EDA数字系统设计与VHDL课程大作业

题目一:数字频率计设计(平台实现)★

(1) 能对输入的方波信号频率进行采样;

(2) 采样频率范围为0~5999999Hz,以1Hz为单位进行显示;

(3) 采用七个七段数码管显示当前采样的频率值,如采样频率值为500HZ,则只显示500,而不显示0000500(即前面4个0不显示);

(4)本电路系统板输入时钟为6MHz。

完整数字系统设计代码及其报告下载:EDA源码报告点这里

VHDL部分代码:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-zKapu3t4-1639400535895)(C:/Users/Lenovo/AppData/Local/Temp/ksohtml/wpsEF83.tmp.jpg)]](https://img-blog.csdnimg.cn/ccf375620354436f8888dbd37d3b52dc.png?x-oss-process=image/watermark,type_d3F5LXplbmhlaQ,shadow_50,text_Q1NETiBA6ZmI6ZmI5LiN5Lya5pWy5Luj56CB,size_18,color_FFFFFF,t_70,g_se,x_16)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-Qpqm96NB-1639400642158)(C:/Users/Lenovo/AppData/Local/Temp/ksohtml/wpsEF84.tmp.jpg)]](https://img-blog.csdnimg.cn/2b2b99d74b8d424fa318dc9eddc0b5fa.png?x-oss-process=image/watermark,type_d3F5LXplbmhlaQ,shadow_50,text_Q1NETiBA6ZmI6ZmI5LiN5Lya5pWy5Luj56CB,size_17,color_FFFFFF,t_70,g_se,x_16)

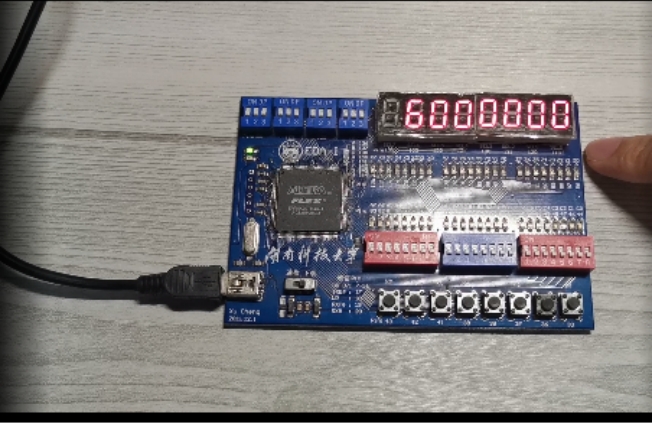

实验测试图:

完整数字系统设计代码及其报告下载:EDA源码报告点这里

2766

2766

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?