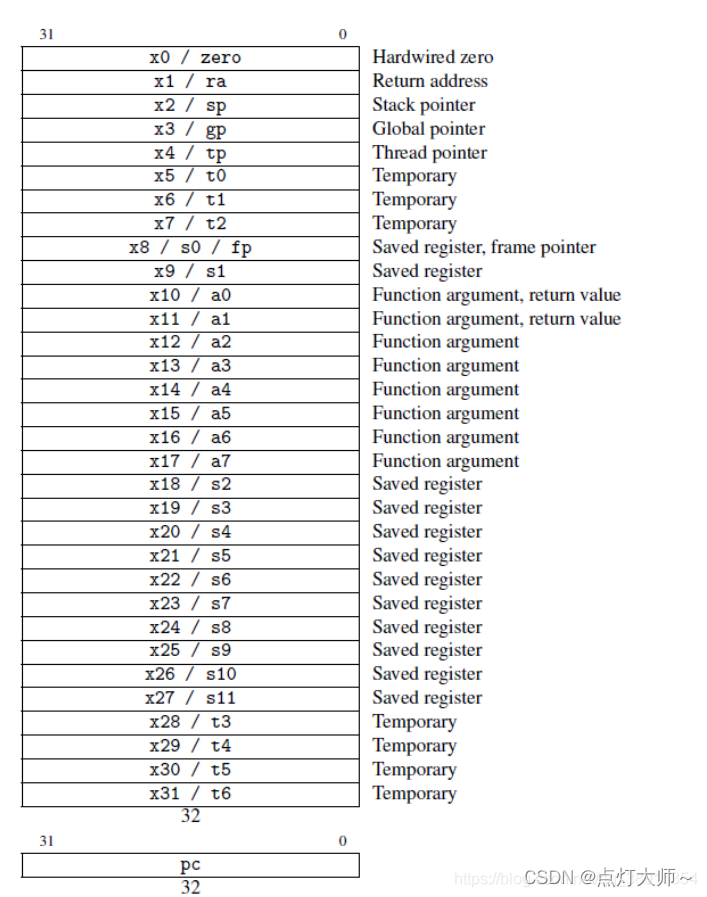

1、寄存器

RV32I有32个通用寄存器,以及一个PC寄存器。其中有一个通过硬件设置的值恒为 0 的 x0 寄存器

注:RISC-V的32个寄存器x0~x31是用0~31这些数字来表示。

2、基础指令

RISC-V有六种基本指令格式:

每个字段名称的含义:

- opcode(操作码):指令的基本操作,这个缩写是它惯用名称。

- rd: 目的操作寄存器,用来存放操作结果。

- funct3: 一个另外的操作码字段。

- rs1: 第一个源操作数寄存器。

- rs2: 第二个源操作数寄存器。

- funct7: 一个另外的操作码字段。

- imm:立即数

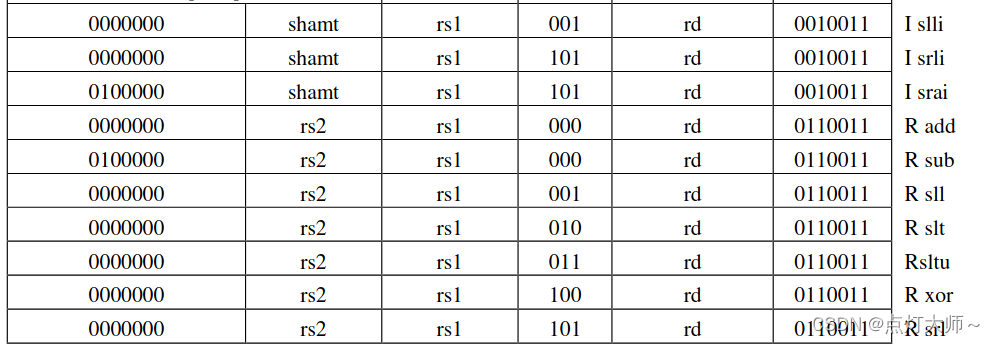

2.1、R 型指令

字段:

| funct7 | rs2 | rs1 | funct3 | rd | opcode |

|---|---|---|---|---|---|

| 7位 | 5位 | 5位 | 3位 | 5位 | 7位 |

指令:

示例:

add a0, a1, a2 //a0 = a1 + a2

sub a0, a1, a2 //a0 = a1 - a2

sll a0, a1, a2 //a0 = a1 << a2(低位补0)

srl a0, a1, a2 //a0 = a1 >> a2(高位补0)

sra a0, a1, a2 //a0 = a1 >> a2 (算术右移,高位补原来的符号位)

slt a0, a1, a2 //a1 < a2 ? a0 = 1 : a0

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6406

6406

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?