参考实验书目:《数字设计和计算机体系结构》机械工业出版社,7章

实验平台:vivado

语言:system verilog

一、实验信息

略...咱的专业课实验报告

二、实验内容

(一)设计原理及实验方案

总体设计思路:

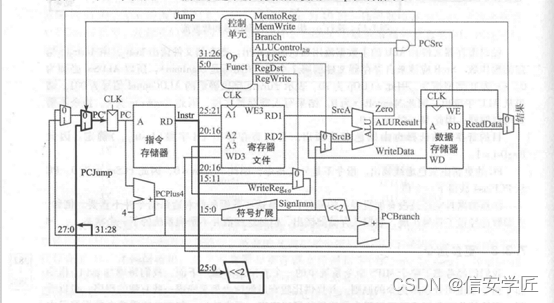

将微体系结构分为两个部分:数据路径和控制。数据路径对数据字进行操作。控制单元从数据路径接收当前指令,并控制数据路径如何执行指令。前者包含存储器,寄存器,ALU和复用器等结构,本次实验设计32位的处理器,因此应采用32位数据路径。后者根据指令需求产生各种使能信号来控制寄存器写,存储器写,复用器数据选择等功能。

设计+实验流程:

1.基础部分(只涉及到教材所提及的指令)

- 确定MIPS处理器的状态元件,再基于当前状态在状态元件之间增加组合逻辑计算新的状态。在本次实验中,共涉及到4个状态元件:

- 1)程序计数器:输入计算的新的PC,输出为当前PC,每个PC指向对应的指令。

- 2)寄存器文件:以instr的rs,rt字段(如果有的话)为地址,读数据;写入数据。

- 3)指令存储器:输入PC取指令instr。

- 4)数据存储器:以ALU的计算结果为地值取数据或者存数据,lw或者sw,取数据会加载到寄存器,存数据时数据来源于rt字段从寄存器中读取的数据。

- 处理器的动作取决于取出的具体指令。

- 从具体指令出发,构造数据路径连接,逐步引入电路元件,当遇到需要共用数据通路时(如寄存器写入时数据来源,ALU计算时的srcB来源等),增加复用器和选择信号。

- 完成一条指令的数据通路后,逐步泛化,在已完成的数据通路上增加连接,引入复用器和其他元件,完成其他指令的数据路径扩展,当lw,sw,R类型,beq,addi,j指令的数据通路都完成后,所有数据路径板块设计完毕。

- 接着整理电路中引入的使能信号(包括寄存器文件,数据存储器的写信号,各个复用器的选择信号,ALU模块执行运算的选择信号),开始完善控制板块。

- 因为指令的不同导致处理器的动作不同,故指令为控制单元的输入信号。本实验中指令的高6位Opcode以及低6位Funct决定指令的功能类型,因此决定各信号的值。在控制单元的设计中,将其分为主译码器和ALU译码器,Opcode作为主译码器的输入信号,计算大部分控制信号,如memtoreg, memwrite, branch, alusrc, regdst, regwrite, jump等,同时产生一个信号aluop(位数取决于指令数,在基础部分时该信号为2位,扩展andi,ori,bne指令后,该信号扩展成3位),该信号与Funct信号一起输入ALU译码器,决定alucontrol的值,控制alu模块的运算类型。

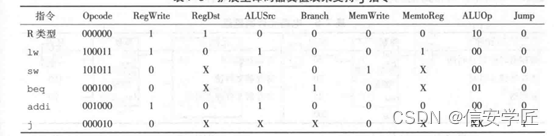

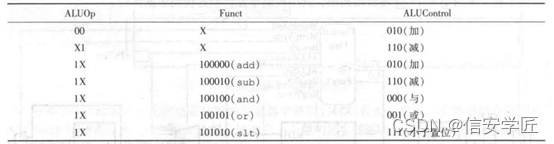

- 根据以上分析做出主译码器和ALU译码器的真值表。

主译码器真值表:

ALU译码器真值表:

- 结合上述流程中做出的最终原理图和完成的两个译码器的真值表,编写system verilog代码,并加入仿真测试文件testbench.sv以及指令文件memfile.txt做仿真测试,观察仿真结果。

基础部分处理器原理图:

2.扩展部分(增加andi,ori,bne指令)

- 在基础部分设计的的CPU基础上,从指令出发,根据增加的指令,扩展数据通路,增加需要的元件和信号。

- 扩展指令功能分析:bne: 条件跳转指令,与beq跳转条件相反,若指令instr的rs字段在寄存器中读取的数据和rt字段读取的数据不相等(Zero为两信号是否相等的标志,zero==1表示读取数据相等,0表示不等),则PC’=(PC)+4+(4*符号扩展后的立即数(即偏移量)。andi:将rs字段对应数据与经过零扩展的立即数做逻辑与运算,得到的值储存到rt指向的寄存器里。ori(或运算),xori(异或运算)的功能类似。

- 扩展指令的具体实现:

- bne部分,考虑增加一个复用器,复用器选择信号zeroselect,当zeroselect值为1时选择输入zero,表示prcsrc=branch&zero,进行beq条件判断;当zeroselect值为0时,选择输入(~zero),表示prcsrc=branch&~zero,进行bne条件判断。zero值为1表示指令取出的两个数据值相等,zero值为0则表示不相等。

- andi部分,需要增加一个复用器,复用器选择信号immselect来选择signimm或者zeroimm,值为1表示选择符号扩展立即数进入接下来alusrc的选择,值为0表示选择零扩展立即数进入接下来alusrc的选择。考虑到此复用器关系到进入ALU运算的srcB的来源(rt字段取数or符号扩展立即数or零扩展立即数),所以alusrc==1(选择立即数作为srcb)的指令,需要明确给出immselect的值,如lw,sw,addi等,immselect=1;而andi,ori指令对应的immselect==0。

- ori部分,因为已经在扩展andi指令时完成了数据路径的扩展,所以只需在addi的基础上,将对应真值表中aluop定为100,使srca和srcb在ALU模块里的运算变成按位或。

- 整理新增控制信号,扩展主译码器和ALU译码器真值表。因为扩展指令后需要的aluop数超过4(加,减,与,或,R类),所以aluop变量更改为三位向量。扩展后的两真值表如下图所示。

主译码器真值表:

| 指令 |

opcode |

regwrite |

regdst |

alusrc |

branch |

memwrite |

memtoreg |

aluop |

jump |

zeroselect |

immselect |

| R类 |

本文详细介绍了32位MIPS单周期CPU的设计过程,从基础部分的处理器设计,到扩展部分增加andi,ori,bne指令,再到增加I/O接口准备上板部分。实验涉及数据路径、控制单元、复用器、真值表、system verilog代码编写和仿真测试。通过逐步扩展和优化,实现了处理器的多种功能,并进行了上板验证。

本文详细介绍了32位MIPS单周期CPU的设计过程,从基础部分的处理器设计,到扩展部分增加andi,ori,bne指令,再到增加I/O接口准备上板部分。实验涉及数据路径、控制单元、复用器、真值表、system verilog代码编写和仿真测试。通过逐步扩展和优化,实现了处理器的多种功能,并进行了上板验证。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2189

2189

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?