第一章 绪论

1.1 数字信号与数字电路

一、模拟量/模拟信号/数字量/数字电路

- 模拟量:在时间和数量上连续变化的物理量

- 模拟信号:表示模拟量的信号

- 数字量:在时间和数量上不连续变化的物理量

- 数字信号:表示数字量的信号

二、数字电路的表示方法

1.2 数制和码制

一、数制基础概念

- 数制:① 每一位的构成方法 ② 从低位到高位的进位规则

- 权展开式:

二、重要的数制

- 十进制:

数码:0~9

基数:10

规律:十进一 - 二进制:

数码:0、1

基数:2

规律:二进一 - 八进制:

数码:0~7

基数:8

规律:八进一 - 十六进制:

数码:0~9 A~F

基数:16

规律:十六进一

三、不同数制之间的转换(考点)

-

任意转十

-

十转任意

整数:连除取余,除到0

小数:连乘取整(默认4位)

-

二转八

小数点为中心,三位合一位,两头不足三位补0

-

八转二

小数点为中心,一位分三位,两头多余0去掉

-

二转十六 / 十六转二

与二转八同理,但四位合一位 -

八转十六

方法1⃣️:先 八转二 后 二转十六

方法2⃣️:先 八转十 后 十转十六

四、码制的基础概念

- 编码:以0,1作为基本码元,按照一定的规则构成一系列代码,用来表示文字、符号或者十进制数字。

- 译码:编码逆过程。

- 码制:编码所遵循的规则。

五、常用编码(考点)

- 自然二进制:二进制数

- bcd码:用 4位二进制代码 表示 1位十进制数

- 8421bcd码:一种恒权码

⚠️注意:

① 两头的0不能删,要确保有4位二进制数!

② 8421bcd码不能直接转换成2,8,16进制,需要先转成10进制后才行

- 余3码:是一种变权码

余3码= 8421bcd + 0011

- 2421bcd:恒权码

- 5211bcd:恒权码

- 格雷码(循环码):

-

如何写出格雷码

-

特点:

- ASII码

第二章 逻辑代数基础

2.1 基础概念

- 逻辑变量:取值只有0、1两种变量。无大小之分。

- 逻辑函数:若变量A、B、C变量取值确定后,可以唯一确定D的取值,那么D变量为ABC变量的逻辑函数。

2.2 基本逻辑运算

一、与

-

逻辑电路:

-

真值表:

-

逻辑式: Y = A ⋅ B = A B Y=A·B=AB Y=A⋅B=AB

-

逻辑运算:(0优先)

5.逻辑符号:

二、或

-

逻辑电路:

-

真值表:

-

逻辑式: Y = A + B Y=A+B Y=A+B

-

运算规则:(1优先)

-

逻辑符号:

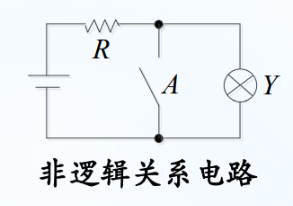

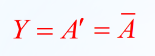

三、非

-

逻辑电路:

-

真值表:

-

逻辑式:

-

运算规则:

-

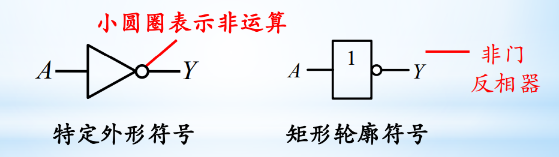

逻辑符号:

2.3 复合逻辑运算

一、与非

二、或非

三、与或非

四、异或/同或

2.4 逻辑函数的表示

一、表示方法

- 逻辑赋值

- 真值表

- 逻辑表达式

- 逻辑图

- 波形图:

- 卡诺图

二、方法之间的转换(考点)

- 逻辑式 -> 真值表:写出变量的每一种状态(0、1)

- 真值表 -> 逻辑式:

① 找Y=1的一列,将变量写成×的形式

② 若变量A为0,则在×的形式中写成A`;若变量A为1,还写成A

③ 将这些式子相加

- 逻辑式 -> 逻辑图

- 逻辑图 -> 逻辑式

- 波形图-> 真值表

- 逻辑式 -> 卡诺图

逻辑式 -> 真值表 -> 卡诺图

2.5 基本公式和常用公式

一、基本公式

二、常用公式(考点)

三、证明方法

-

真值表:

-

已有公式证明:

四、逻辑代数基本定理(考点)

- 代入定理:

- 反演定理:

- 对偶定理:

- 逻辑式相等可以推出对偶式相等

五、逻辑函数的化简(考点)

-

标准:

-

化简题目:

2.6 卡诺图

一、最小项基础

- 最小项:n个变量乘积项满足:① 每个变量都出现 ② 每个变量的正反形式只出现一次

① n个变量最小项有: 2 n 2^n 2n个 - 最小项表示方法:

- 最小项性质:

① 所有最小项之和为:1

② 任意两个最小项之积为:0

③ 相邻两个最小项之和可以合成一项,消去某对因子

④ 任何式子都可以展开成某些最小项之和的形式(最小项表达式)

- 求最小项表达式(考点)

- 代数法:A+A’=1代入缺A项;缺啥补啥

- 真值表:Y=Σ 函数值为1的项 | Y‘=Σ 函数值为0的项

- 用卡诺图表示最小项:

二、用卡诺图表示逻辑函数(⭐)

- 逻辑函数 --> 卡诺图:

方式一:最小项法:

思路:

① 将逻辑函数 —> 最小项表达式

② 将0、1填入卡诺图对应的位置

方式二:真值表法:

方式三:直填法

- 卡诺图 — > 逻辑函数(很简单略)

三、卡诺图化简逻辑函数(⭐)

- 合并最小项原则:

2个相邻 --> 消1个变量

4个相邻 --> 消2个变量

8个相邻 --> 消3个变量

判断消去哪个变量:看分别看行+列,若相同 —> 保留 ;不同0、1 —> 丢掉

- 思路

① 将逻辑函数化为卡诺图

② 画圈

- 8,4,2,1 (优先级依次降低)(满足圈大圈少)

- 圈与圈可相交

- 一个圈内乘,一个图圈圈加

- 圈1得原函数的最简式; 圈0得反函数得最简式,也适用于0的数目远小于1的数目 、将函数化为最简或与、或非-或非、与或非式

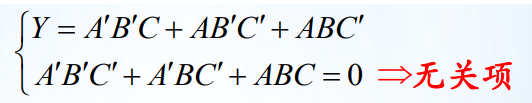

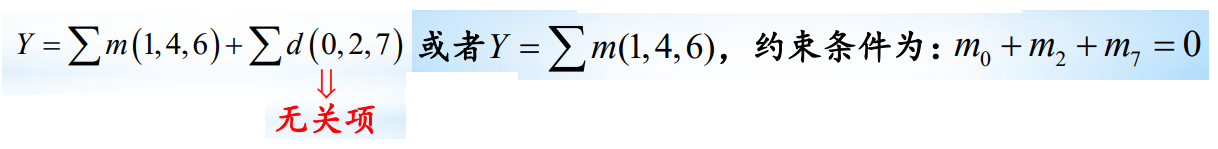

四、具有无关项的逻辑函数的化简(⭐)

- 无关项:任意项 + 约束项 = 无关项

任意项和约束项不管取0,1都是不影响结果的项 - 无关项的表示:

- 用逻辑式表示:

- 用最小项表示:

- 真值表和卡诺图

- 用逻辑式表示:

- 逻辑式有无关项的逻辑函数的化简

- 公式化简(不直观不推荐)

- 卡诺图化简:

有利于化简的×看成1

不利于化简得×看成0

第三章 门电路

3.1 基础概念

- 门电路:用以实现基本逻辑运算和复合逻辑运算的单元电路

- 门电路的分类:

- 正负逻辑:无特殊说明,默认为正逻辑

- 获得低/高电平的方法:

3.2 基础门电路

一、二极管

- 二极管基础:

- 二极管与门:

- 二极管或门:

- 二极管门电路特点

- 电路构造简单

- 成本低

- 存在点评偏移现象:若有多个二极管门点电路,规定的0/1不唯一,会发生逻辑错误

二、三极管

- 三极管基础

- 三极管反相器

3.3 TTL门电路

一、TTL门重点(⭐)

-

电路结构:

-

工作原理:

-

电压传输特性:

-

几个参数:

-

输入端噪声容限

-

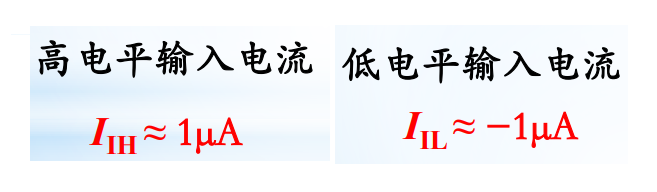

静态输入/输出特性:

-

扇出系数:

-

输入端负载特性:

TTL的输入端

- 动态特性

- TTL门电路多余输入端的处理

二、其他类型的TTL门电路

- TTL与非门

三、OC门

- 电路结构

- OC门的并联

四、三态输出门电路(TS门)

三态:L(低电平)、H(高电平)、Z(高阻态)

- 电路结构

- 工作原理

3.4 CMOS门电路

一、CMOS门电路重点

-

MOS管构造:

-

MOS管开关特性:

-

CMOS电路结构:

-

CMOS工作原理:

-

输入伏安特性

-

输入端负载特性:

对于CMOS门电路输入端

- CMOS门多余输入端处理

二、其他类型的CMOS门

- 与非门

- 或非门

三、OD门(漏极开路输出门电路)

四、TS门(三态输出门电路)

五、CMOS传输门

- 电路结构:

- 工作原理

第四章 组合逻辑电路

4.1 基础概念

- 组合逻辑电路特点:无存储单元

一、组合逻辑电路的分析

组合逻辑电路分析:

逻辑电路——>逻辑式——>逻辑式化简——>真值表——>逻辑功能

二、组合逻辑电路设计

问题——> 真值表——>逻辑式——> 逻辑式化简 ——>逻辑电路

4.2 若干常用的组合逻辑电路

4.2.1编码器

一、普通编码器

- 普通编码器准则:任何时刻只允许输入一个有效编码信号

- 二进制编码器:

- 二进制编码器原理(以8-3线为例)

- 二十进制编码器:

将0—9十种状态用8421BCD码进行表示

- 二十进制编码器特征

二、优先编码器

- 优先编码器准则:克服了普通编码器只能输入一个高电平的缺点,设计了几个信号同时输入时,

电路只对其中优先级别最高的进行编码 - 二进制优先编码器(以8-3线74LS/HC148):

- 二十进制优先编码器

4.2.2 译码器

一、二进制译码器

- 规则:对应输入的每一组二进制代码,有且仅有一个输出端为有效电平

- 原理(以3-8线编码器为例)

- 集成3/8线译码器74HC138

988

988

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?