第一章 开关理论基础

第一节 数字与模拟

离散与连续的对比

数量、空间、事物

连续量又称模拟量,离散量又称数字量

开关量:二状态系统,两个数字状态可以用1和0来表示,亦称比特(bit)

二进制系统

逢2进位的进位制。0,1是基本算符

使用低电平来表达0,高电平来表达1

对于电位型,无需归零,但脉冲型需要归零

周期化波形的参数化描述

脉冲周期T,单位是秒s

脉冲频率f,单位是赫兹HZ

频宽比D,脉冲宽度和脉冲周期之比的百分数占空系数 t w T ∗ 100 \frac{t_w}{T}*100 Ttw∗100%

脉冲分类:正脉冲和负脉冲

正脉冲是脉冲的上升沿,负脉冲是脉冲的下降沿

区分方法:时钟沿CLK的接入是否存在非门,存在即为负脉冲,否则为正脉冲

在非理想状态下,脉冲波形并不是严格的瞬间变换,而是存在高低电平转化之间的过程,这个过程需要时间。

第二节 数制与码制

位权表示法:

( N ) R = K n − 1 R n − 1 + K n − 2 R n − 2 + . . . + K 1 R 1 + K 0 R 0 + K − 1 R − 1 + . . . + K − m R − m (N)_R = K_{n-1}R^{n-1}+K_{n-2}R^{n-2}+...+K_1R^1+K_0R^0+K_{-1}R^{-1}+...+K_{-m}R^{-m} (N)R=Kn−1Rn−1+Kn−2Rn−2+...+K1R1+K0R0+K−1R−1+...+K−mR−m

常用的进制有:

十进制(Decimal notation)

八进制(Octal notation)

二进制(Binary notation)

十六进制(Hexadecimal notation)

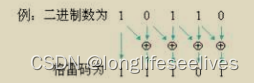

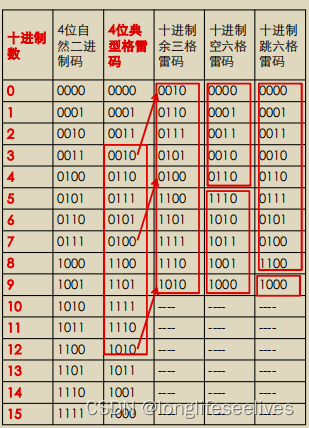

格雷码

格雷码属于可靠性编码,是一种错误最小化的编码方式,避免尖峰电流脉冲

编码方式:最高位保留,其他各位做异或运算

解码方式,同编码方式

其他形式的格雷码

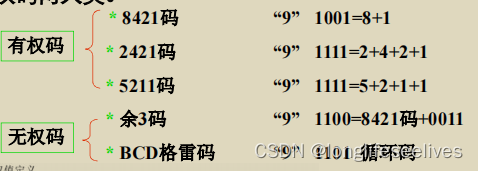

编码方案分为有权码和无权码

原码的表示:最高位为符号位,其余位为数值位

反码的表示:正数的反码是它本身,负数的反码可将原码中的符号位保持不变,数值位的每一位1改为0,0改为1即可

补码的表示:正数的补码是它本身,负数的补码等于它的反码加1

第三节 逻辑函数及其描述

逻辑函数的描述工具:六种方法

布尔代数法:按一定逻辑规律进行运算的代数。与普通代数不同,布尔代数中的变量是二元值的逻辑变量。

真值表法:采用一种表格来表示逻辑函数的运算关系,其中输入部分列出输入逻辑变量的所有可能组合,输出部分给出相应的输出逻辑变量值。

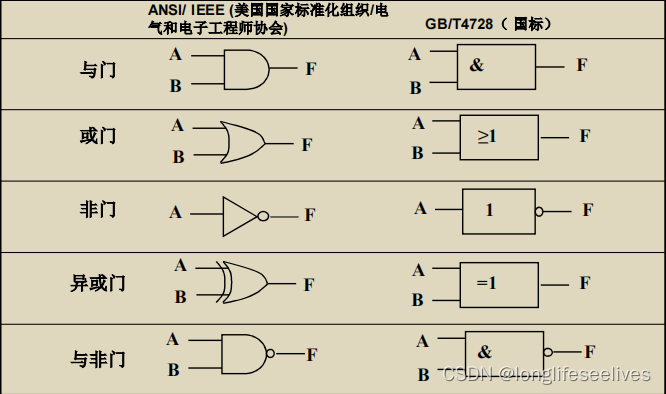

逻辑图法:采用规定的图形符号,来构成逻辑函数运算关系的网络图形。

卡诺图法:卡诺图是一种几何图形,可以用来表示和简化逻辑函数表达式。

波形图法:一种表示输入输出变量动态变化的图形,反映了函数值随时间变化的规律。

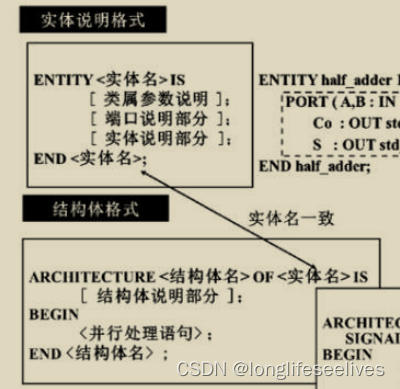

硬件设计语言法:是采用计算机高级语言来描述逻辑函数并进行逻辑设计的一种方法,它应用于可编程逻辑器件中。目前采用最广泛的硬件设计语言有Verilog、 VHDL等。

基本逻辑运算

与运算: F = A B C F=ABC F=ABC

或运算: F = A + B + C F=A+B+C F=A+B+C

非运算: F = A ‾ F=\overline{A} F=A

与非运算: F = A B C ‾ F=\overline{ABC} F=ABC

或非运算: F = A + B + C ‾ F=\overline{A+B+C} F=A+B+C

异或运算: F = A ⊕ B = A ‾ B + A B ‾ F=A\oplus B=\overline{A}B+A\overline{B} F=A⊕B=AB+AB

同或运算: F = A ⊙ B = A B + A ‾ ∗ B ‾ F=A\odot B=AB+\overline{A}* \overline{B} F=A⊙B=AB+A∗B

逻辑运算的表达

正逻辑:TTL电平

高电平赋为1,低电平赋为0

负逻辑:标准串行接口RS232

高电平赋为0,低电平赋为1

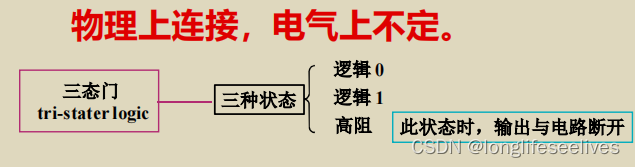

三态门

指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路。

高阻态相当于隔断状态。 三态门都有一个EN控制使能端,来控制门电路的通断。

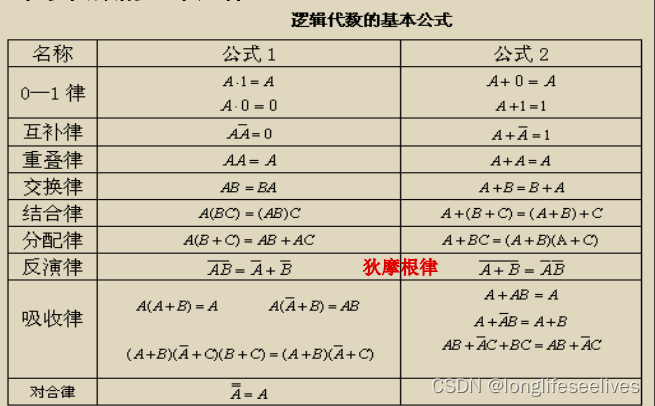

第四节 布尔代数

布尔代数的基本定律

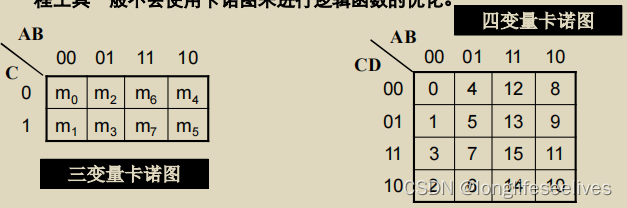

第五节 卡诺图

逻辑函数最小项:

设有n个变量,它们所组成的具有n个变量的“与”项中,每个变量或者以原变量或者以反变量(非变量)的形式出现一次,且仅出现一次,这个乘积项称为最小项。

n格变量具有 2 n 2^n 2n个最小项。

任何一个逻辑函数可以写成一组最小项之或

卡诺图

是一种描述逻辑函数的特殊方法,将n变量的全部最小项各用一个小方格表示,并按循环码排列变量取值组合,使几何相邻的小方格具有逻辑相邻性。

卡诺图是真值表的变形,超过四个变量一般不用这种方法表示

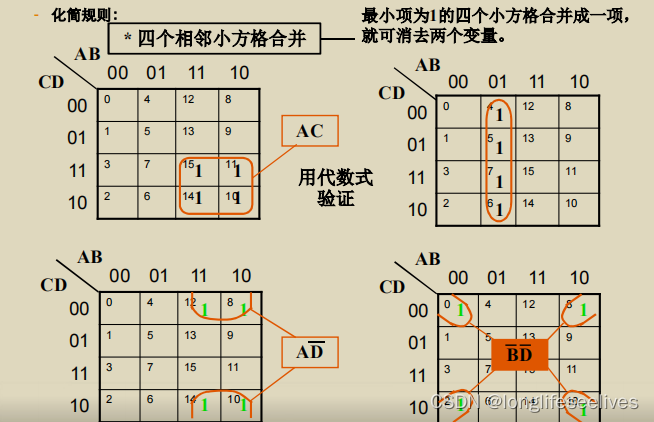

使用卡诺图化简逻辑函数

化简规则:两个或四个或八个相邻小方格合并

第二章 组合逻辑

第一节 组合逻辑分析

组合逻辑特点:

电路任意时刻的输出状态只取决于该时刻的输入状态,而与该时刻前的电路输入状态无关。

74LS00:四个2输入与非门

74LS10:三3输入与非门

74LS86:TTL2输入端四异或门

组合逻辑中的竞争冒险

产生原因:

实际逻辑电路中,信号经过同一电路中的不同路径所产生的时延不同。时延的长短与信号经过的门数、具体逻辑门的时延大小和导线的长短有关。

竞争:

输入信号经过不同路径到达输出端的时间有先有后,这样的现象就叫竞争。

非临界竞争:不产生错误输出的竞争。

临界竞争:导致错误输出的竞争。

冒险:

电路中竞争的存在,使得输入信号的变化可能引起输出信号出现非预期的错误输出现象,也称为冒险。组合电路中的冒险是一种瞬态现象,表现为在输出产生不应有的尖脉冲(毛刺),暂时破坏正常逻辑关系。瞬态结束即可恢复正常逻辑关系。

冒险的判断:

当某个变量A 同时以原变量和反变量的形式

出现,且在一定条件下表达式可简化成 A + A ‾ A+\overline{A} A+A或 A A ‾ A\overline{A} AA形式时,则A 的变化可能由于竞争而产生冒险。

代数法:通过对其他变量赋初值,化简逻辑表达式直至出现上述形式,即可判断是否可能产生险象。

卡诺图法:

步骤:1、做出函数的卡诺图。

2、画出与项对应的卡诺圈。

3、找出存在“相切”关系的卡诺圈(即两个卡诺圈间存在不被同一卡诺圈包含的相邻最小项)。

如何消除竞争冒险现象:

加选通脉冲:在接收了输入信号并且电路达到了新的稳态之后,才加入选通脉冲。

修改逻辑设计

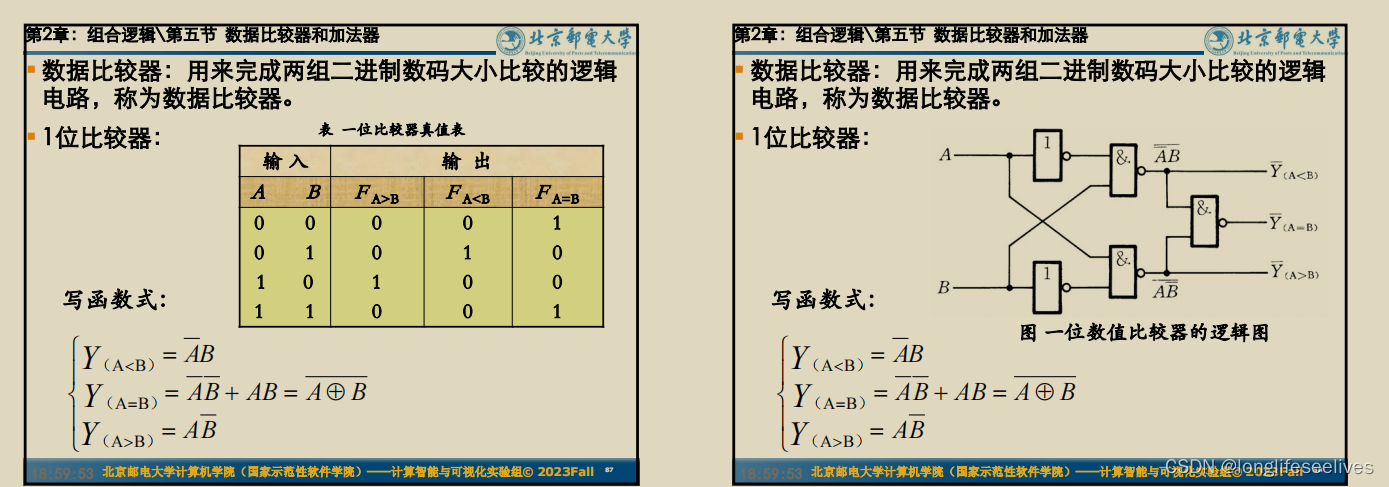

第二节 组合逻辑设计

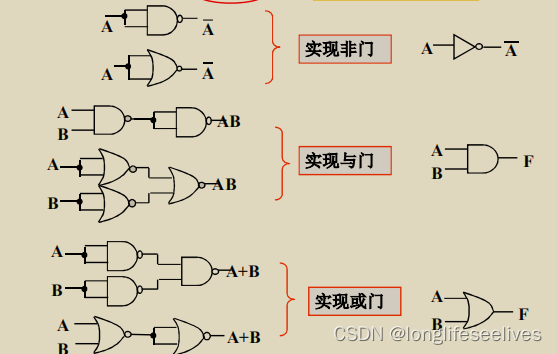

逻辑函数的门实现:一个逻辑函数可以用不同形式的逻辑函数来实现

与非门和或非门

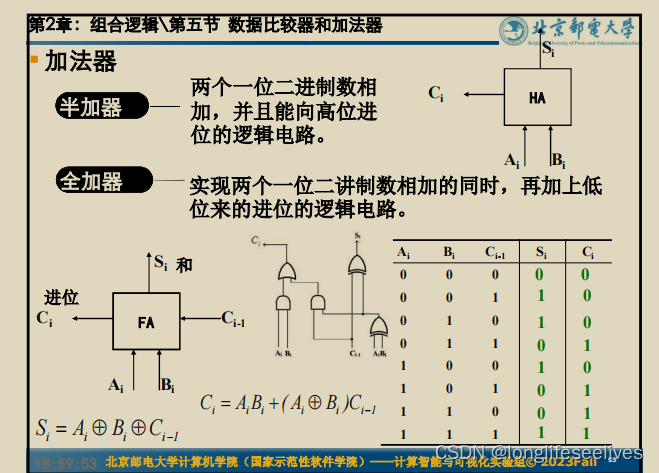

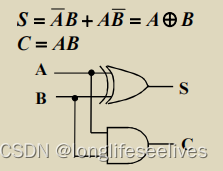

半加器

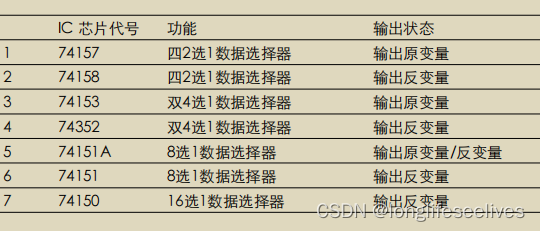

第三节 数据选择器与分配器

数据选择器MUX,又称:多路转换器 多路开关。是多路输入、单路输出的组合逻辑构件。是一种可以从多个输入信号中选择一个信号进行输出的器件。

74LS153:2个四选一多路开关

74LS151:8选一数据选择器

74LS155:1-4线数据分配器/2:4线译码器

第四节 译码器和编码器

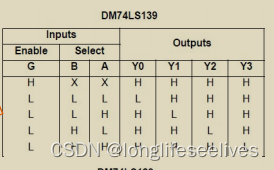

译码器

实现译码功能的组合逻辑电路称为译码器.

输入是一组二进制代码,输出是一组高低电平信号

对于每输入一组不同的代码:只有一个输出呈现有效状态,其他都无效,可实现按照编码选择

应用:地址译码器

二进制译码器

74LS139:2:4译码器

74LS138:3:8译码器

74LS154:4:16译码器

第三章 时序逻辑

时序电路: t 时刻输出Y不仅与t时刻输入X有关,还与电路过去的状态Qn有关。

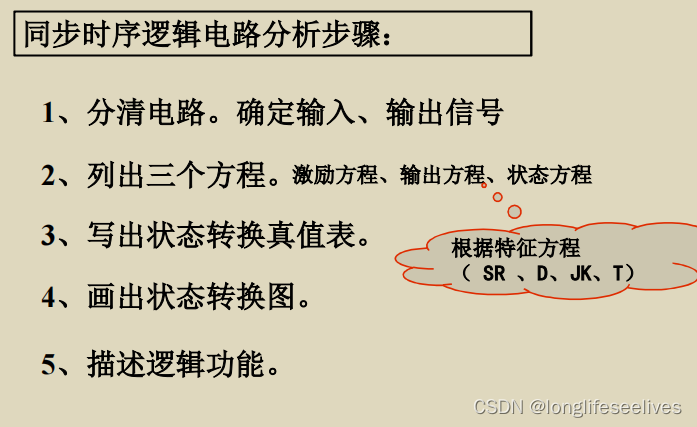

分析图示电路的逻辑功能方法

- 写出驱动方程

- 写出状态转移方程

- 写出输出方程

- 列出转移状态表、画出转移图

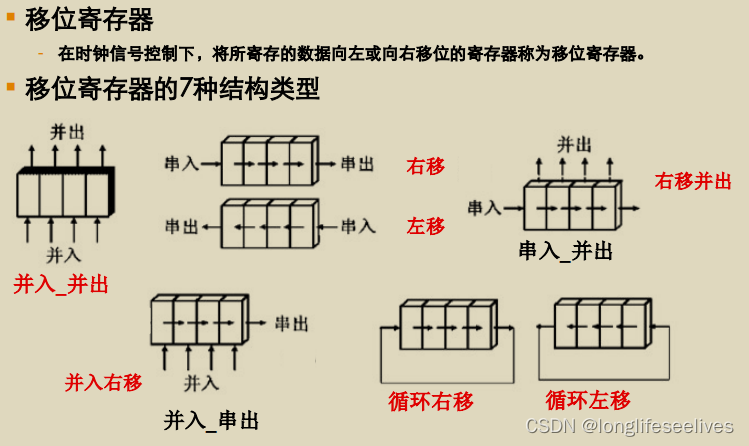

在时钟信号控制下,将所寄存的数据向左或向右移位的寄存器称为移位寄存器。

通用移位寄存器74LS299

四种功能功能:置数、左移、右移、保持

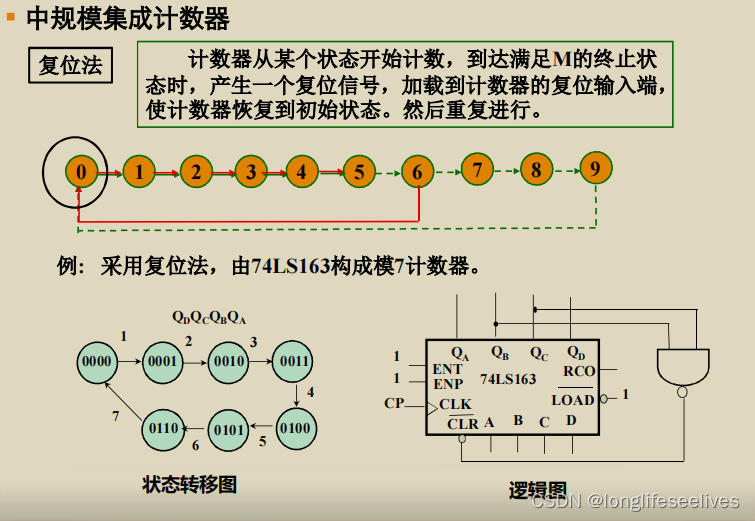

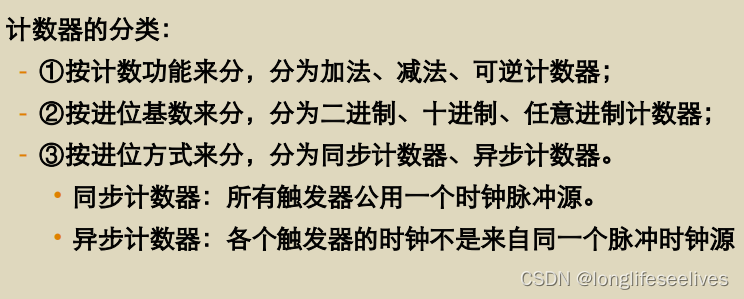

计数器:记忆脉冲的个数的时序逻辑电路

计数器所能记忆脉冲的最大数目称为该计数器的模。

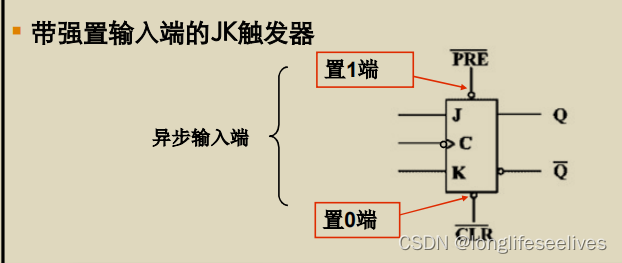

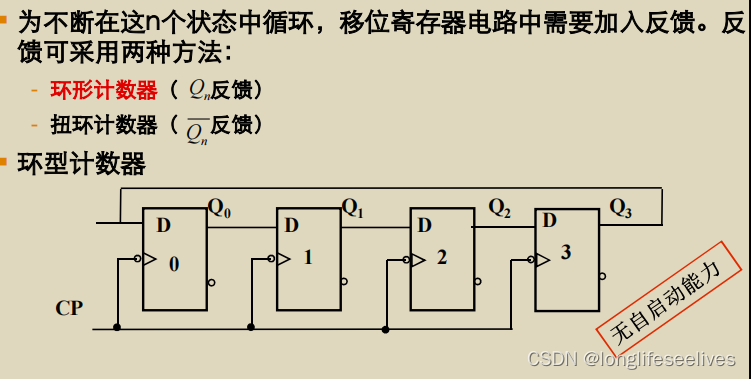

核心元件是触发器

计数器自启动:

在有效循环中的为有效状态,否则为无效状态

无效状态在CP脉冲作用下能够进入有效循环,说明该电路能够自启动。

无效状态在CP作用下不能进入有效循环,则表明电路不能自启动。

分析计数器步骤:

- 写出输出方程和激励方程

- 写出电路的状态方程

- 作状态转移表和状态图

- 分析说明

环型计数器的特点:K个触发器,可计K个数。

扭环计数器的特点:K个触发器,可计2K个数。

异步计数器的分析方法中要把时钟信号作为输入信号来处理。

当实际要求的计数模值超过单片计数值时,采用多片级联。

定时脉冲产生器:

一个数字系统之所以有条不紊的工作,完全是受到定时脉冲的指挥。定时脉冲,也称为节拍脉冲,按固定时间顺序再现的脉冲序列。

时钟脉冲源电路

石英晶体振荡器

节拍脉冲产生器

同步时序逻辑分析

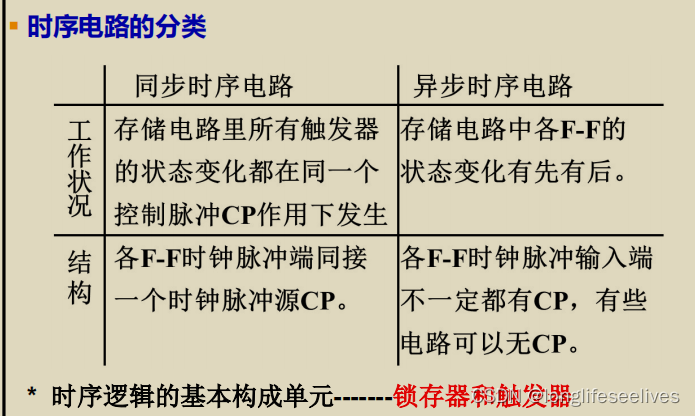

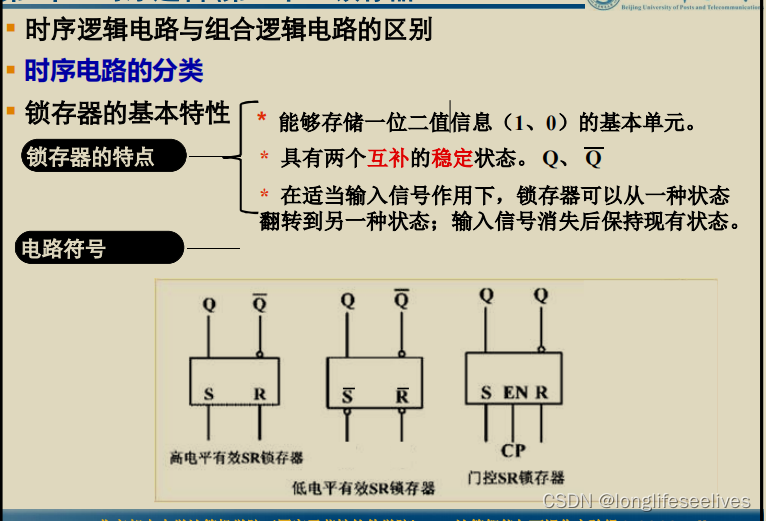

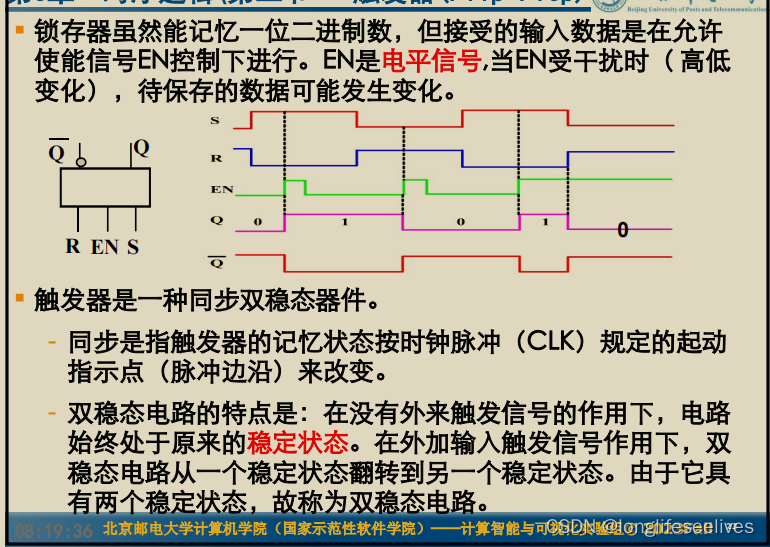

时序电路的分类:

米里型时序电路:输出与输入及状态有关

摩尔型时序电路:输出只与状态有关

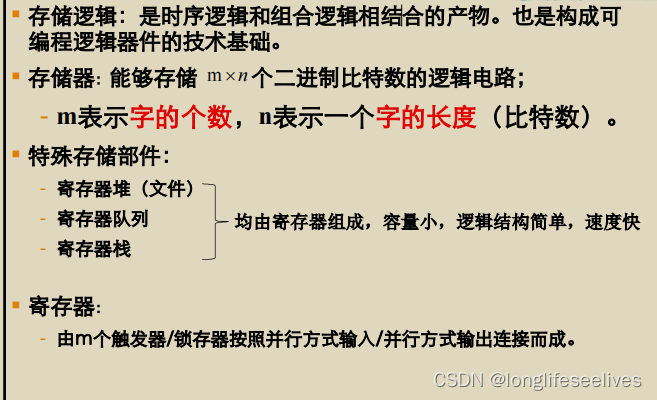

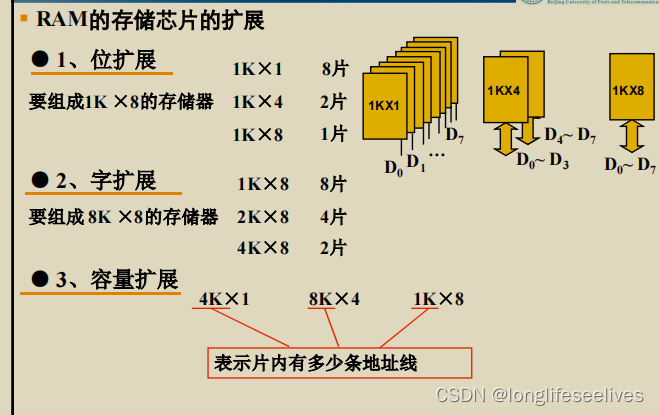

第四章 存储逻辑器件

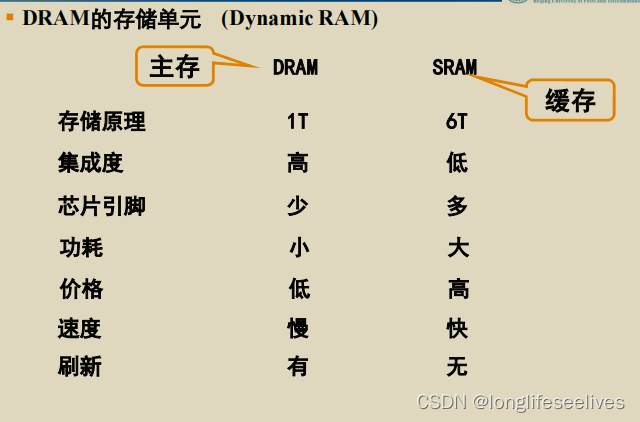

SRAM:静态随机存储器

DRAM:动态随机存储器

DDR:双倍速率同步动态随机存储器

SGRAM:同步图形随机存储器

半导体只读存储器.简称 ROM (Read - only Memory):非易失性存储器

特点:存储固定信息。预先把信息写入到存

储器中,在操作过程中,只能读出信息,不

能写入。

ROM分类:

MROM:掩模式只读存储器

PROM:一次编程的只读存储器

EPROM:多次编程的只读存储器

- 卡诺图上变量的取值顺序是采用循环码的形式,以便能够用几何上相邻关系来表示逻辑上的相邻。

- 在VHDL中,以下不属于并发语句:

过程语句、函数调用语句,case语句- 优先编码器的编码输入信号是相互排斥的,不允许有多个编码信号同时有效。

- 二进制译码器相当于是一个最小项发生器,便于实现组合逻辑电路。

- 在结构体中定义一个全局变量(Variable),可以在所有进程中使用。

VHDL

1555

1555

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?