1. Introduction

TileLink 是一种芯片级互连标准,为多个主设备提供对内存和其他从设备的一致内存映射访问。

TileLink 设计用于片上系统 (SoC),使用可提供低延迟和高吞吐量传输的快速可扩展互连来连接通用多处理器、协处理器、加速器、DMA 引擎以及简单或复杂的设备。

TileLink:是一种自由开放的紧密耦合、低延迟 SoC 总线标准,专为 RISC-V 设计,但支持其他 ISA,提供物理寻址、共享内存系统,可通过可扩展、可分层组合、点对点实现网络为缓存或非缓存主设备的任意组合提供一致的访问,

可以缩小为简单的从设备或扩大为高吞吐量从设备

TileLink 的一些重要功能包括: 高速缓存一致共享内存,支持 MESI 等效项协议可验证任何符合 SoC 的死锁自由 无序完成可提高并发操作的吞吐量 解耦接口,简化寄存器级插入 无状态总线宽度自适应和突发碎片

1.1. Protocol Conformance Levels

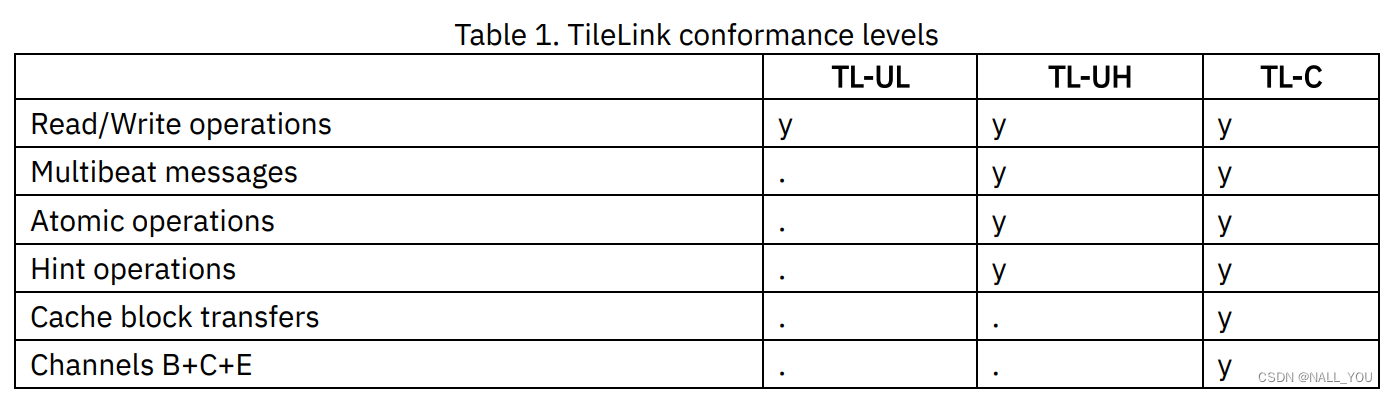

TileLink 网络可以支持混合的通信代理,每个代理都支持协议的不同子集。 TileLink 规范包括附加代理的三个一致性级别,这表明它们必须支持协议的哪个子集,如表 1 所示。最简单的是 TileLink Uncached Lightweight (TL-UL),它仅支持简单的内存读取和写入 (Get/ Put) 单个单词的操作。第二个最复杂的是 TileLink Uncached Heavyweight (TL-UH),它添加了各种提示、原子操作和突发访问,但不支持一致缓存。最后,TileLink Cached (TL-C) 是完整的协议,它支持使用一致性缓存。

当 TL-C 处理器代理与 TL-UL 设备代理通信时,处理器代理应避免使用更高级的功能,或者两者之间的网络中必须有 TL-C 到 TL-UL 适配器。代理可以支持其他功能组合,但本规范仅涵盖列出的三个一致性级别。

当 TL-C 处理器代理与 TL-UL 设备代理通信时,处理器代理应避免使用更高级的功能,或者两者之间的网络中必须有 TL-C 到 TL-UL 适配器。代理可以支持其他功能组合,但本规范仅涵盖列出的三个一致性级别。

1.2. Document Overview

本规范的其余部分分为以下几节:

第 2 节概述了 TileLink 架构及其公共抽象。

第 3 节定义了每个 TileLink 通道所需的特定信号。

第 4 节定义了如何使用这些信号来交换 TileLink 消息。

第 5 节描述了 Tilelink 的无死锁设计,并提供了确保一致性的规则和解释。

第 6 节概述了 TileLink 代理可用的操作,并提供了有关其排序、地址空间使用和事务标识符的指导。

第 7 节详细介绍了用于在 TileLink 上执行基本 get/put 操作的消息。

第 8 节通过突发传输、原子操作和提示扩展了 TileLink。

第 9 节概述了如何在完整的 TileLink 协议中管理缓存数据块。

2. Architecture

TileLink 协议是根据连接代理图来定义的,这些代理通过链接内的点对点通道发送和接收消息,以在共享地址空间上执行操作。

操作 对内存层次结构中地址范围的数据值、权限或位置的更改。

代理 协议中的主动参与者,发送和接收消息以完成操作(更准确的定义将在第 5.1 节中给出)。

通道 主接口和从接口之间承载同质优先级消息的单向通信连接。

消息 通过特定通道发送的一组控制和数据值。

link 两个代理之间完成操作所需的通道集

2.1. Network Topology

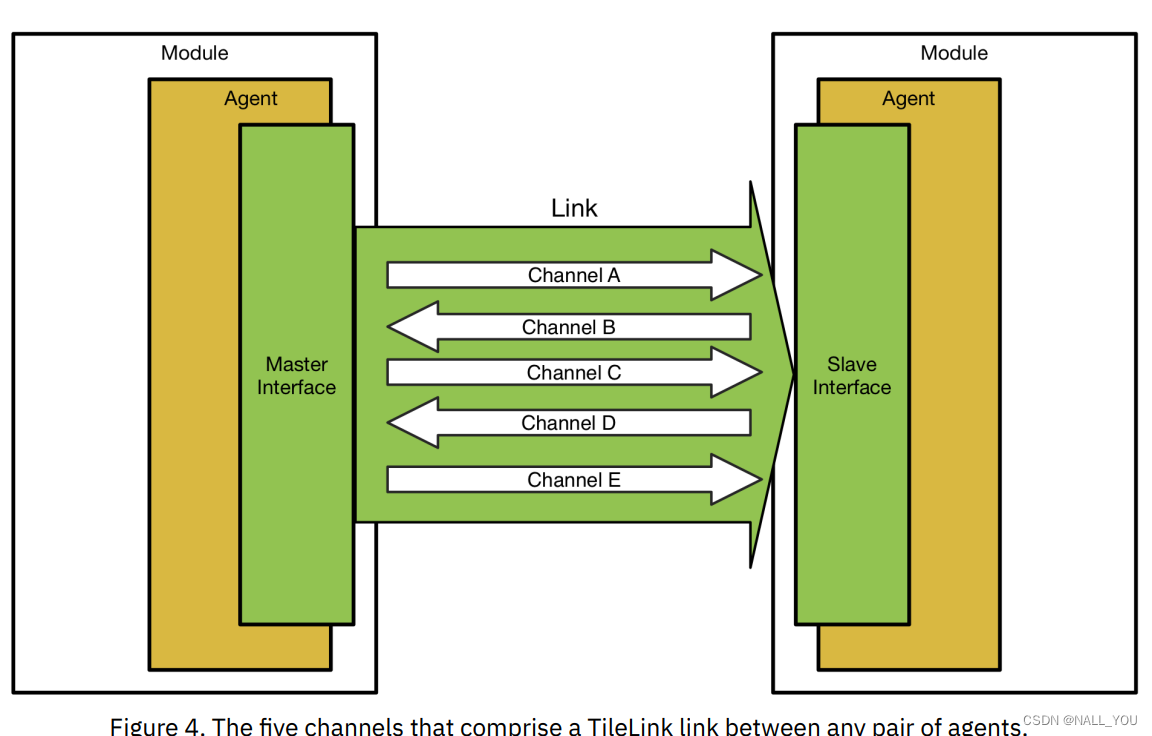

代理对通过链接连接。每条链路的一端连接到一个代理中的主接口,另一端连接到另一个代理中的从接口。具有主接口的代理可以请求具有从接口的代理执行内存操作,或者请求传输和缓存数据副本的许可。具有从接口的代理管理对一系列地址的许可和访问,其中它代表从主接口到达的请求执行存储器操作。

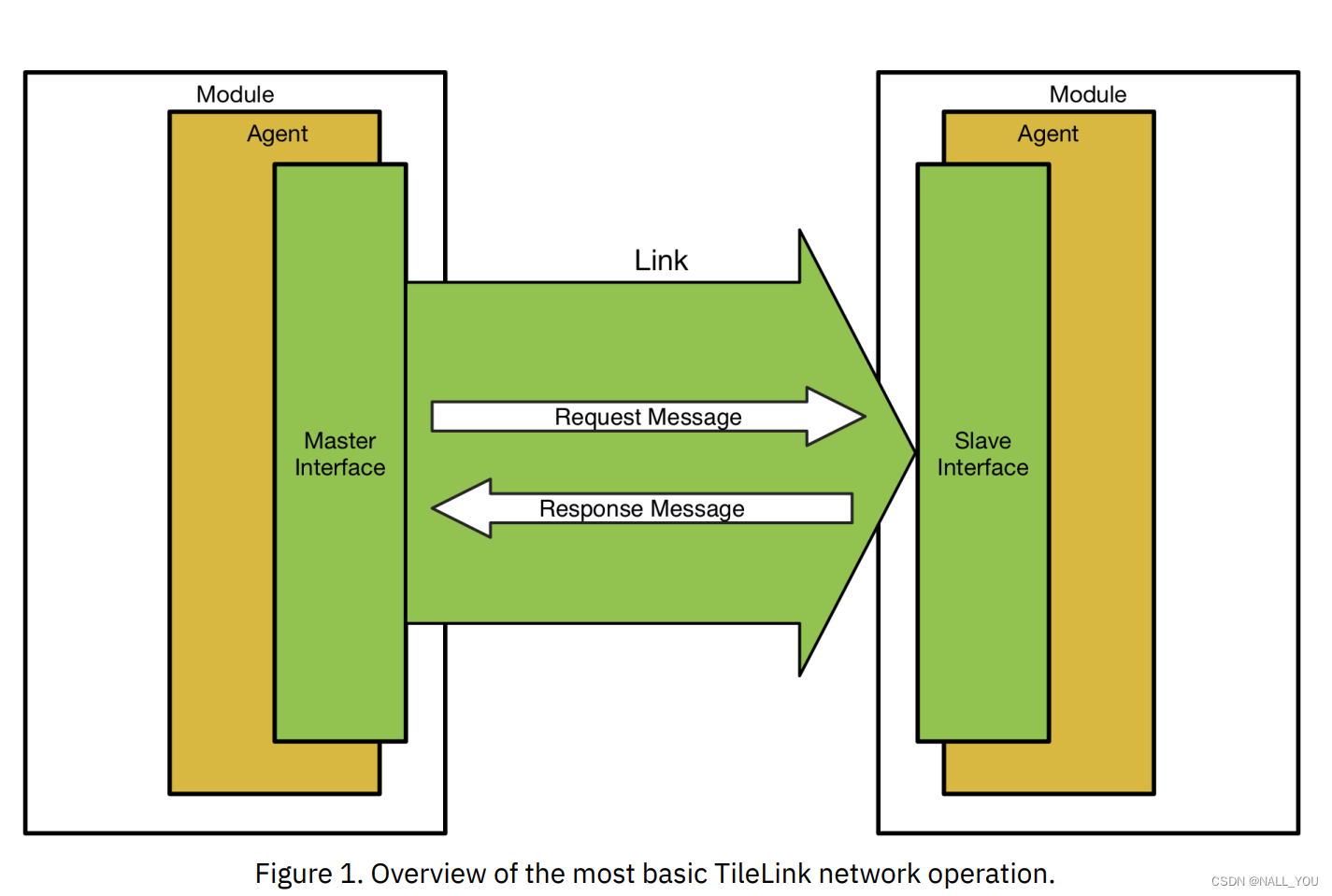

图 1 显示了一个 TileLink 网络,由主接口和从接口之间的单个链路组成,具有两个通道。为了对共享存储器执行操作,主设备在请求通道上向从设备发送请求消息,并在响应通道上等待确认消息。

两个模块通过链路连接,一个模块包含具有主接口的代理,另一个模块包含具有从接口的代理。具有主接口的代理向具有从接口的代理发送请求。如果需要,具有从属接口的代理与后备存储器进行通信。获得所需的数据或权限后,从站响应原始请求者。

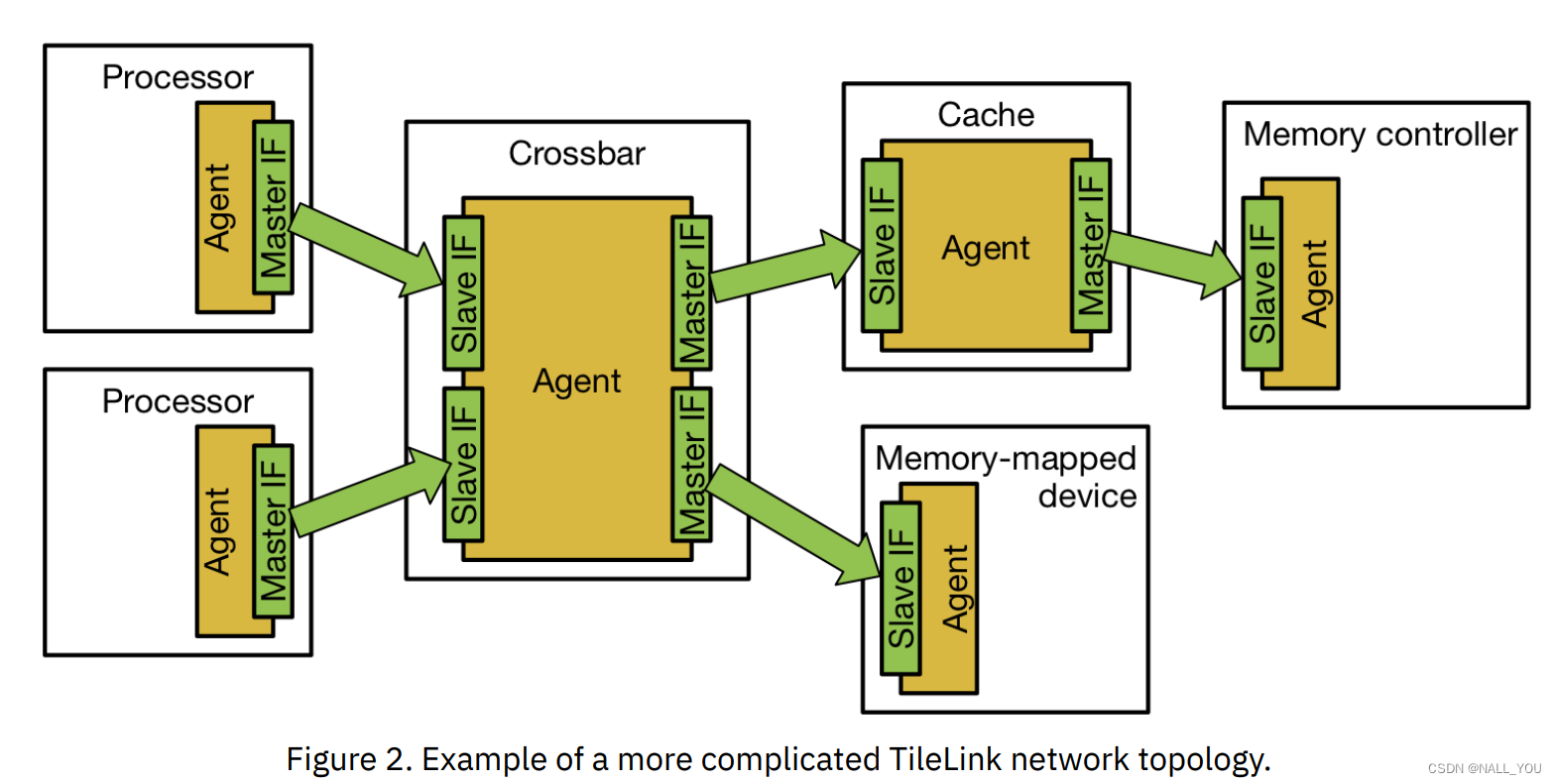

TileLink 支持多种网络拓扑,但须遵守第 5.3 节中指定的限制。图 2 说明了此类拓扑的示例,其中两个模块(交叉开关和缓存)具有代理,这些代理在其右侧具有主接口,在其左侧具有从接口。

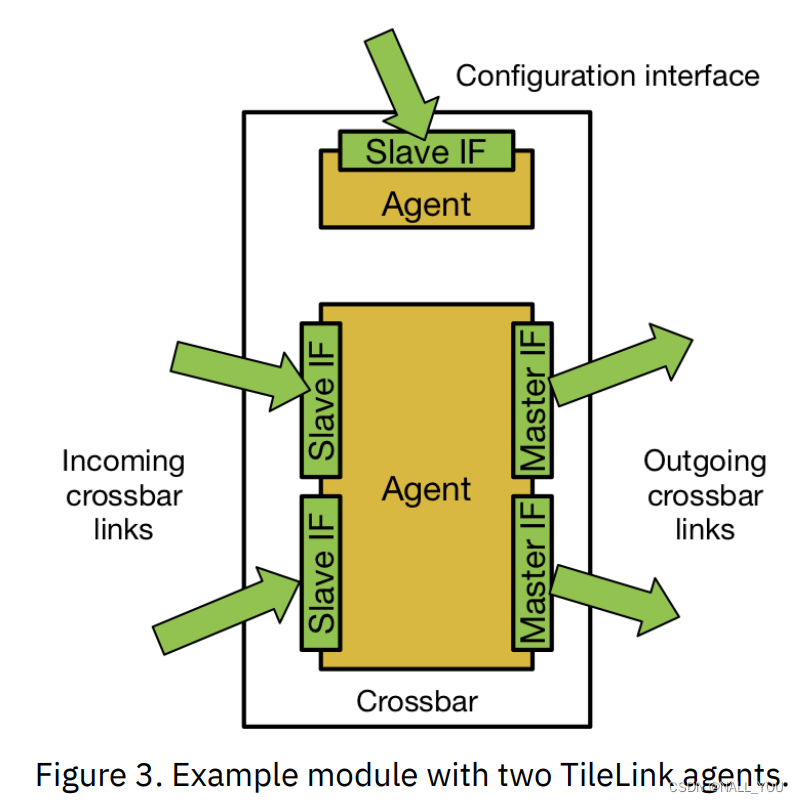

需要注意的是,单个硬件模块可以包含多个独立的 TileLink 代理。图 3 显示了一个示例,其中交叉开关具有一个在链路之间路由数据的代理和一个允许访问配置状态的第二个代理。

这是包含两个代理的更复杂的交叉模块的示例。一个代理具有多个接口,用于在正常操作中路由数据,而另一个代理具有单个从属接口来访问交叉开关的配置数据。

2.2. Channel Priorities

在每个网络链路中,TileLink 协议定义了五个逻辑上独立的通道,代理可以通过这些通道发送消息。为了避免死锁,TileLink 在通道消息中指定了必须严格执行的优先级。大多数通道都包含事务控制信号以及用于交换数据的总线。通道是定向的,因为每个通道都从主接口到从接口或从从接口到主接口传递消息。图 4 说明了5 个通道的方向性。

执行内存访问操作所需的两个基本通道是:

通道 A 发送在指定地址范围上执行操作的请求,访问或缓存数据。

通道 D 向原始请求者传输数据响应或确认消息。最高协议一致性级别 (TL-C) 添加了三个额外通道,提供管理缓存数据块权限的功能:

通道 B 传输在主代理缓存的地址处执行操作的请求,访问或写回缓存的数据。

C 传输数据或确认消息以响应请求。

通道 E 传输来自原始请求者的缓存块传输的最终确认,用于序列化。

跨通道消息的优先级为 A < B < C < D < E,按优先级递增的顺序。优先级确保流经 TileLink 网络的消息永远不会进入路由或等待循环。换句话说,通过所有代理之间的所有通道的消息流仍然是非循环的。

这是 TileLink 保持无死锁的必要属性;详细信息请参见第 5 节。

2.3. Address Space Properties

属性根据操作所针对的地址范围来限制允许注入 TileLink 网络的消息。可能归属于地址空间的属性包括:TileLink 一致性级别、内存一致性模型、可缓存性、FIFO 排序要求、可执行性、特权级别和任何服务质量保证。

依靠属性,TileLink 将确定特定地址上可能执行哪些操作的问题与消息本身的内容分开。通过将确定操作是否合法的工作预先加载到发送发起请求消息的代理上,TileLink 能够避开其通道内容中的各种信号。

用于描述哪些地址范围具有哪些属性以及这些属性如何控制消息注入的特定机制超出了本文档的范围。

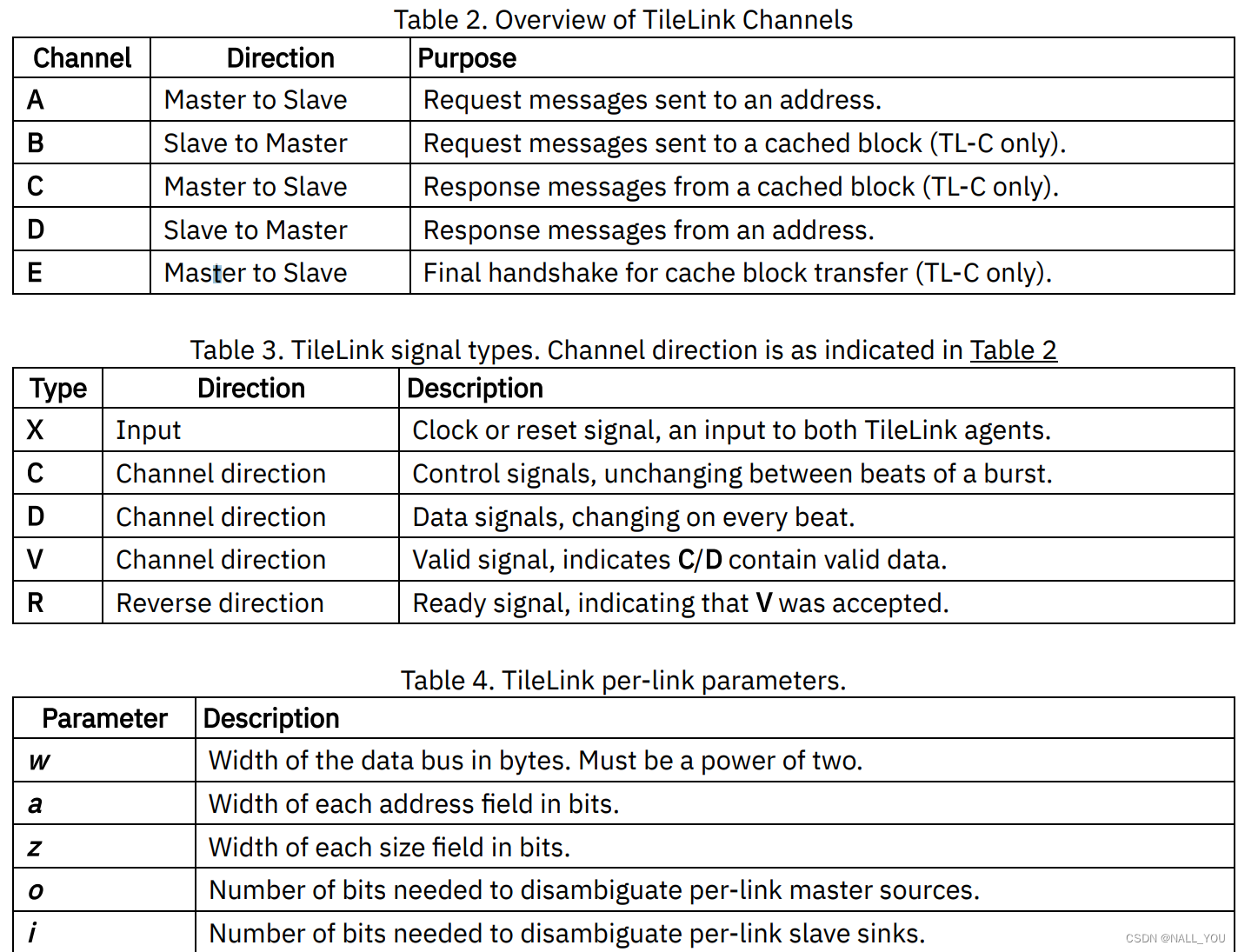

3. Signal Descriptions

本章列出了 TileLink 五个通道使用的所有信号,总结于表 2 中。与每个通道的方向结合时,表 3 中的信号类型决定了信号方向。这些信号的宽度由表 4 中描述的值进行参数化

3.1. Signal Naming Conventions

除了时钟和复位信号之外,TileLink 信号名称由通道标识符 (a–e) 后跟下划线和信号名称组成(在以下小节中列举)。对于具有多个 TileLink 接口的设备,建议在所有 TileLink 信号名称前添加一些描述性标记和下划线。例如,a_opcode 变为 gpio_a_opcode。

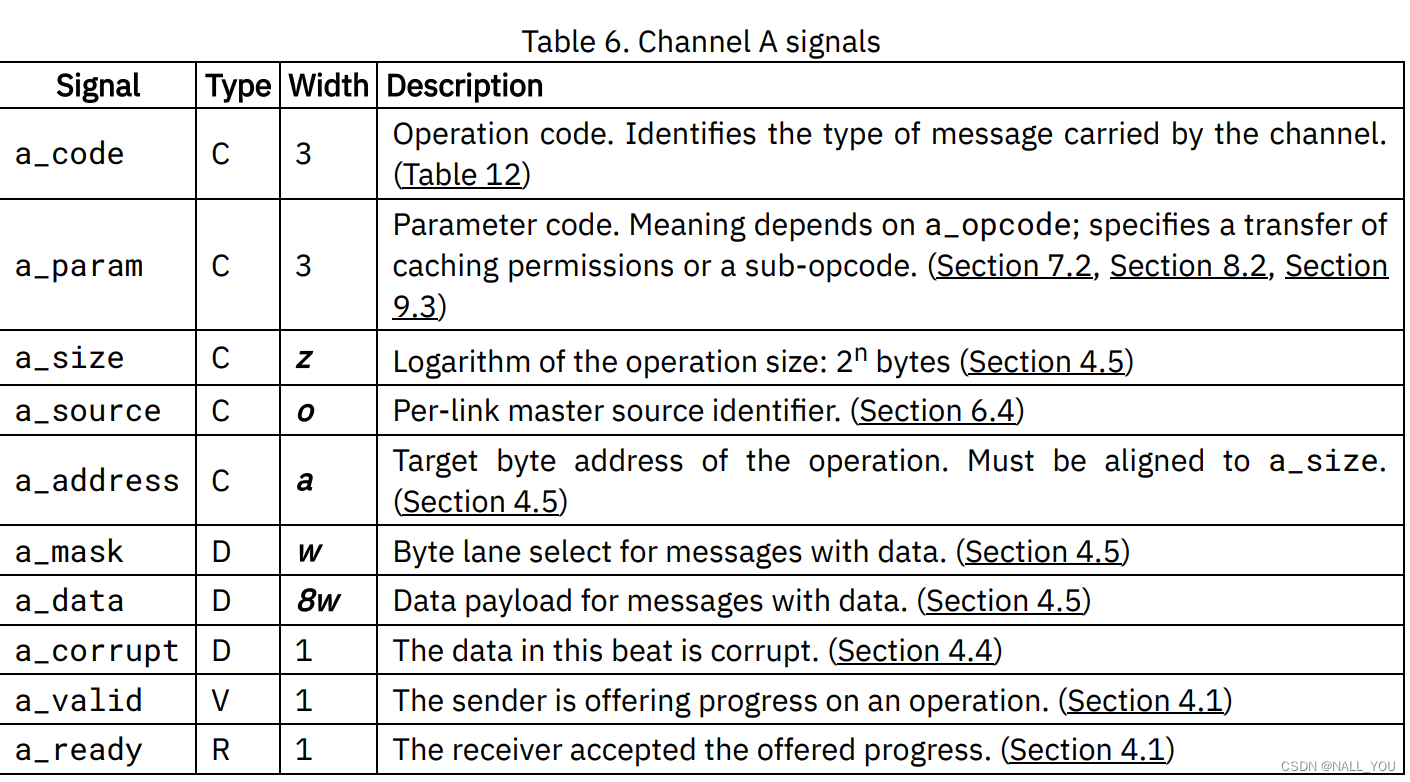

3.3. Channel A (Mandatory)

通道A从主接口流向从接口,承载发送到特定地址的请求消息。此通道由所有 TileLink 一致性级别使用,并且是强制性的。

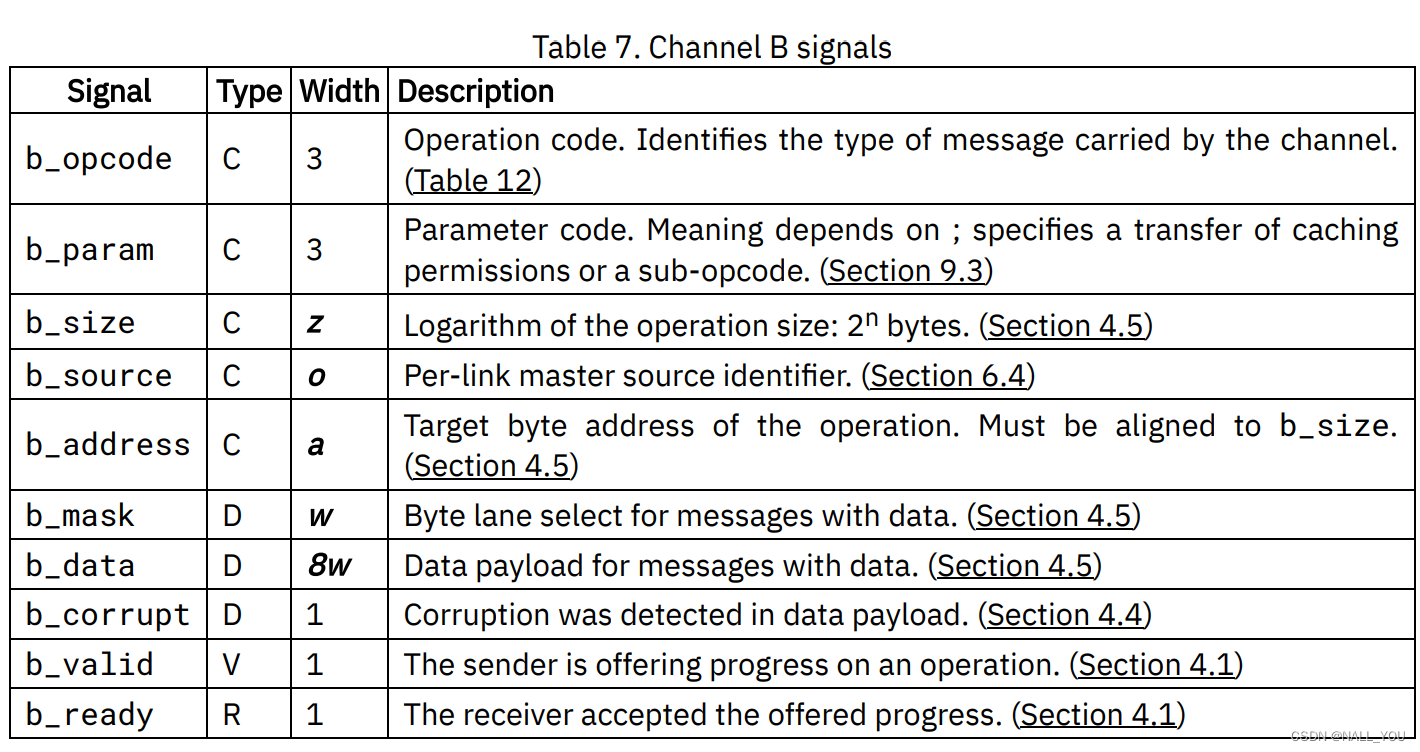

3.4. Channel B (TL-C only)

通道 B 从从接口流向主接口,承载发送到特定主接口持有的特定缓存数据块的请求消息。该通道由 TL-C 一致性级别使用,并且在较低级别中是可选的。

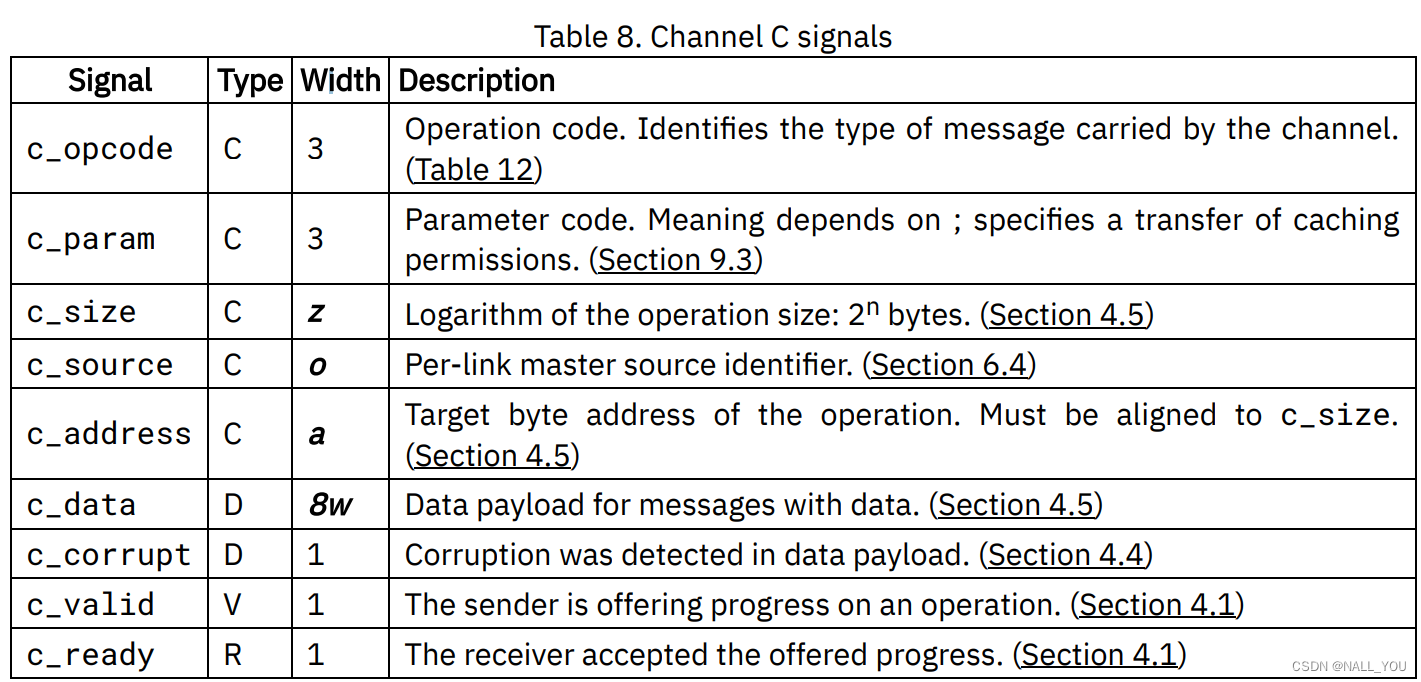

3.5. Channel C (TL-C only)

通道 C 从主接口流向从接口。它可以携带对发送到特定缓存数据块的通道 B 请求的响应消息。它还用于自动写回脏的缓存数据。该通道用于 TL-C 一致性级别,在较低级别中是可选的。

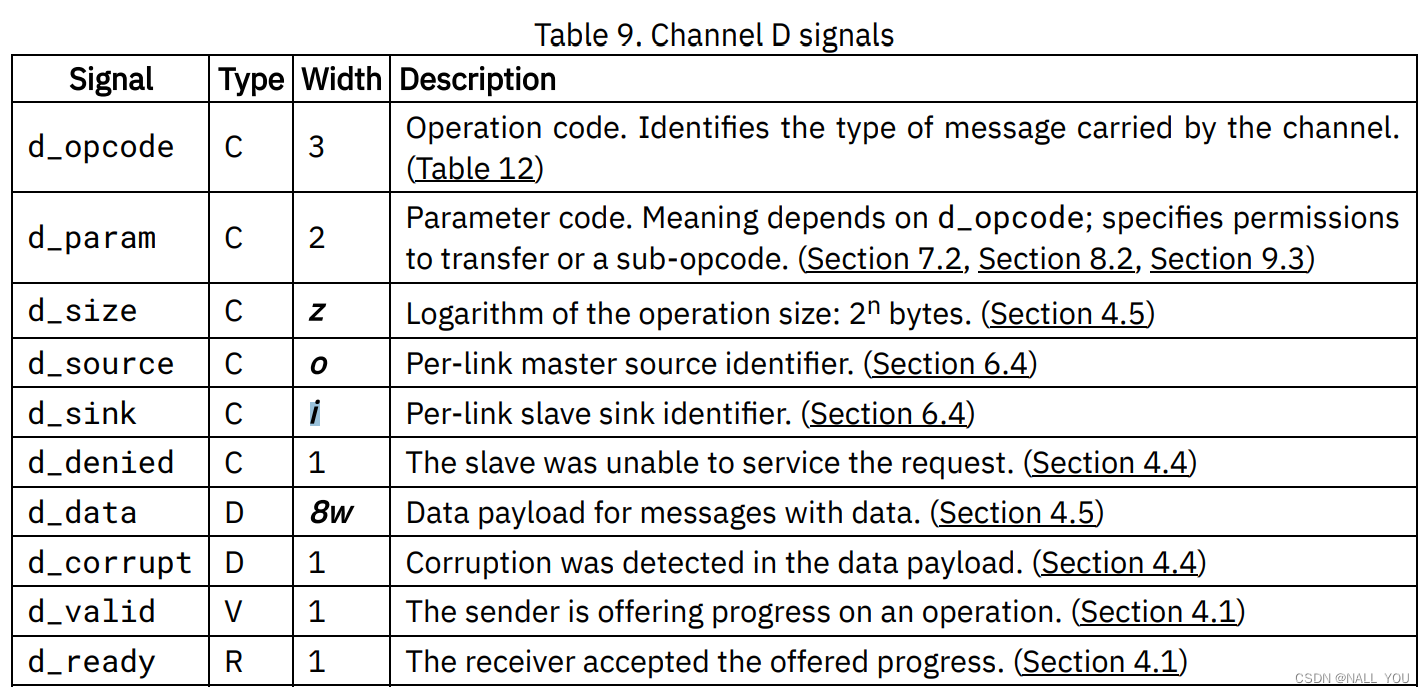

3.6. Channel D (Mandatory)

通道 D 从从接口流向主接口。它携带发送到特定地址的通道 A 请求的响应消息。它还载有对通道 C 自愿回写的确认。此通道由所有 TileLink 一致性级别使用,并且是非可选的。

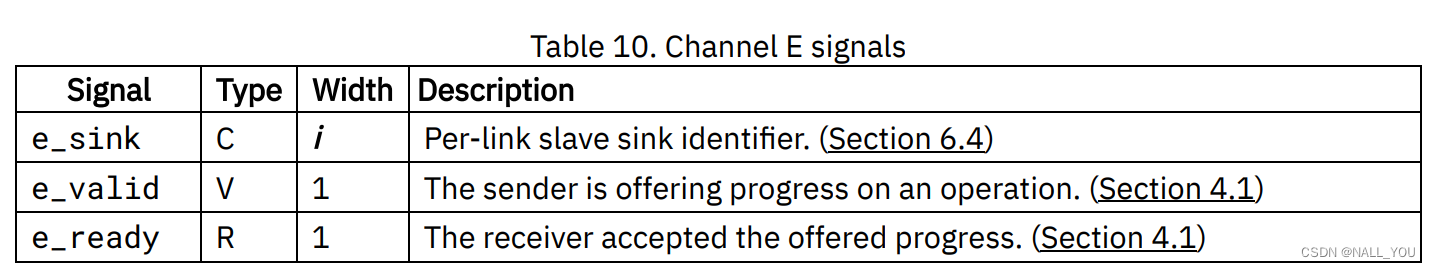

3.7. Channel E (TL-C only)

通道 E 从主接口流向从接口。它携带对通道 D 响应消息的接收确认,用于操作序列化。该通道用于 TL-C 一致性级别,在较低级别中是可选的。

4. Serialization

TileLink 中的 5 个通道被实现为 5 个物理上不同的单向并行总线。

每个通道都有一个发送器和一个接收器。

对于 A、C、E 通道,具有主接口的代理为发送方,具有从接口的代理为接收方。

对于 B 和 D 通道,具有从接口的代理为发送方,具有主接口的代理为接收方。

许多 TileLink 消息包含数据有效负载,根据消息和数据总线的大小,该数据负载可能需要分布在多个时钟周期(或节拍)上。多拍消息通常称为突发。不带数据负载的 TileLink 消息始终在单节拍中交换。 TileLink 禁止在通道上交错不同消息的节拍。一旦突发开始,发送方不得发送任何其他消息的节拍,直到接收方接受突发的最后一个节拍。突发的持续时间由通道的大小字段决定。

操作的进度是通过特定通道上的发送和接收代理之间的节拍交换来调节的。节拍的发送者发出通道有效信号以提供通道上节拍的可用性。

接收器发出就绪通道信号以表明其接受节拍的能力。接收器降低就绪信号以表明它们正忙并且不接受节拍。

仅当同时提出ready和valid时,节拍的内容才被视为已交换。本章的其余部分列出了控制何时可以切换就绪和有效以交换消息节拍的流量控制规则,并且还定义了如何对请求/响应消息对进行排序的规则。

我们最后讨论与传统总线标准的接口、错误处理以及如何将突发数据映射到特定宽度的物理数据总线。

4.1. Flow Control Rules

为了实现正确的就绪有效握手,必须遵循以下规则: 如果就绪为低电平,则接收方不得处理节拍,发送方不得认为节拍已处理。

如果 valid 为低电平,则接收器不得期望控制或数据信号是语法上正确的 TileLink 节拍。

有效决不能依赖于就绪。如果发送方希望发送节拍,则它必须断言有效,而与接收方是否发出信号表示其已准备好无关。

因此,必须不存在从就绪到有效或任何控制和数据信号的组合路径。

低优先级有效不能组合地依赖于高优先级有效。

换句话说,发送请求的决定可能不基于在同一周期内接收响应。

高优先级就绪可能不会组合地依赖于低优先级就绪。换句话说,响应的接受可能不取决于请求在同一周期被接受。

任何不被禁止的事情都是允许的。

特别是: 接收器响应有效或任何控制和数据信号而驱动就绪是可以接受的。

例如,如果对繁忙的地址发出有效请求,则仲裁器可以降低就绪状态。不过,只要有可能,建议ready独立驱动,以减少握手电路深度。通道可以根据前一周期中的就绪值来更改有效信号和所有控制信号和数据信号。

例如,在请求被接受(就绪高电平)之后,可以提出新的请求。仅禁止 valid 对 read 的同周期依赖。设备可以根据同一周期内请求的有效性来合法地驱动响应的有效性。例如,立即响应的组合 ROM。在这种情况下,大概准备好请求将同样由准备好响应驱动。禁止相反的关系。

请注意,发送者可能会提高 valid 值,然后在下一个周期降低它,即使该消息在上一个周期未被接受。例如,发送方可能在下一个周期要执行一些其他更高优先级的任务,而不是尝试再次发送被拒绝的消息。此外,当消息未被接受时,发送者可以改变控制和数据信号的内容。

在可以承载突发的 TileLink 通道上,还有其他限制。在接受第一个节拍之后直到接受最后一个节拍为止,据说突发正在进行。

当突发正在进行时,如果 valid 为高电平,则发送方必须另外提供: 仅来自同一消息突发的节拍。

控制信号与第一节拍的控制信号相同。数据信号对应于前一个节拍的地址加上数据总线宽度(以字节为单位)。如果突发中的第一个数据节拍被拒绝,则发送方可以选择在下一个周期尝试不同的消息(包括启动不同的突发)。

如果已经在进行中的突发的数据节拍被拒绝,则发送方可以选择在下次呈现该节拍时改变数据的值。

然而,无论下一个有效节拍上出现的数据值如何,都将继续对应于相同的地址,直到接收器接受某些提供的节拍。

只有接受的节拍才会导致突发在与数据有效负载的节拍相关的地址范围内取得进展。正在进行的突发的控制信号对于所有有效节拍必须保持恒定,直到突发完成。

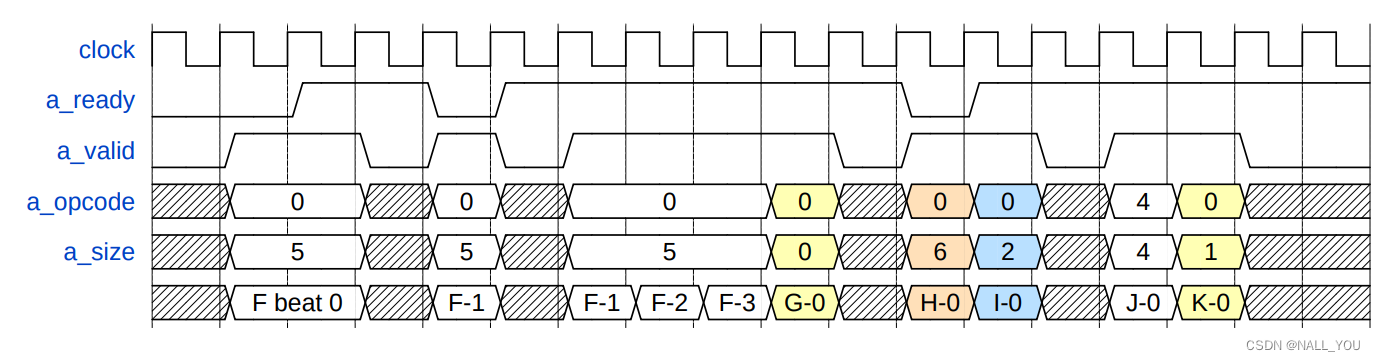

图 6 展示了一个 8 字节宽通道遵守这些规则的波形。

图中发送了 6 条消息:F、G、H、I、J、K。

请注意,所有控制和数据的有效性信号基于有效高电平。仅当就绪和有效均为高电平时才会交换节拍。

第一个消息 F 的大小为 5,这表示该操作访问 2n = 32 字节。 Opcode 0 是 PutFullData 消息,因此 F 携带数据。由于该特定通道 A 的宽度足以传输 8 字节节拍,因此有 4 个节拍的数据需要交换。这些被表示为 F-0、F-1、F2 和 F-3。出现 F-0 的第一个周期,从机不接受它。主站选择重复F-0,然后被接受。 F-0 被接受后,突发 F 被认为正在进行中。因此,主人别无选择,只能重复F-1,直到接受为止。然而,主设备仍然可以在突发期间降低有效值。然后,大师继续按顺序呈现 F 节拍(这是必须的),直到最后一个节拍 F-3 被接受。第二条消息 G 的大小为 0,表示 1 字节消息。该尺寸可以一次性发送并立即交换。消息H(8拍突发)由主机提出,但被拒绝。由于突发的第一个节拍未被接受,因此突发未在进行中,并且主设备选择在下一个周期呈现不同的消息 I。消息H永远不需要被发送。

消息 J 具有操作码 4,它在通道 A 上表示 Get。尽管 Get 对 a_size 指示的 16 个字节进行操作,但消息 J 本身不携带数据,因此在单个节拍中发送,立即接受。然后可以在下一个周期发出并接受消息 K。

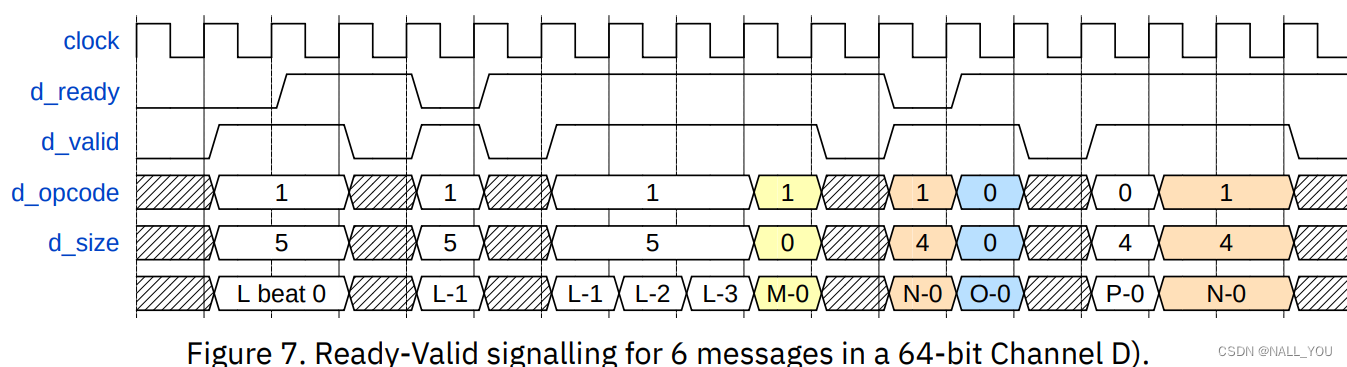

图 7 中的 8 字节宽 D 通道说明了遵守这些规则的另一个波形。

图中发送了 5 条消息:L、M、N、O、P。这些是在通道 D 上发送的响应消息。提供了一个与图 6 中使用的示例请求消息序列无关的示例,但它们确实说明了同一组基于就绪-有效的流控制规则适用于请求和响应通道。

第一个消息 L 的大小为 5,这表示访问的操作为 25 = 32 字节。 Opcode 1是AccessAckData消息,因此L携带数据。因为这个特定的通道 D` 承载 8 字节节拍,所以有 4 个节拍的数据需要交换。这些被表示为 L-0、L-1、L-2 和 L-3。出现 L-0 的第一个周期,主设备不接受它。从机选择重复L-0,然后被接受。 L-0被接受后,突发L被认为正在进行中。因此,从机别无选择,只能重复L-1,直到被接受为止。

然而,从设备在突发期间仍然可以自由地降低有效值。然后从机继续按顺序呈现 L 的节拍(这是必须的),直到最后一个节拍 L-3 被接受。

第二条消息 M 的大小为 0,表示 1 字节消息。

该尺寸被转换为一个节拍并立即交换。消息N由从站提出,但被拒绝。由于突发的第一个节拍未被接受,因此突发未在进行中,并且主设备选择在下一个周期呈现不同的消息 O。为了完成 TileLink 中的操作,所有响应消息最终都必须发送,因为所有请求最终都必须收到响应。

与上一示例中被拒绝的消息不同,出于事务完成原因,最终必须再次提供消息 N。消息 O 的操作码为 0,在 D 上表示 AccessAck。即使AccessAck是响应于对d_size指示的16字节执行的操作,消息O本身不携带数据,因此在单个节拍中传送,其被立即接受。然后消息 N 被发出并最终在接下来的周期被接受。

4.2. Request-Response Message Ordering

我们现在定义了管理何时可以发送响应消息的规则,特别强调包含多个节拍的突发。

允许响应消息的第一个节拍有效:与请求的第一个节拍有效的周期相同,但不能早于该节拍。

在请求消息的第一个节拍之后的任意时间之后,但前提是在请求消息的第一个节拍期间请求通道上的就绪和有效为高电平。

这意味着在请求消息和响应消息的第一个节拍的同一周期中,响应通道上的就绪高电平意味着请求通道上的就绪高电平。特别是,请求通道上的有效高电平和就绪低电平以及响应通道上的有效高电平和就绪低电平是合法的。然而,如果响应通道上有有效高电平和就绪高电平,则请求通道上的有效高电平和就绪低电平是非法的。突发响应消息的第一个节拍之后的节拍也可以在任意长的延迟之后呈现,但是来自其他消息的节拍之间不能交织。

事实上,响应消息可以与请求的第一节拍同时并结合地接收,这与第 5 节中的转发进度规则相互作用。这些规则控制接收响应的代理何时可能出现,例如d_ready 为低电平,而 d_valid 为高电平。例如,设计人员可能会尝试实现一个主接口,该接口将 d_ready 保持为低电平,而 a_valid 为高电平,以便将并发响应消息延迟到下一个周期。然而,这表示通道 D 上的无限延迟,这是任何前向进度规则都不允许的。事实上,符合 TL-UL 标准的从接口可能已分别将 d_valid 和 d_ready 连接到 a_valid 和 a_ready。因此,不合格的主接口导致了死锁。

…====================================================================================================…

两个模块通过链路连接,一个模块包含具有主接口的代理,另一个模块包含具有从接口的代理。

具有主接口的代理向具有从接口的代理发送请求。如果需要,具有从属接口的代理与后备存储器进行通信。

获得所需的数据或权限后,从站响应原始请求者。

TileLink 支持多种网络拓扑,但须遵守第 5.3 节中指定的限制。

图 2 说明了此类拓扑的示例,其中两个模块(交叉开关和缓存)具有代理,这些代理在其右侧具有主接口,在其左侧具有从接口。

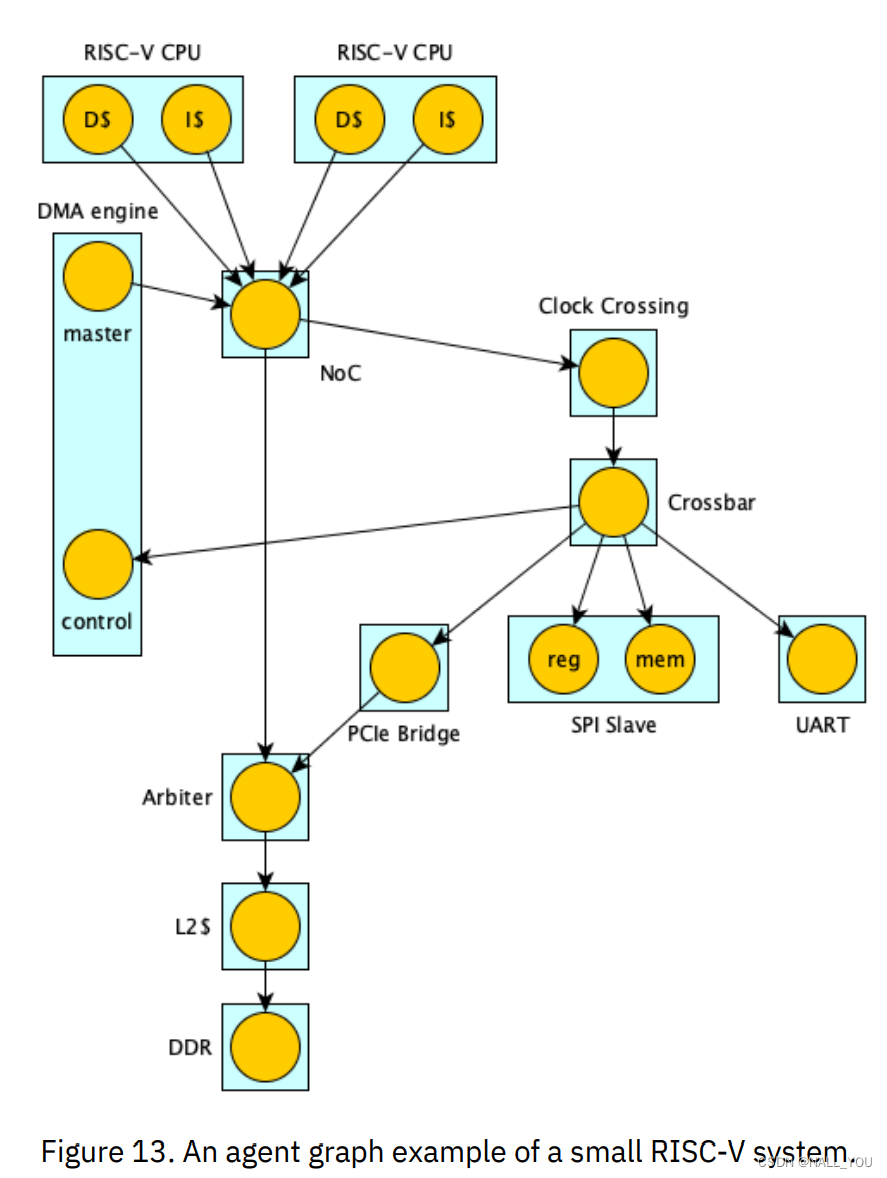

回想一下,规则 1 要求代理图不包含循环。绘制代理图时的一个很好的约定是排列代理,使所有边都指向下方。这使得图表中没有循环变得非常明显。

该示例图包括两个 RISC-V 内核,每个内核都有一个指令和数据缓存。尽管每个核心都是一个模块,但缓存是两个不同的代理。通常,缓存彼此独立运行;它们之间没有消息耦合(规则 3)。因此,链路可以连接到共享模块中的两个独立代理。

稍微不太明显的是 DMA 引擎。为了让主控链路和控制链路按原样连接,没有循环,引擎需要两个独立的代理。这意味着控制接口必须能够响应请求,而无需等待 DMA 主控操作完成。

片上网络 (NoC) 被视为单一代理,多少有些无伤大雅。这可以作为一个假设的令牌环网络来实现,该网络围绕芯片旋转,在连接的 TileLink 链路上丢弃消息。代理图经常严重歪曲物理模块和逻辑代理的物理布局和大小/复杂性。请注意,令牌环代理微体系结构内循环的存在不会违反 TileLink 的前向进度保证,只要 TileLink 链接支持前向进度规则。

系统中一种经常出现问题的设备类型是 PCI Express (PCIe) 桥接器。 PCIe 内的排序规则具有将发送到 PCIe 桥接器的请求的转发进度耦合到从 PCIe 桥接器发送的请求的转发进度的效果。由于这种耦合,有必要(根据规则 3)使用单个代理来表示 PCIe 桥。在此代理图中,这迫使我们限制 PCIe DMA 仅具有主内存的可见性,而不是外围交叉开关(包括 PCIe)的可见性。

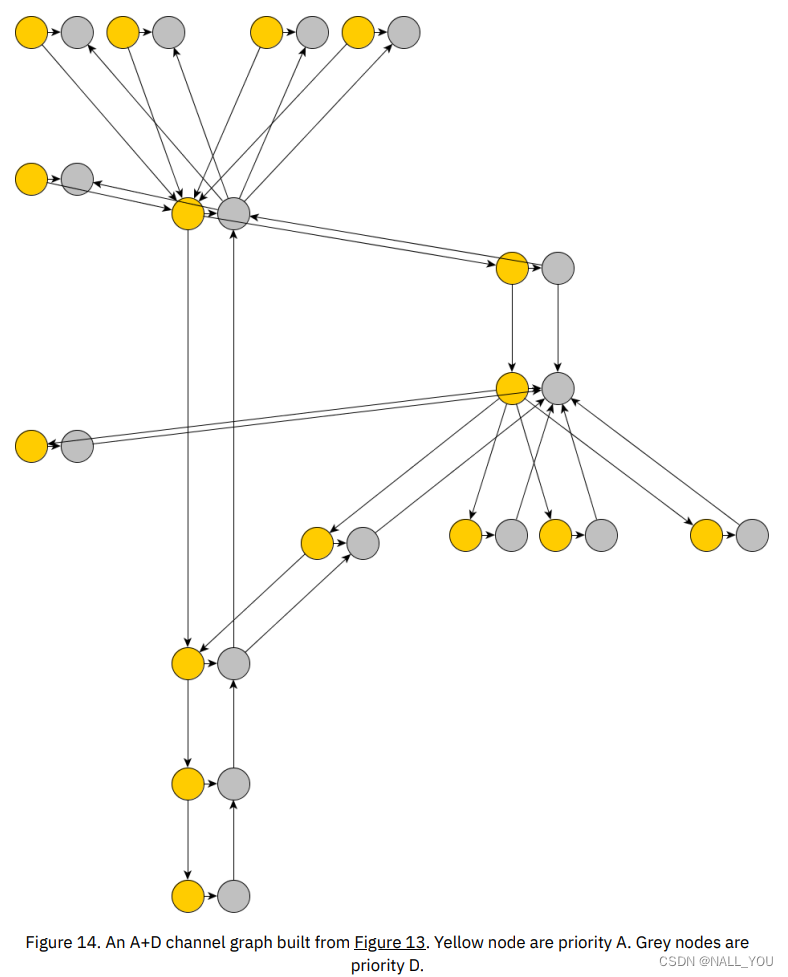

给定一个有向无环代理图,我们必须将其转换为有向无环通道图。为此,请将每个代理复制为 5 个副本,并将它们标记为 A-E,每个通道一个。然后,反转连接 B 和 D 类型节点的所有 35 个箭头。最后,连接节点副本,使 A 指向 B 指向…E。两个通道 (A+D) 的示例可以在图 14.

119

119

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?