图片来源:南京大学软件学院COA课程PPT

©author:zzb

文章目录

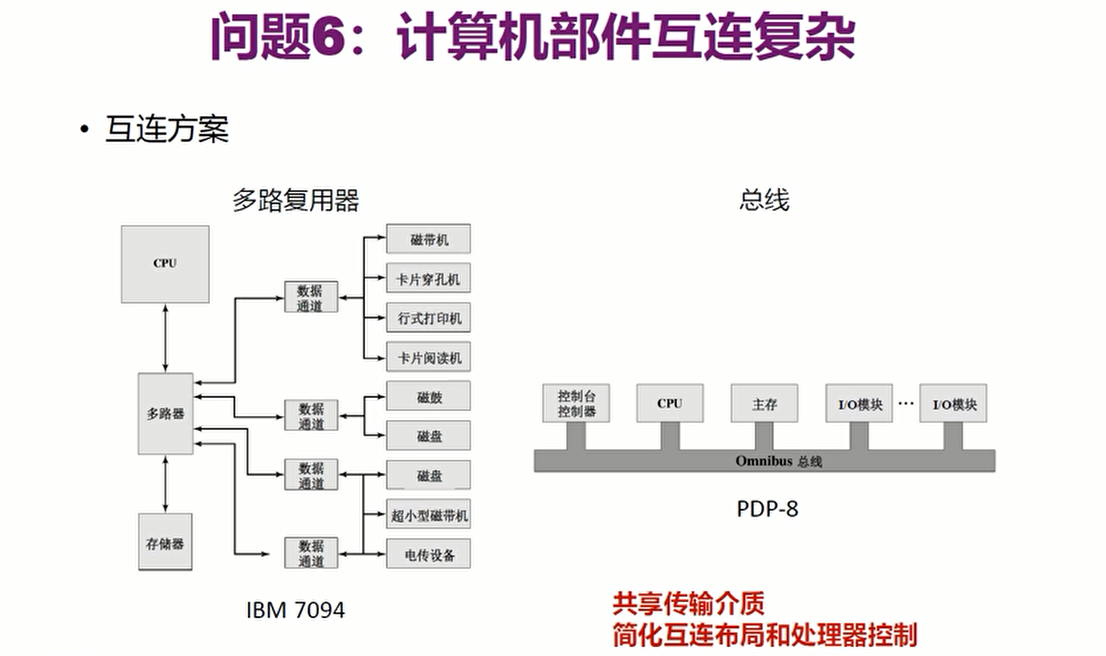

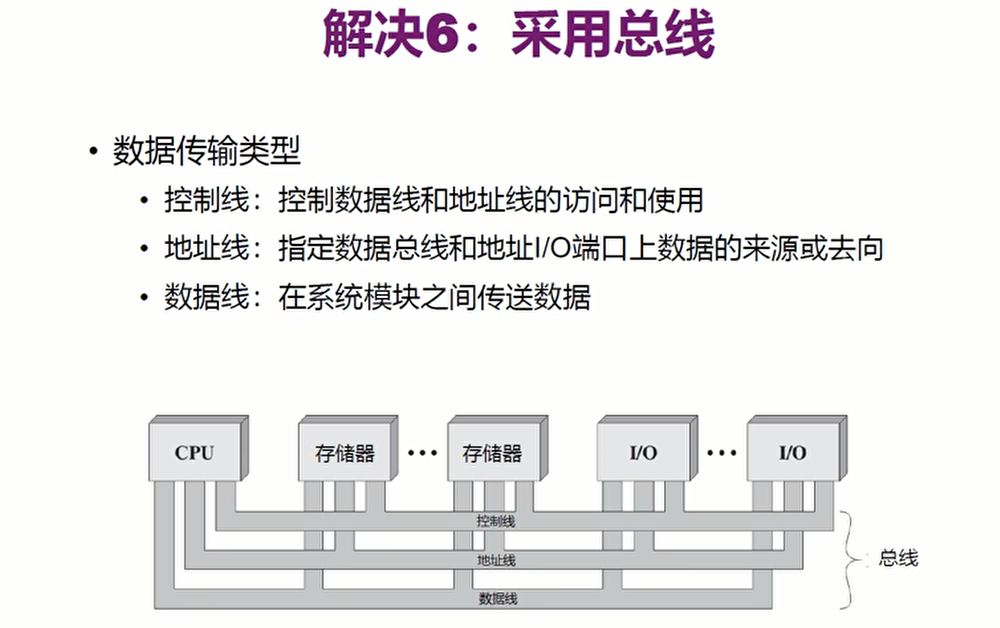

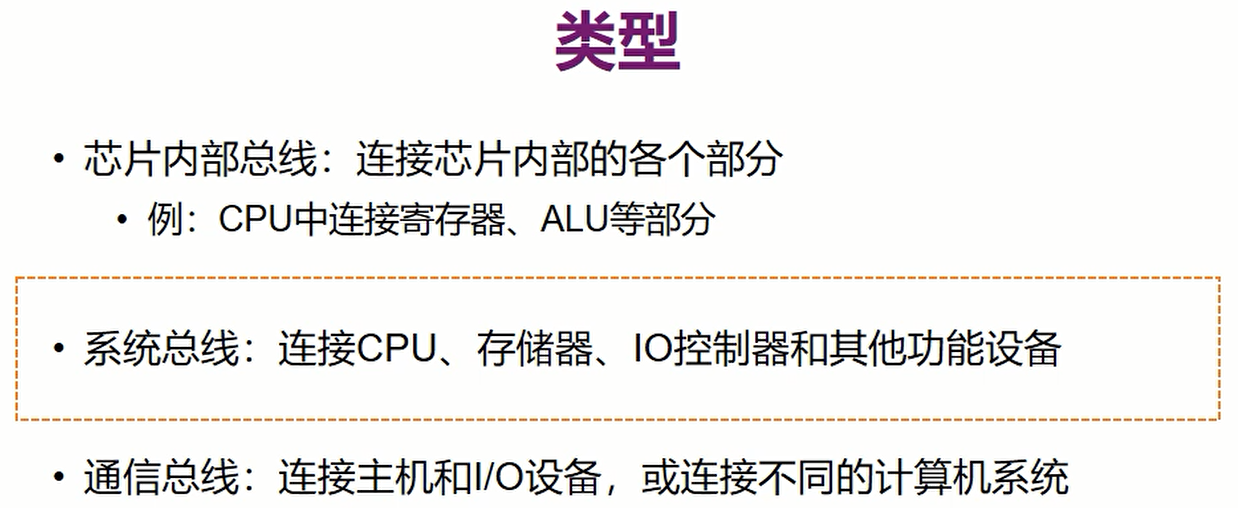

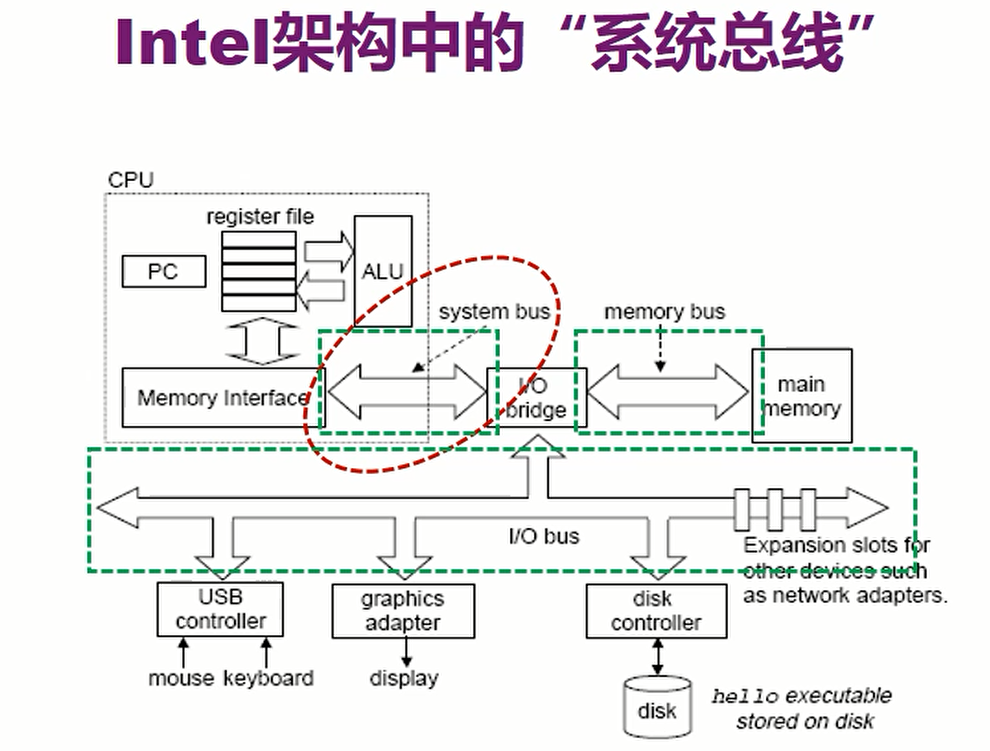

13 总线

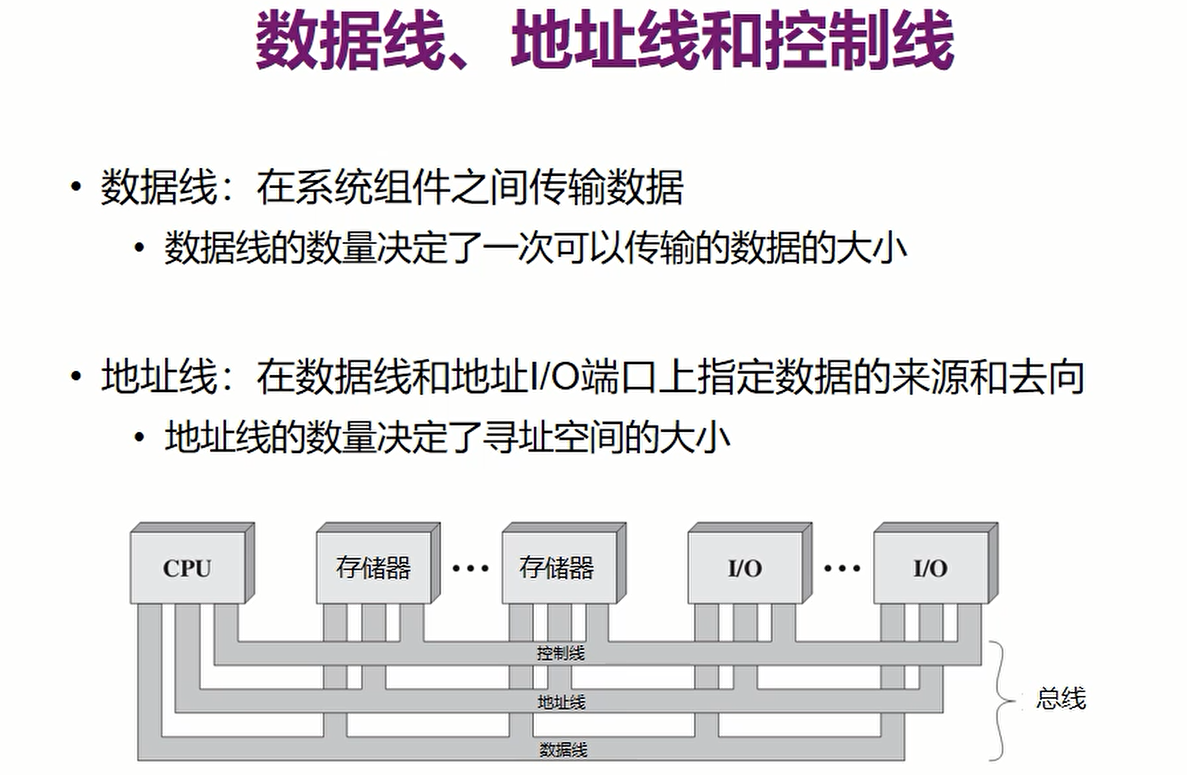

总线包括芯片内部总线、系统总线、通信总线

系统总线在不同位置不同场景下会有不同的含义,课程中主要把系统总线作为一个通用的概念,而不是特指某条总线

地址不一定只能一次传输,事实上有时候是可以分成两次来传输地址的,这样就能扩展寻址空间,即寻址空间不是由地址线的宽度来决定的

当总线被使用时,其他设备不能抢占

用途

仲裁

要在优先级和公平性之间取得平衡

仲裁器是硬件设备,集中处理总线使用权

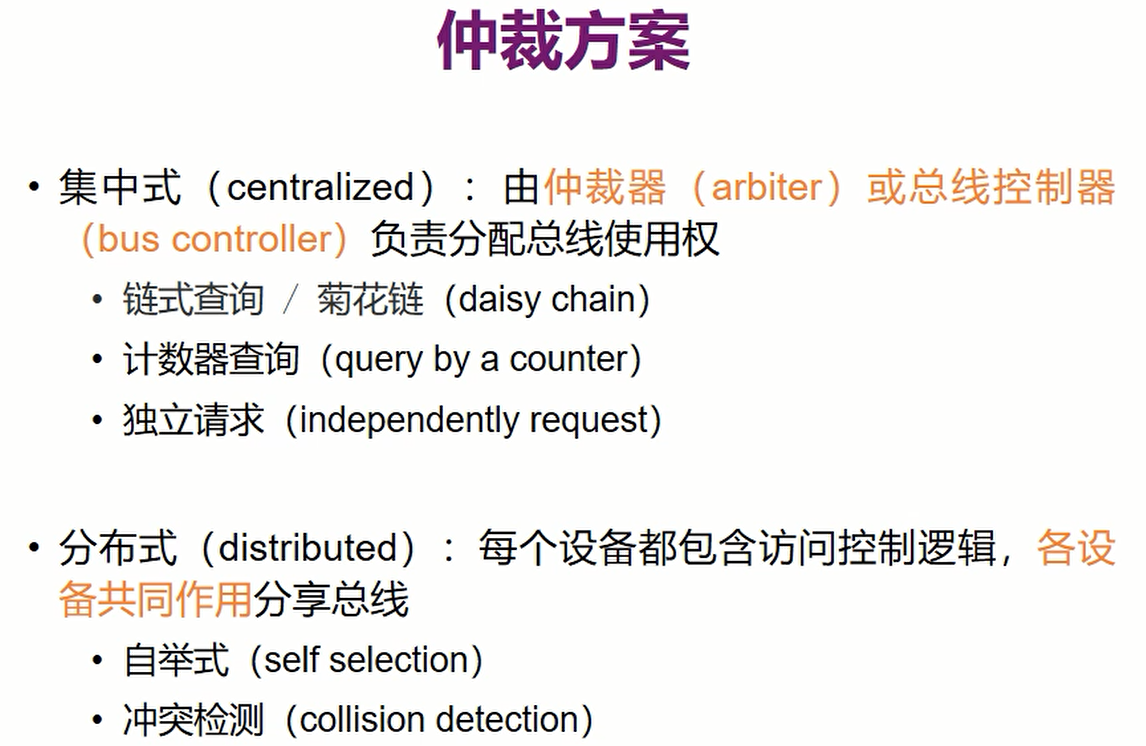

集中式

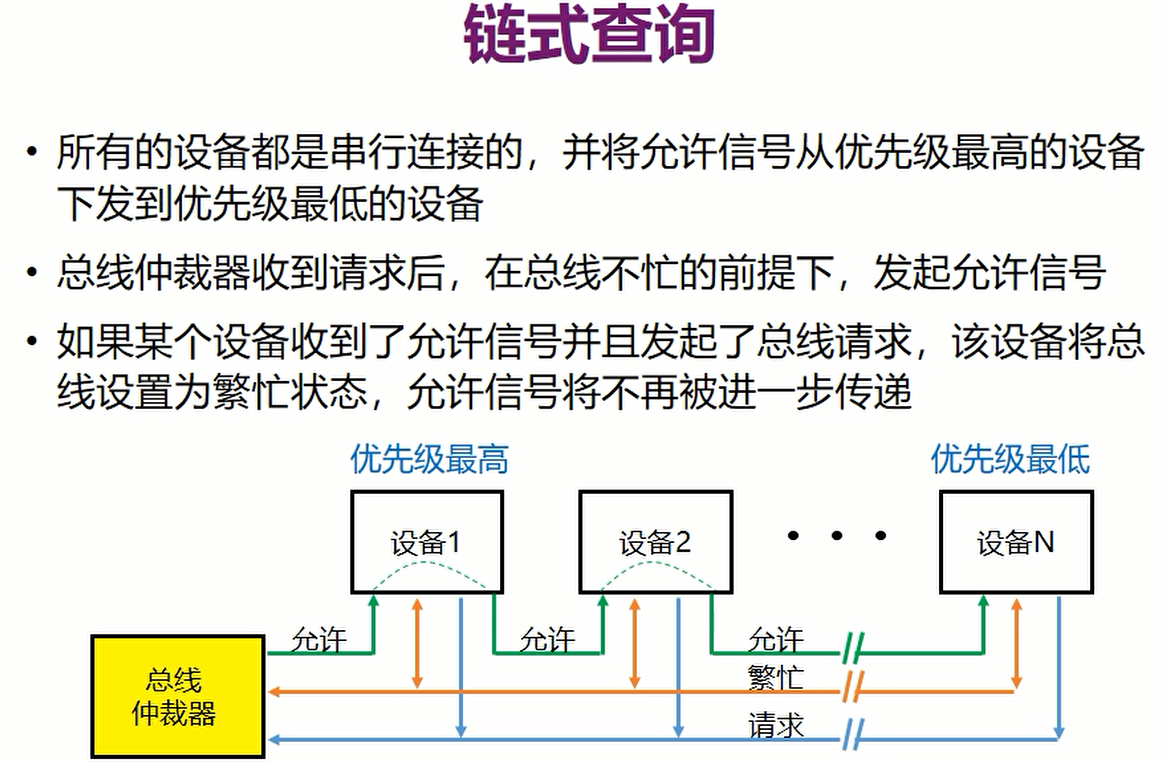

链式查询

允许信号从仲裁器下发,按优先级从高到底传递(串行),从而高优先级的设备如果要使用总线,则可以截取允许信号

繁忙线与各个设备之间是双向箭头,因为各个设备要去监听看总线是否繁忙,如果繁忙则不能发起请求。同时得到允许的设备要去修改这条线的状态,使之变成繁忙

连接的设备越多,那么速度就会越慢,因为允许信号要经过每一个设备

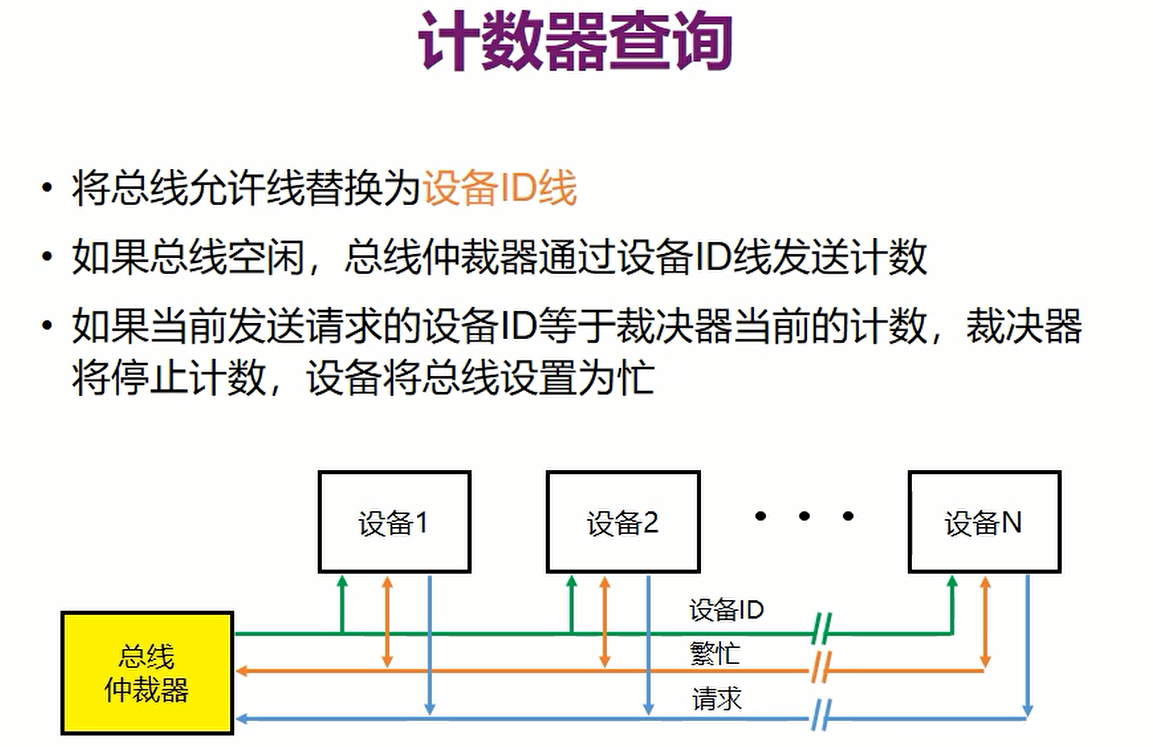

计数器查询

至少要log2n根线,来区分不同的设备ID,可以灵活的调整优先级

相当于一个个的报学号,可以按不同的顺序报,也可以从不同的位置开始报,从而来平衡优先级和公平性,先报到的可以使用总线

如果一个响应后又从1开始计数,那么就和上面的链式查询效果一样的

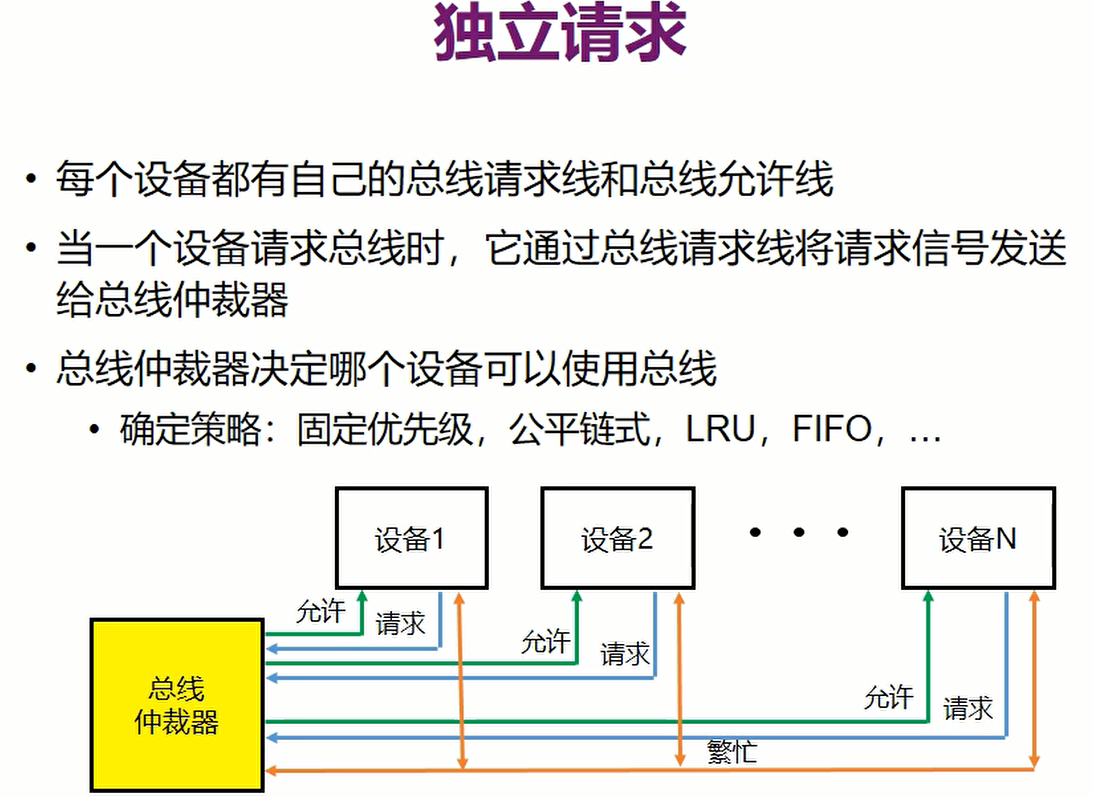

独立请求

仲裁器可以灵活使用不同的策略来分配总线

但线路更多了

不需要和前面一样要等待询问其他设备就可以请求总线,随时都发送请求,如果仲裁器通过了,就可以直接获得允许

分布式

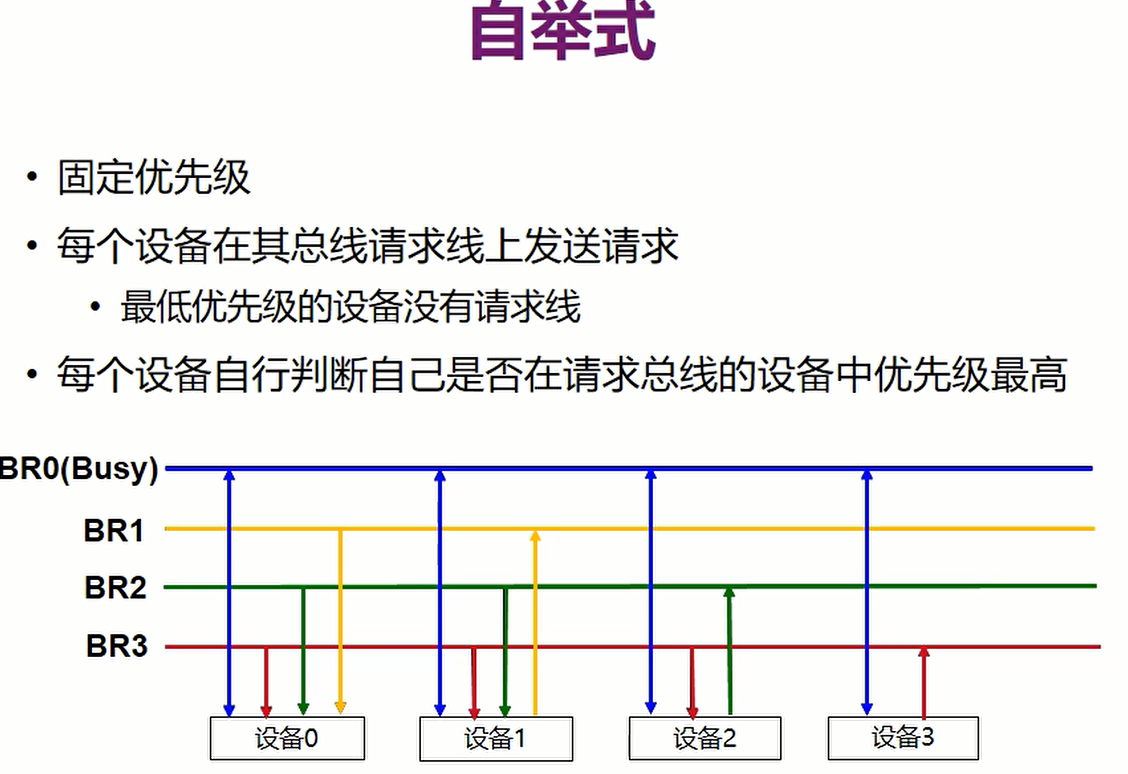

自举式

设备只需要关心优先级比它高的设备是否需要使用总线,而无需去关心优先级比它低的设备是否需要总线

因此高优先级需要关心的少,上面设备3的优先级最高,只需要关心是否总线忙即可

而最低优先级的设备没有请求线,如上的设备0,因为没有其他设备需要去关心它的请求

同样的当使用总线时要把总线设为忙

优先级很明显

冲突检测

公平性很明显

解决冲突要消耗一定的时间,效率会低一些

时序

总线事务是指在总线上完成一次数据的传递:是指根据一个地址,但数据可能会传输多次

同步时序??

所有设备共用一个时钟,会导致快的设备要去迁就慢的设备(即要等待慢的设备,而不像下面的异步一样快的设备只要发出信号就可以去做其他事情),也即快的设备的速度没法发挥出来。

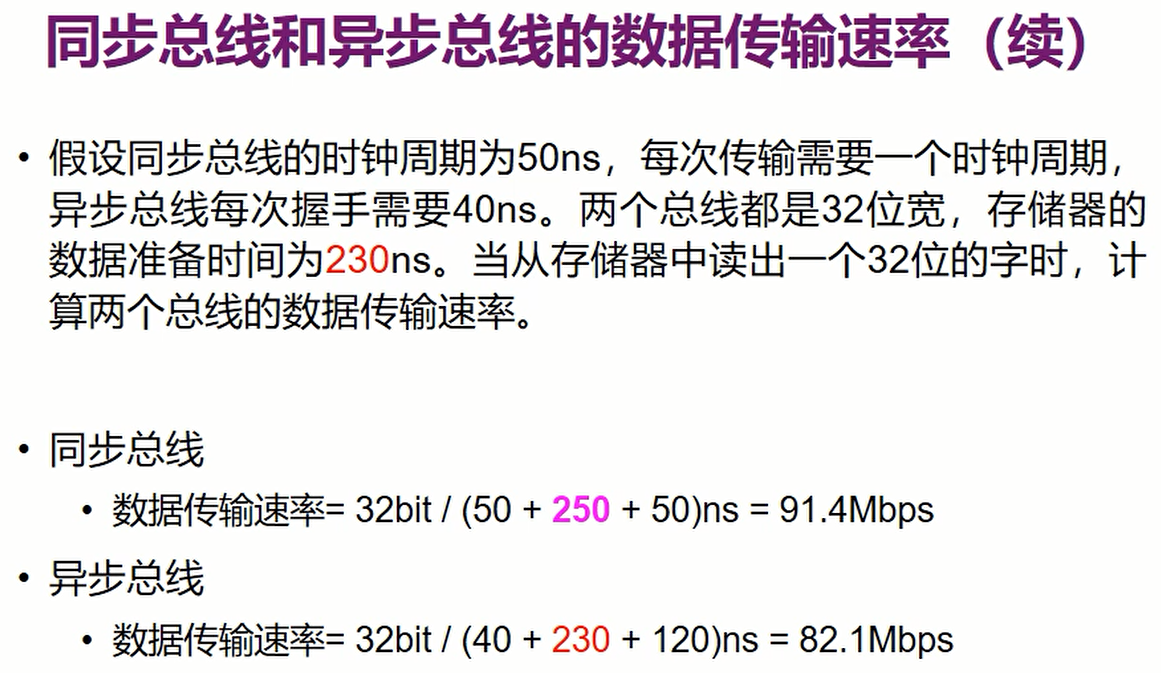

如时钟周期为50ns,存储器准备数据230ns,那么实际上仍然需要250ns才能完成数据的准备,因为必须在一个时钟周期开始才能进行下一步,所以即使存储器完成了准备,也需要等待时钟周期,而异步时序则当数据准备完成即可直接传输

总线不能太长,如果总线很长,那么时钟信号会有较大的延迟

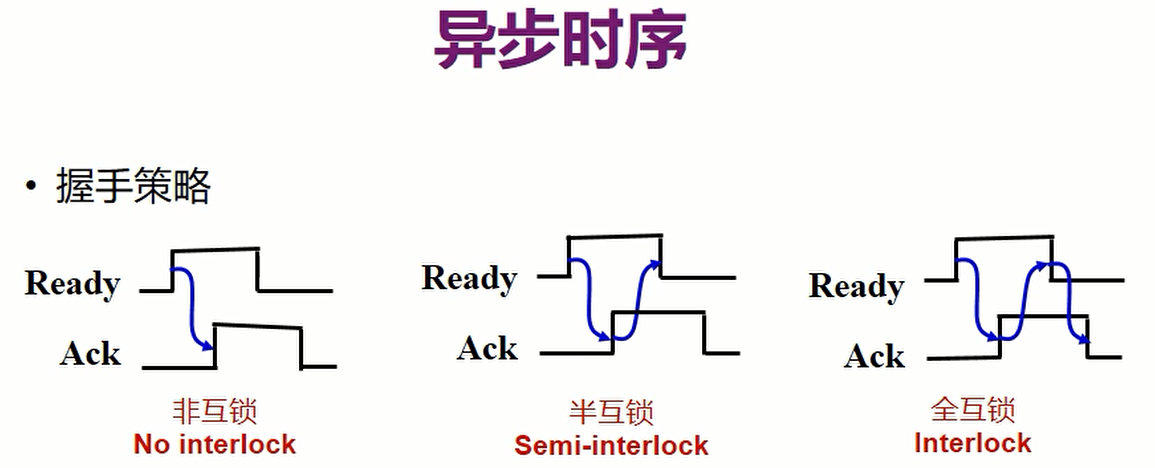

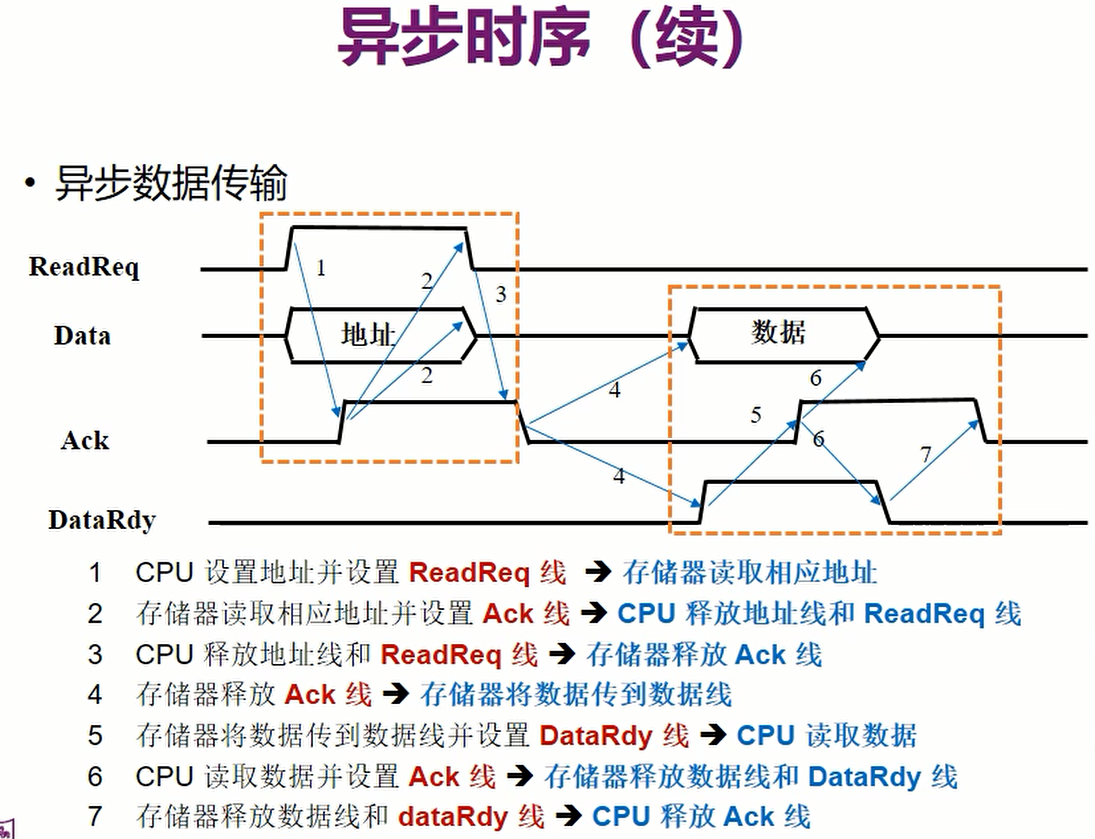

异步时序

Ready信号说明已经准备好了,设备可以来取,Ack信号表明告诉对方已经取完了,对方可以把ready信号给拿走了

信号都有上升沿和下降沿,分别表示把信号放到总线上和把信号从总线上拿走的过程

一次握手其实就是表明一个前后关系

- 非互锁是一个自然的状态,只通过一次握手,而没有加额外的限制,只是一个自然的先后关系,先准备好才能去取,然后才有取好信号

- 半互锁是用两次握手强调已经取完了之后Ready信号才能撤走,这是为了防止出现在取之前(并不是一出现Ready就去取,可能正在处理其他事务)就已经撤走了Ready,即撤早了,而无法取数据就一直处于等待的情况

- 全互锁是用三次握手强调只有Ready撤走后,才能撤走Ack,如果ready的设备正在处理其他事务,而另一个设备已经取好了,并撤走了Ack,那么设备就以为对方还没有取好,因此会一直处于Ready状态

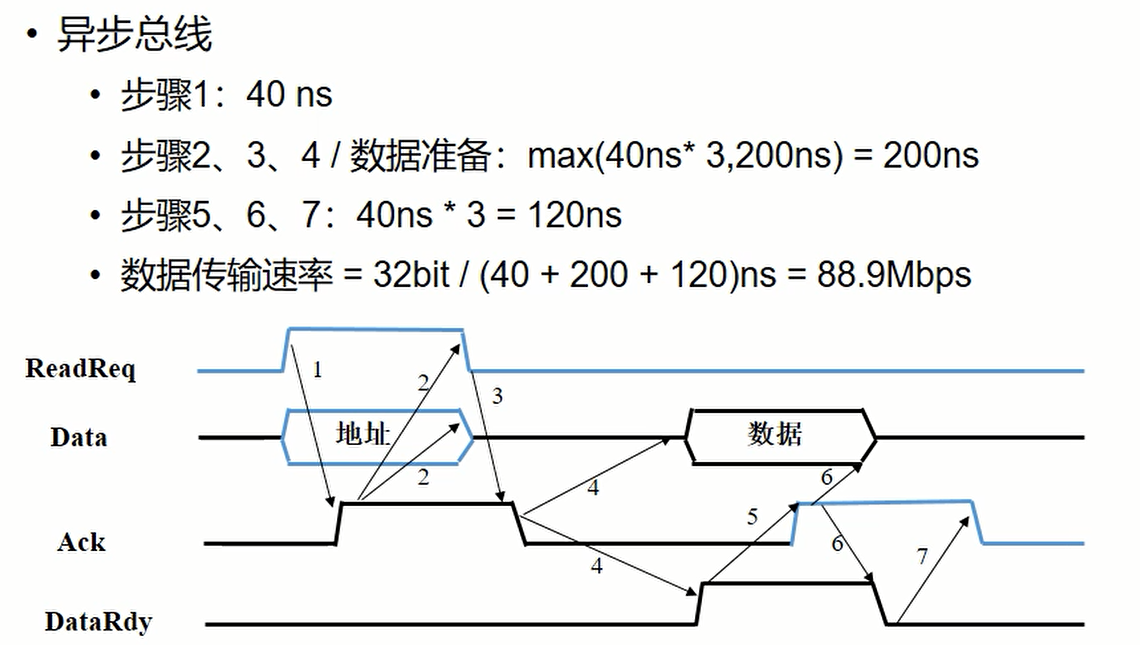

注意总共为7次握手,握手中即有数据传输的时间,所有的握手时间加起来即一次总线事务的时间,而不需要额外考虑数据传输。

如1花费了40ns,即存储器得到ReadReq信号并读取了地址并设置了Ack信号花费40ns。此时存储器已经得到了地址信息,可以开始准备数据。

数据准备阶段:在234中有3次握手,是为了保证顺序,当4结束时存储器把数据放到数据线上,因此这里花费的时间为

3次握手的时间和存储器准备这些数据的时间的最大值。

数据传输阶段:567则是通过3次握手,保证数据能传输到CPU中

上面3个部分全部加起来就是一次总线事务的时间,数据量/时间即数据传输速率

速度快的设备在Ready后,就可以去忙别的事情了,而等慢的设备Ack后,快的设备再回来处理这件事,从而协调好不同速度的设备

对噪声敏感是指设备可能把噪声误认为是信号,从而出现错误。因为异步信号的发送是没有固定的时间的,是很随意的,任何时间段都可以发出信号,所以会容易把偶然的噪声当作信号

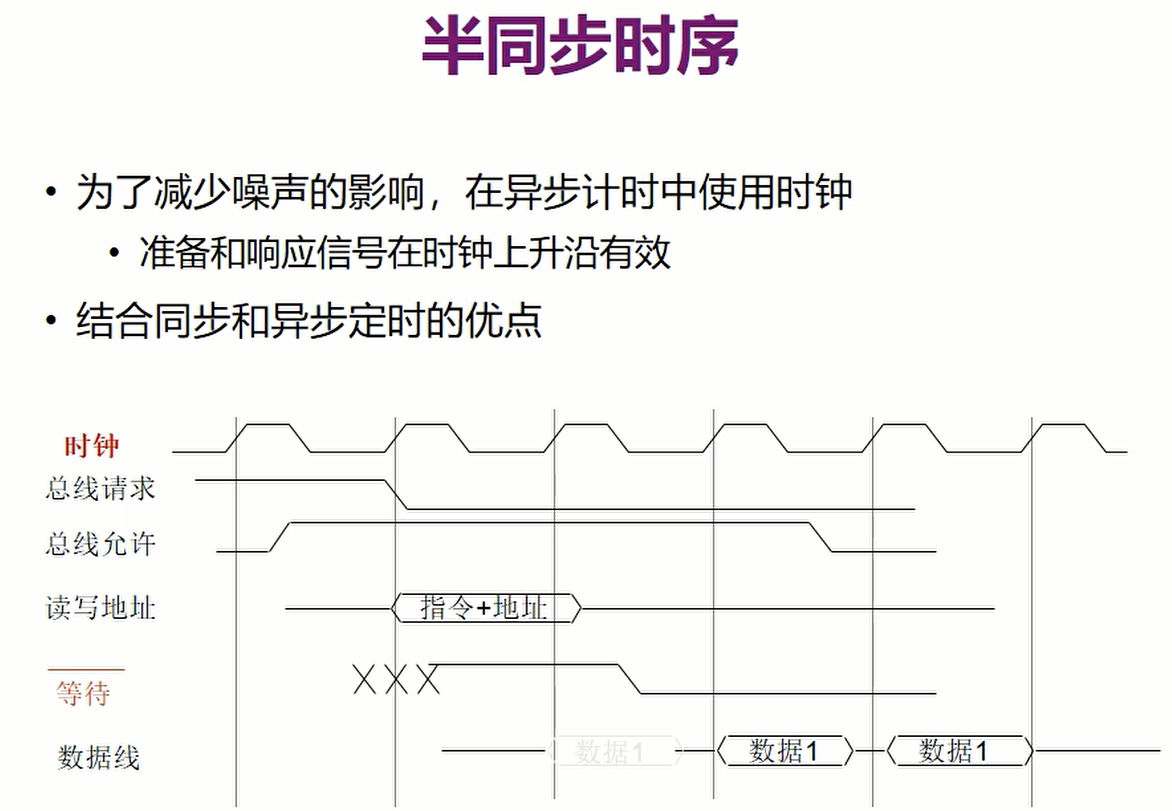

半同步时序

固定在上升沿才能发出准备和响应信号,其他时间段的信号均为无效,从而减少噪声的影响

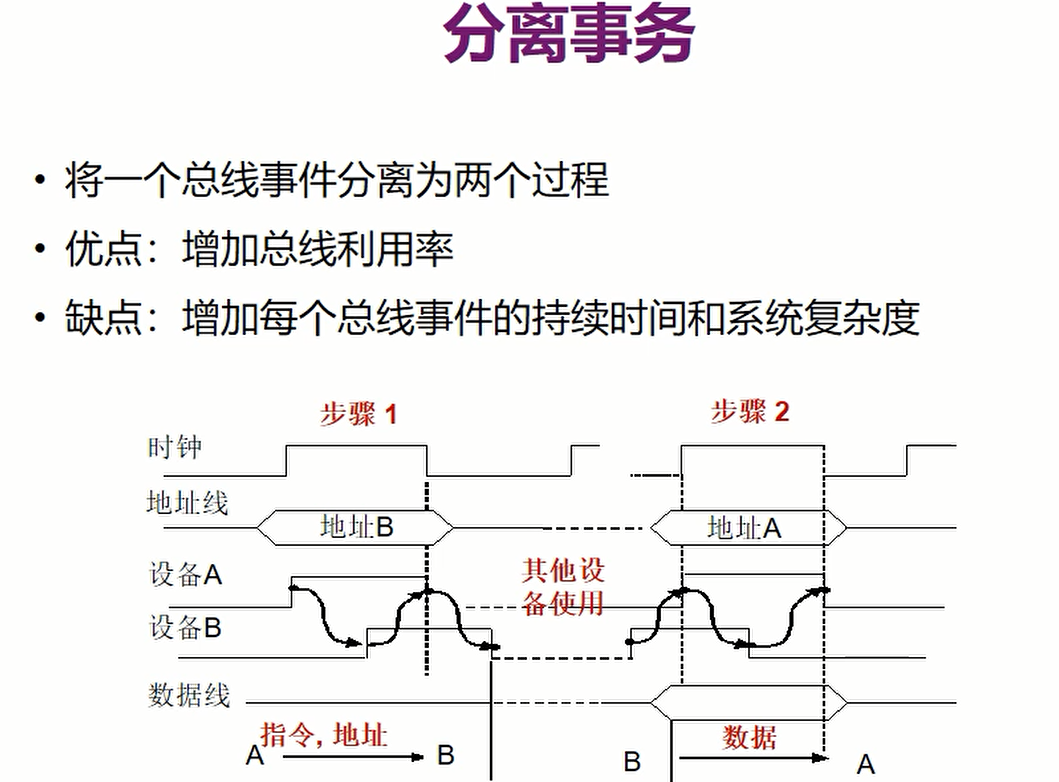

分离事务

即把总线事务分成地址传过去和数据传过来两个过程,在得到地址后准备数据的过程中,可以把总线释放出来,给其他设备使用,等数据准备好了,再去申请总线

提高了总线利用率

但这样会增加每个总线事务的时长,因为在数据准备好后再申请总线不一定立刻就能得到,可能需要等待一段时间

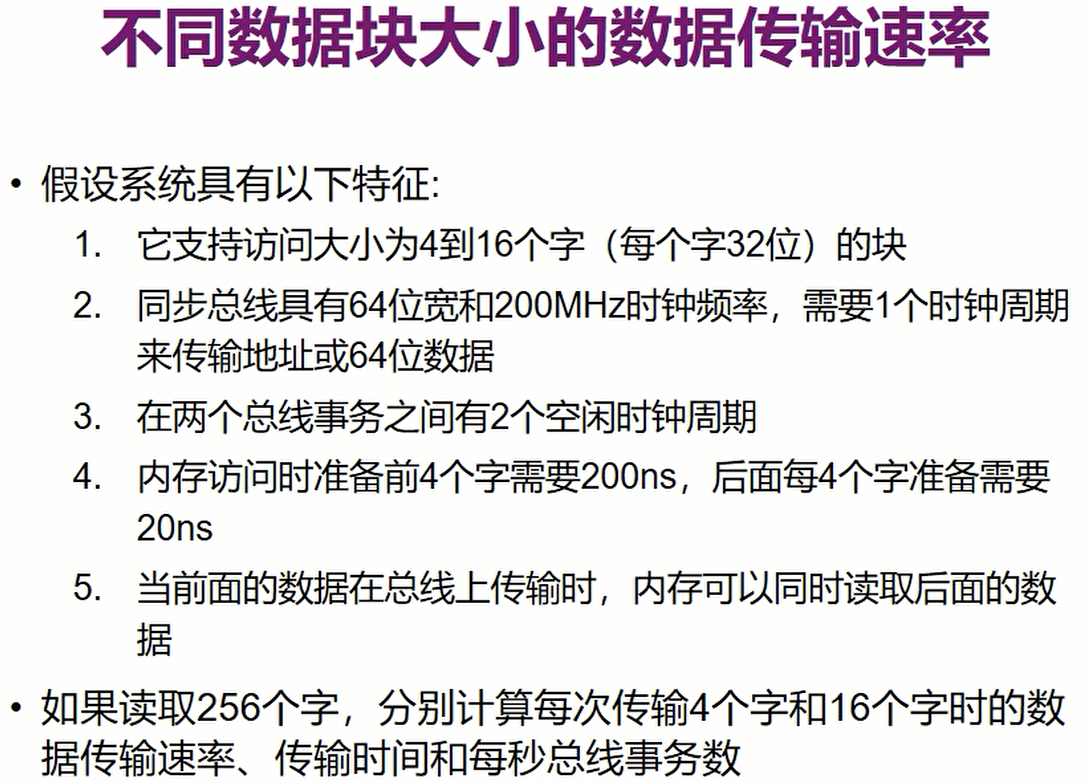

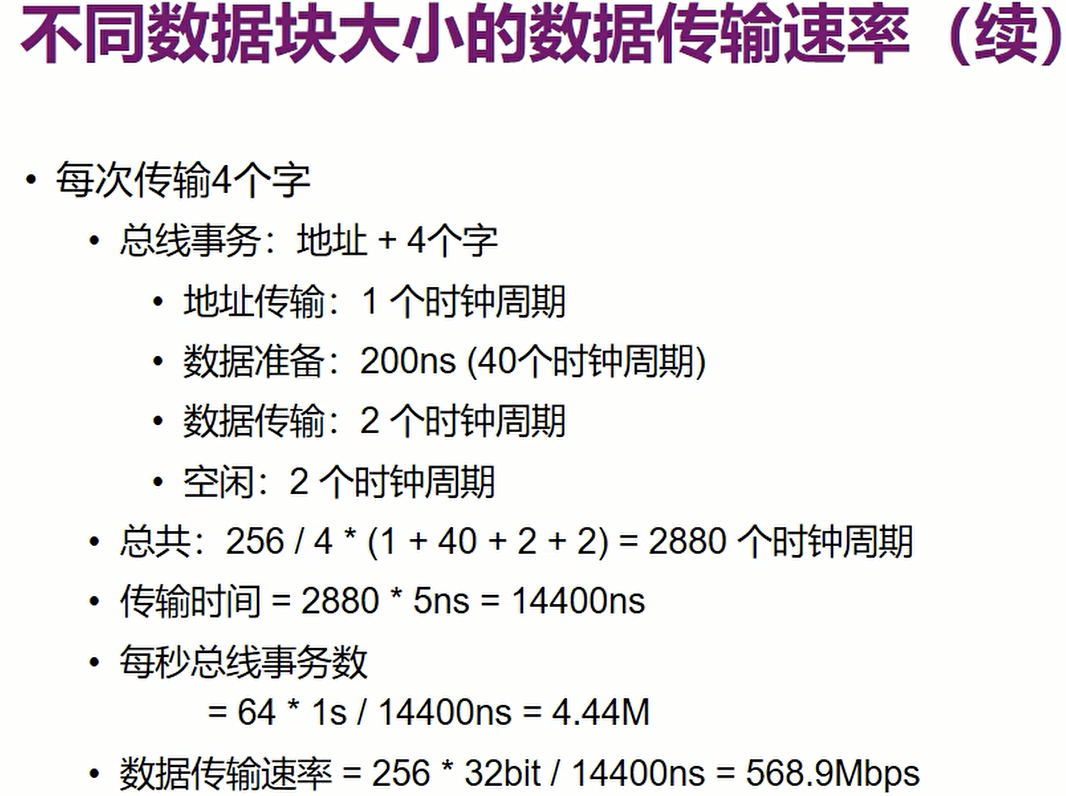

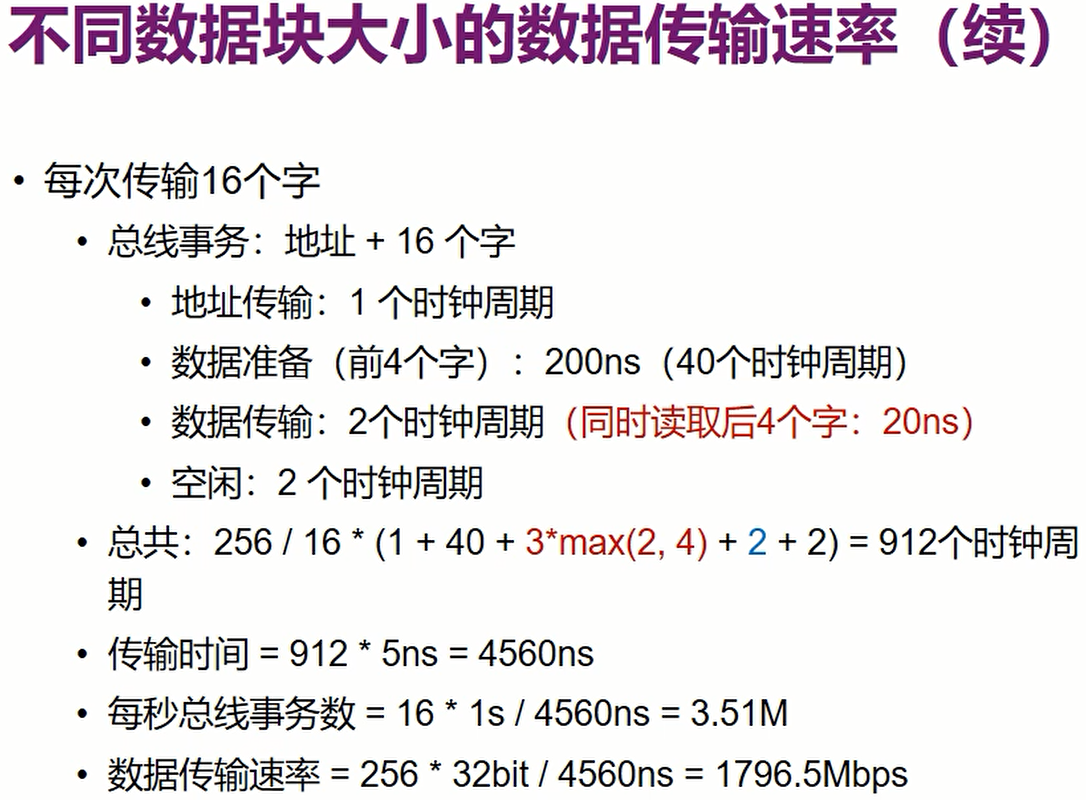

总线带宽和数据传输速率

总线带宽是理想状态下的数据传输速率,不考虑地址传输和总线仲裁

地址不算数据

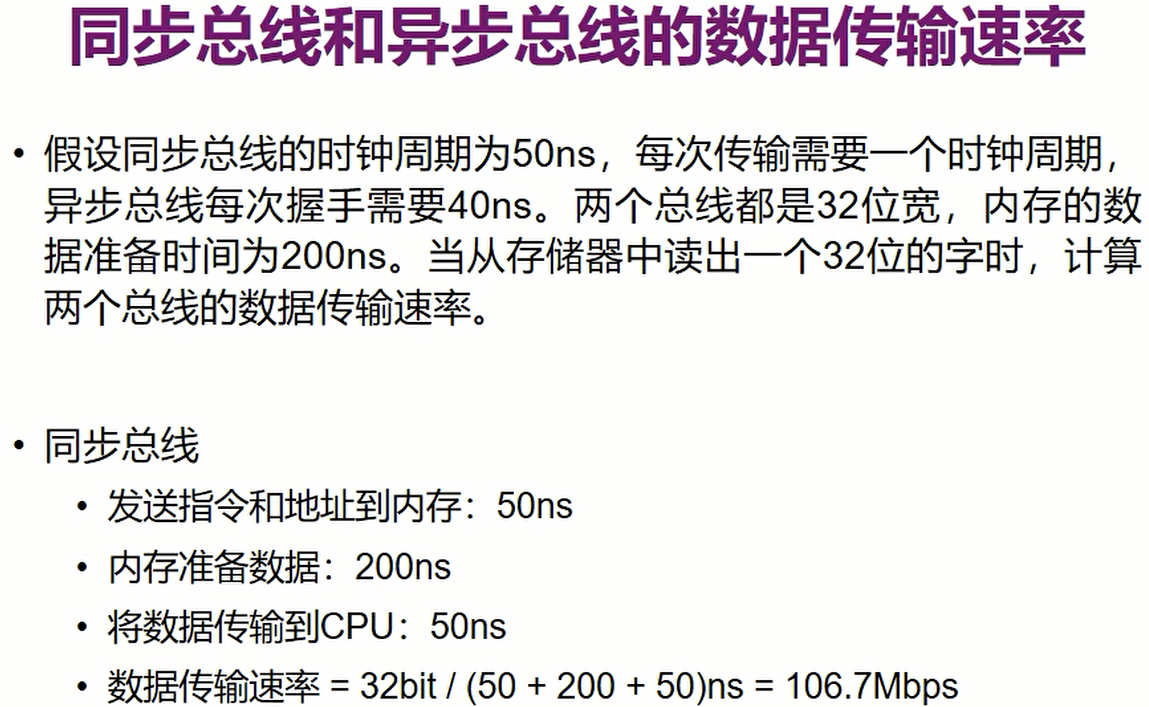

同步总线中一个时钟周期内只能做一件事情

计算数据传输速率只要计算传输一次4个或16个字即可,同时最后全部传完之后的空闲也要算进去,因为肯定还会有下一次总线事务,所以可以算入到每次传完后里面

这里每次总线事务都是可以理解是第一次访问内存,所以都需要花费200ns,只有像下面的一次传输一个块的,才是考虑后面的访cache速度快

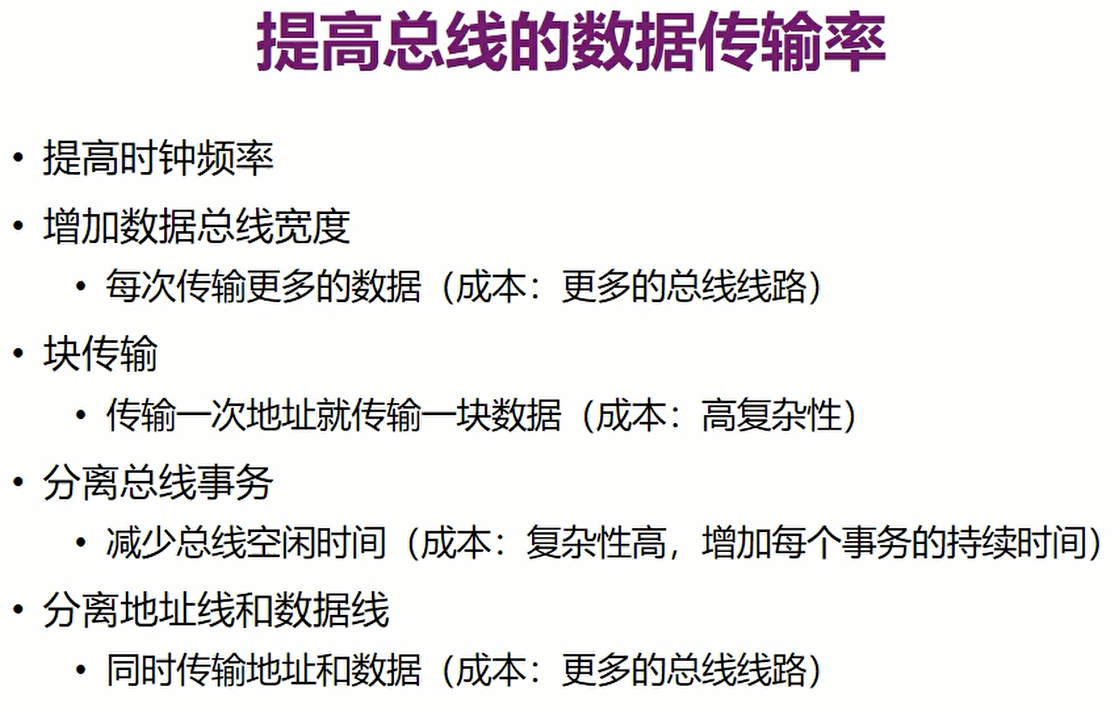

提高总线的数据传输率

块传输可以减少地址传输的时间,同时减少了准备数据的时间,因为有cache的存在,所以第一次数据读取会比较慢,但后续的读取会很快

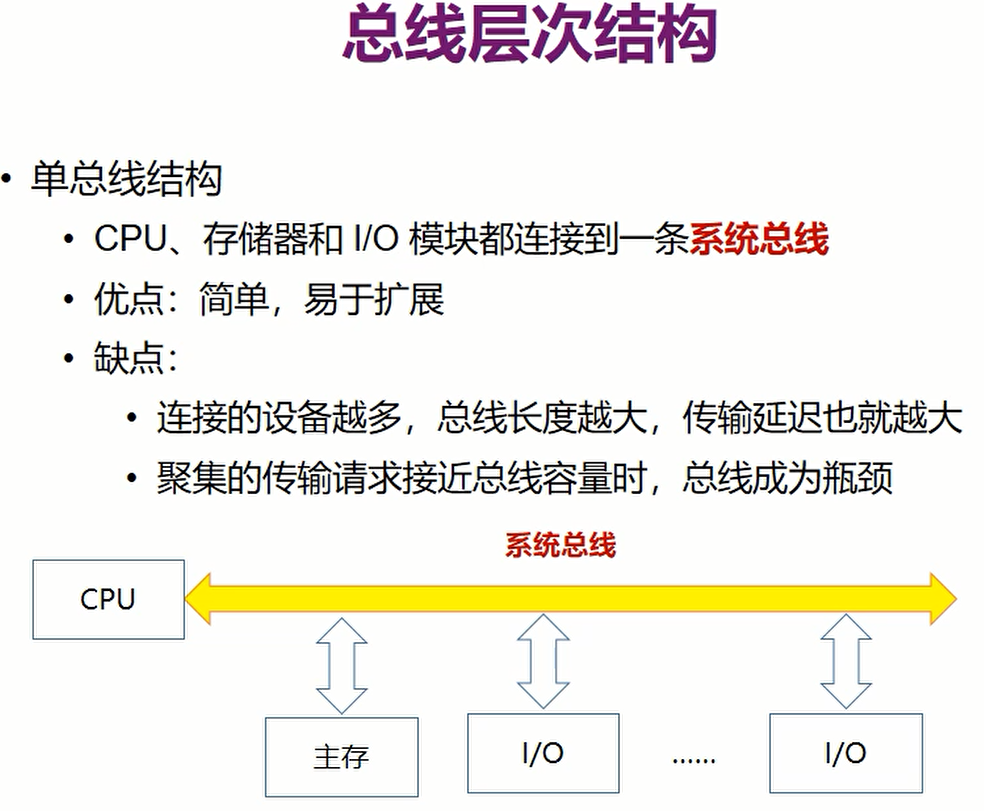

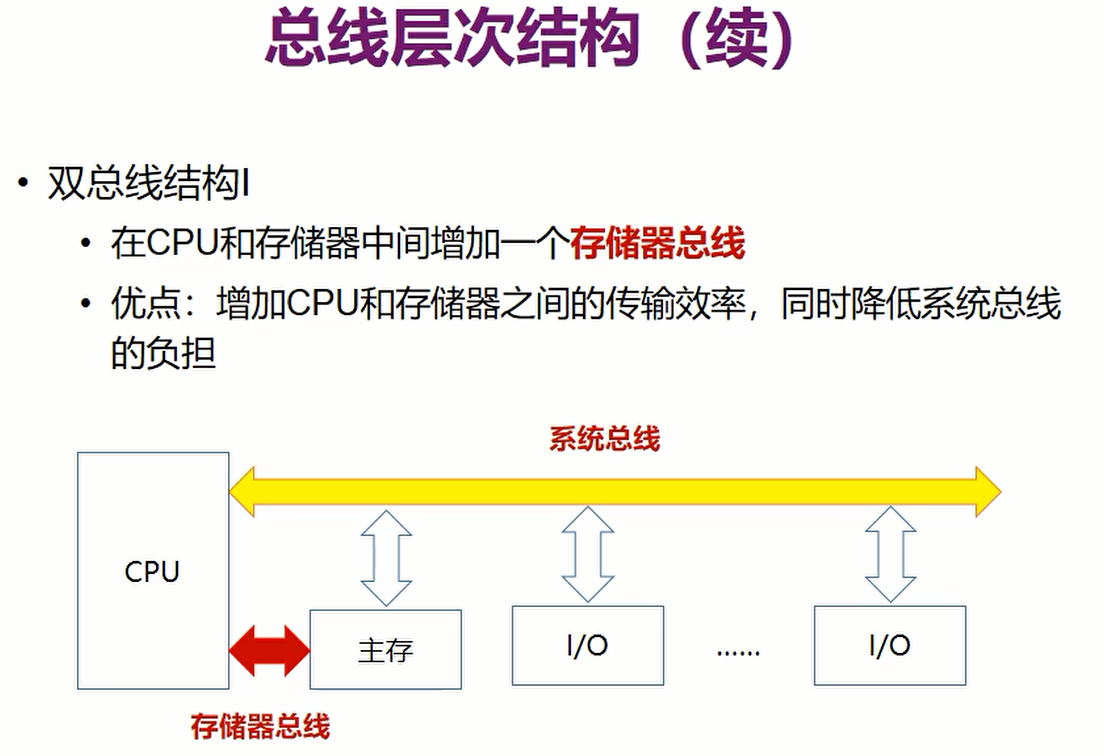

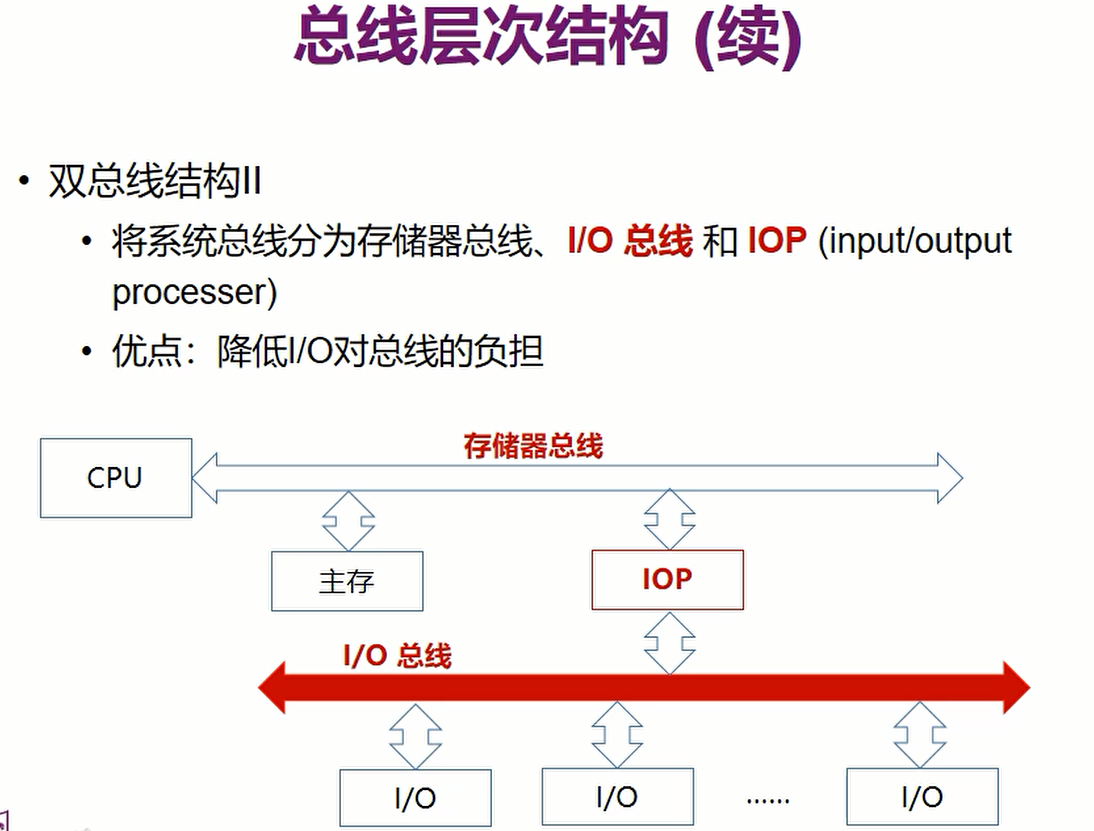

总线的层次结构

总线主要讨论CPU、主存、IO之间的连接和数据传输

单总线结构

双总线结构1

双总线结构2

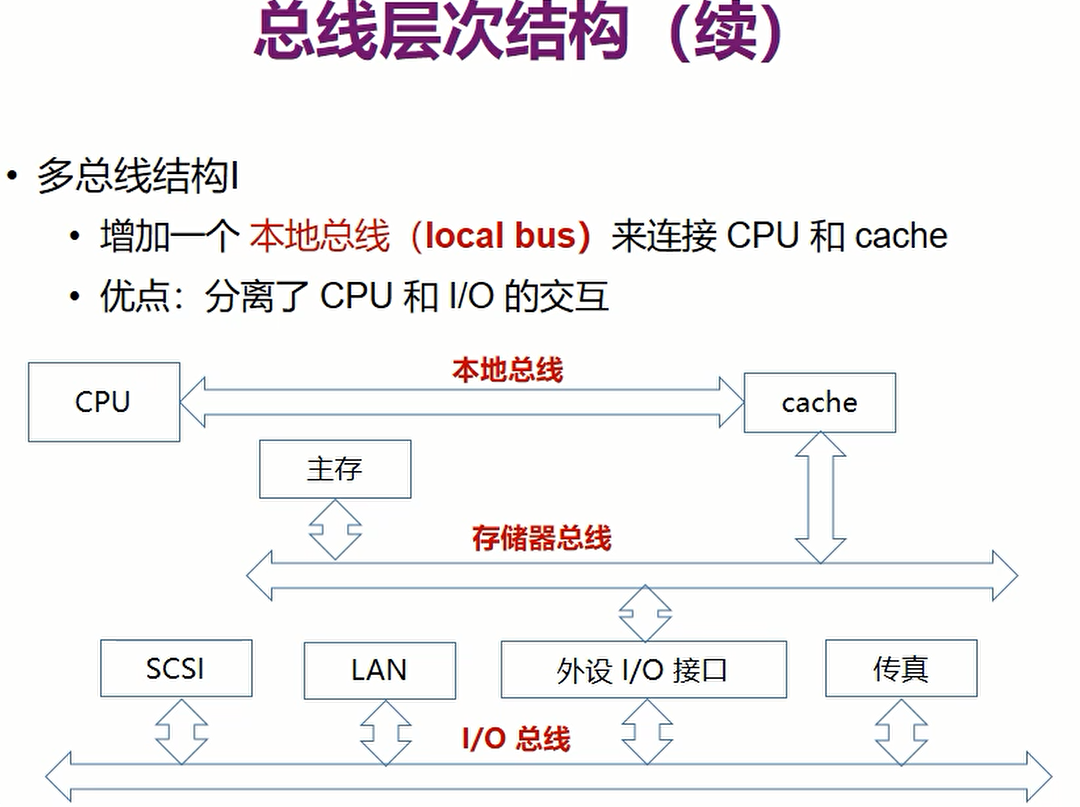

#### 多总线结构1

这种情况是cache还设计在CPU外,与之分离的时候的总线结构,当cache合并到CPU中时,就是内部总线了,而不存在上面的本地总线

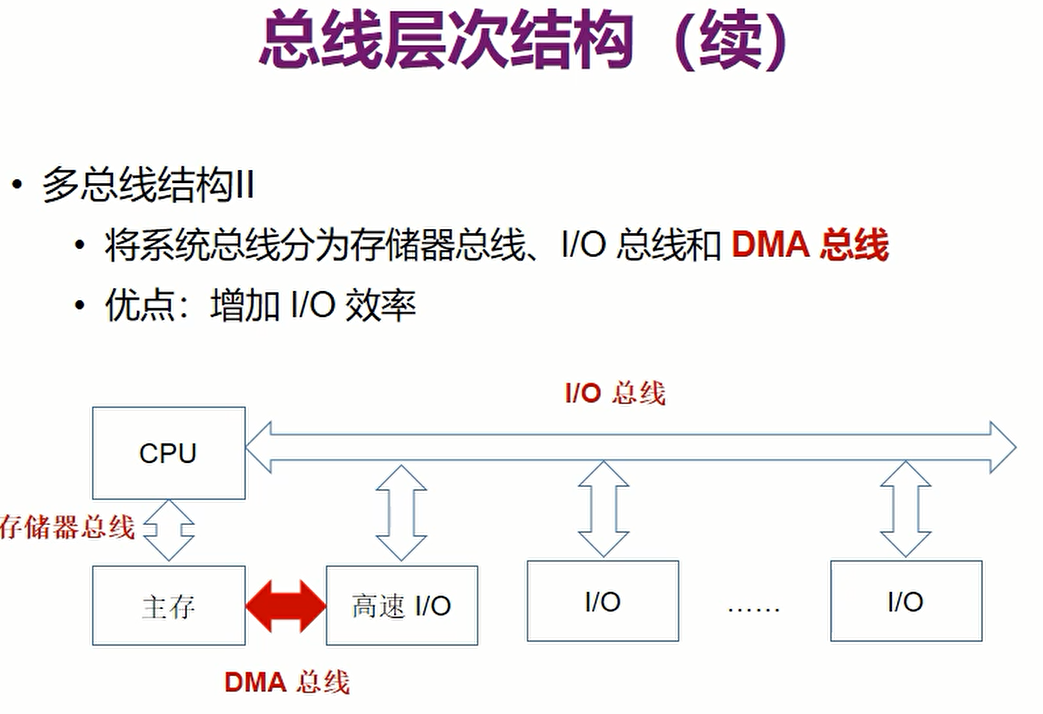

多总线结构2

从外部输入的数据可以直接存入主存,而不需要经过CPU

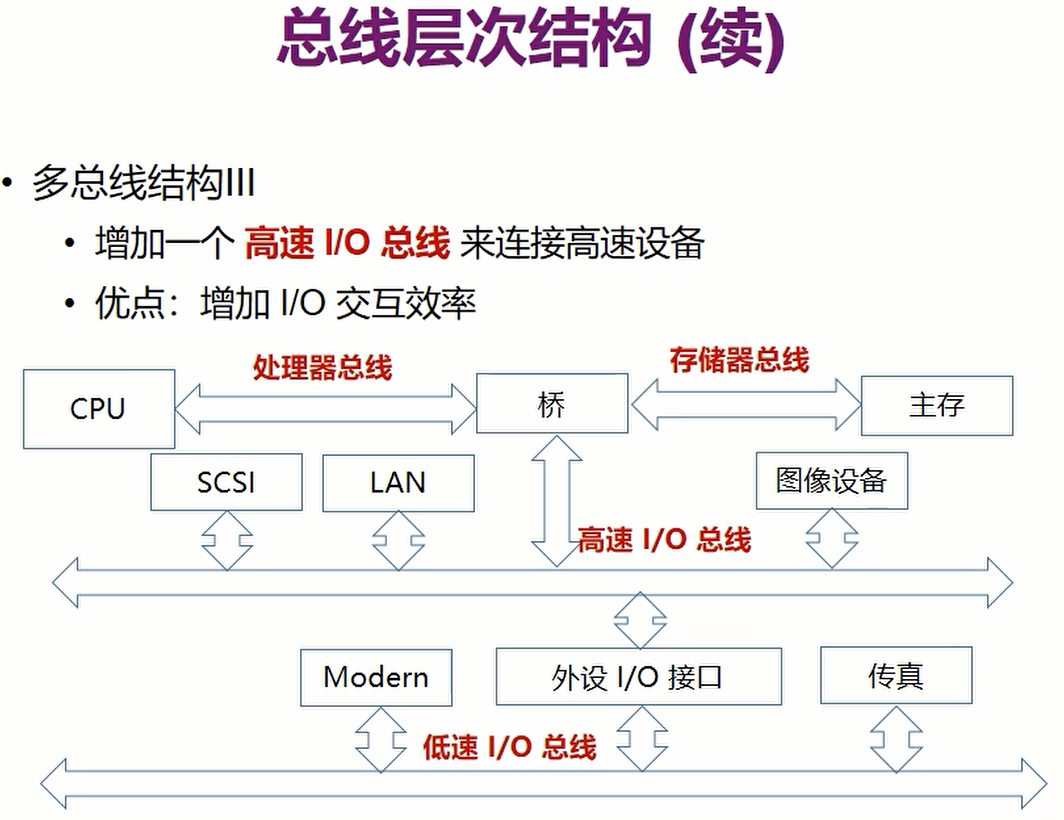

多总线结构3

总结

总线的巨大缺点是一次只能有一个数据在总线上,如果多个,那么会出错

多总线结构2

[外链图片转存中…(img-jYPA1TBZ-1656915352540)]

从外部输入的数据可以直接存入主存,而不需要经过CPU

多总线结构3

[外链图片转存中…(img-fZyxkqDK-1656915352540)]

总结

[外链图片转存中…(img-vXg8ejdN-1656915352541)]

总线的巨大缺点是一次只能有一个数据在总线上,如果多个,那么会出错

358

358

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?