1、SPI 介绍

SPI(串行外设接口)是一种由摩托罗拉公司开发的同步串行通信协议,主要用于短距离、高速通信的场景(如芯片间通信)。其核心特点是主从架构、全双工通信和硬件简单,广泛应用于嵌入式系统中连接微控制器(MCU)与传感器、存储器(如 EEPROM Flash)、显示屏、实时时钟和网络控制器等外设。

SPI 接口提供两个主要功能,支持 SPI 协议或 I2S 音频协议。默认情况下,选择的是 SPI 功能。可通过软件将接口从 SPI 切换到 I2S。

1.1、SPI 协议的核心机制

SPI 协议基于 4 根信号线实现通信:

- SCLK(Serial Clock):主设备生成的时钟信号,用于同步数据传输。

- MOSI(Master Out Slave In):主设备发送数据到从设备的信号线。

- MISO(Master In Slave Out):从设备发送数据到主设备的信号线。

- SS/CS(Slave Select/Chip Select):主设备通过拉低该信号线选择目标从设备(每个从设备独立一根 SS/CS 线)。

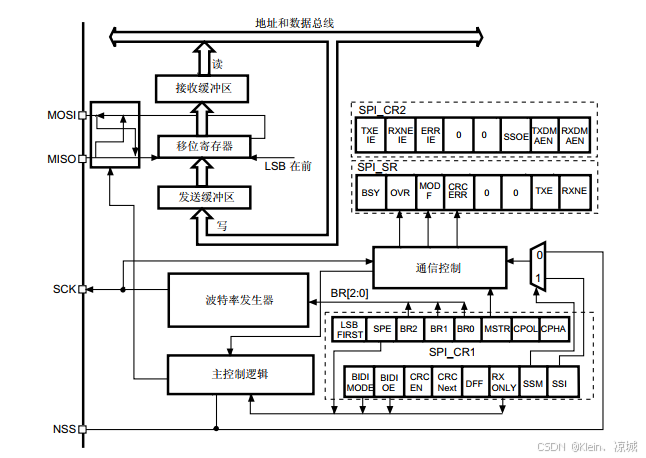

下图即是 SPI 框图:

1.2、通信过程

1、主设备通过拉低对应从设备的 SS/CS 线激活通信。

2、主设备生成 SCLK 时钟信号。

3、数据通过 MOSI 和 MISO 线同时传输(全双工):

- 主设备通过 MOSI 发送数据,从设备通过 MISO 返回数据。

- 每个时钟周期传输 1 位数据(MSB 或 LSB 优先,由设备配置决定)。

4、传输完成后,主设备拉高 SS/CS 线结束通信。

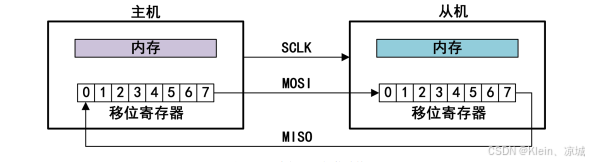

主机和从机都有一个移位寄存器,主机移位寄存器数据经过 MOSI 将数据写入从机的移位寄存器,此时从机移位寄存器的数据也通过 MISO 传给了主机,实现了两个移位寄存器的数据交换。无论主机还是从机,发送和接收都是同时进行的,如同一个“环”。

如果主机只对从机进行写操作,主机只需忽略接收的从机数据即可。如果主机要读取从机数据,需要主机发送一个空数据来引发从机发送数据。

1.3、SPI 的四种工作模式

SPI 模式由时钟极性(CPOL)和时钟相位(CPHA)的组合定义,决定数据采样时机:

| 模式 | CPOL | CPHA | 空闲时SCLK电平 | 数据采样时机 | 数据锁存时机 |

| 0 | 0 | 0 | 低电平 | SCLK的上升沿(第1个边沿) | SCLK的下降沿(第2个边沿) |

| 1 | 0 | 1 | 低电平 | SCLK的下降沿(第2个边沿) | SCLK的上升沿(第1个边沿) |

| 2 | 1 | 0 | 高电平 | SCLK的下降沿(第1个边沿) | SCLK的上升沿(第2个边沿) |

| 3 | 1 | 1 | 高电平 | SCLK的上升沿(第2个边沿) | SCLK的下降沿(第1个边沿) |

关键参数解释:

1、CPOL(Clock Polarity):

- 0:SCLK 空闲时为低电平。

- 1:SCLK 空闲时为高电平。

2、CPHA(Clock Phase):

- 0:在第一个边沿(上升或下降)采样数据。

- 1:在第二个边沿(上升或下降)采样数据。

1.3.1、模式 0 (CPOL=0 & CPHA=0)

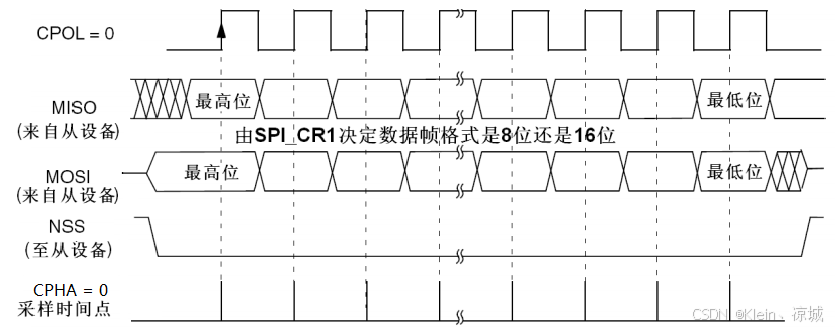

下图即是 SPI 模式 0 的时序图:

由于配置了 CPOL = 0,可以看到当数据未发送或者发送完毕, SCL 的状态是低电平,再者 CPHA = 0 即是奇数边沿采集。所以传输的数据会在奇数边沿上升沿被采集, MOSI 和 MISO 数据的有效信号需要在 SCK 奇数边沿保持稳定且被采样,在非采样时刻, MOSI和 MISO 的有效信号才发生变化。

1.3.2、模式 1 (CPOL=0 & CPHA=1)

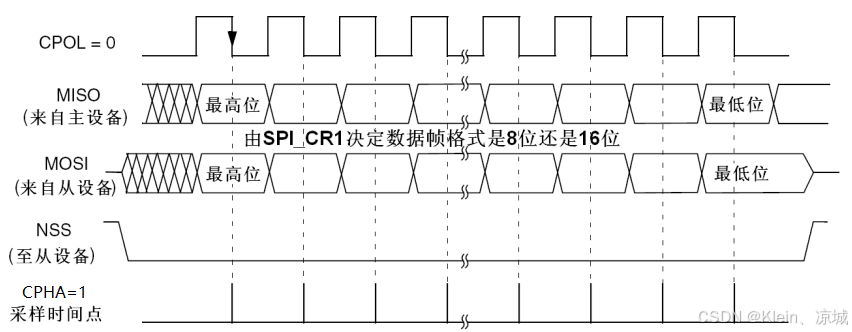

下图即是 SPI 模式 1 的时序图:

由于 CPOL = 0,所以 SCL 的空闲状态依然是低电平, CPHA = 1 数据就从偶数边沿采样,也就是下降沿。此处需要明确这里是偶数边沿采样,那么从时序图可以清楚地知道 SCL 低电平空闲状态下,上升沿是在奇数边沿上,下降沿是在偶数边沿上。

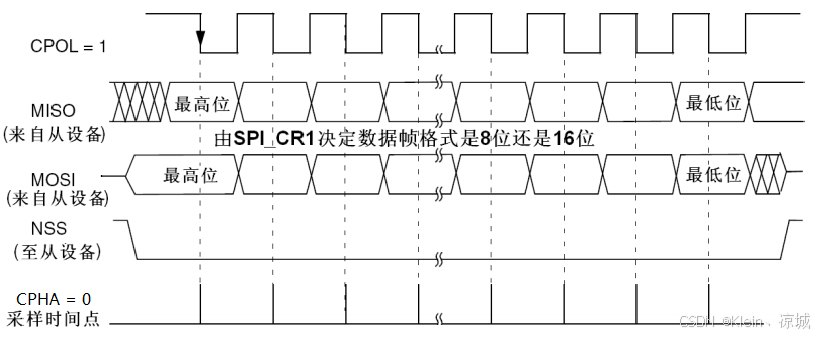

1.3.3、 模式 2 (CPOL=1 & CPHA=0)

下图即是 SPI 模式 2 的时序图:

这里是 CPOL = 1,即 SCL 空闲状态为高电平,在 CPHA = 0,奇数边沿采样的情况下,数据在奇数边沿下降沿要保持稳定并等待采样。

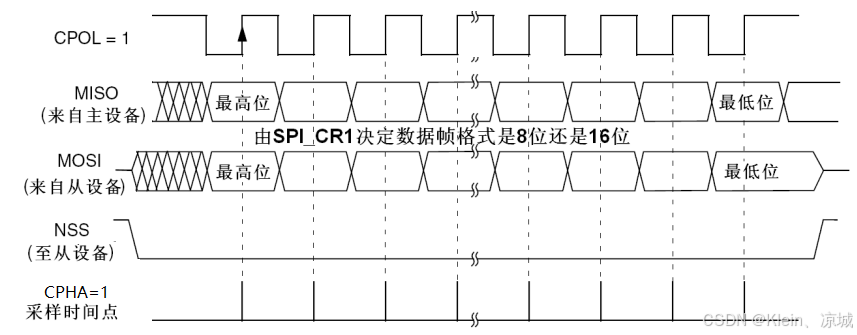

1.3.4、模式 3 (CPOL=1 & CPHA=1)

下图即是 SPI 模式 3 的时序图:

从时序图可以看到未发送数据和发送数据完毕,SCL 的状态是高电平,奇数边沿的边沿极性是上升沿,偶数边沿的边沿极性是下降沿。因为 CPHA = 1,所以数据在偶数边沿上升沿被采样。在奇数边沿的时候 MOSI 和 MISO 会发生变化,在偶数边沿时候是稳定的。

2、SPI 配置

2.1、 GPIO 初始化

首先是需要定义引脚,及控制 SCK 引脚的高低电平宏定义、片选线 CS 的高低电平宏定义:

/* SPI 引脚定义 */

#define SPI_SCK_PIN GPIO_Pin_5

#define SPI_MISO_PIN GPIO_Pin_6

#define SPI_MOSI_PIN GPIO_Pin_7

#define SPI_PORT GPIOA

#define W25Q128_CS_PIN GPIO_Pin_13

#define W25Q128_CS_PORT GPIOC

/* 控制引脚线电平高低 */

#define SPI_SCK_H() GPIO_SetBits(SPI_PORT, SPI_SCK_PIN)

#define SPI_SCK_L() GPIO_ResetBits(SPI_PORT, SPI_SCK_PIN)

#define W25Q128_CS_H() GPIO_SetBits(W25Q128_CS_PORT, W25Q128_

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1090

1090

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?