1.真值表

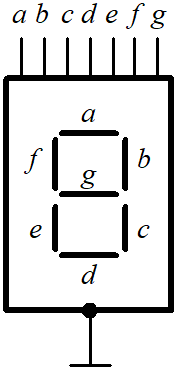

2.管脚图

3.VHDL语言

library ieee;

use ieee.std_logic_1164.all;

entity decoder7 is

port(d : in std_logic_vector(3 downto 0);

x : out std_logic_vector(6 downto 0));

end decoder7;

architecture behave of decoder7 is

begin

with d select

x <= "1111110" when "0000", --选择信号赋值语句

"0110000" when "0001",

"1101101" when "0010",

"1111001" when "0011",

"0110011" when "0100",

"1011011" when "0101",

"1011111" when "0110",

"1110000" when "0111",

"1111111" when "1000",

"1111011" when "1001",

"0000000" when others;

end behave;

4644

4644

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?