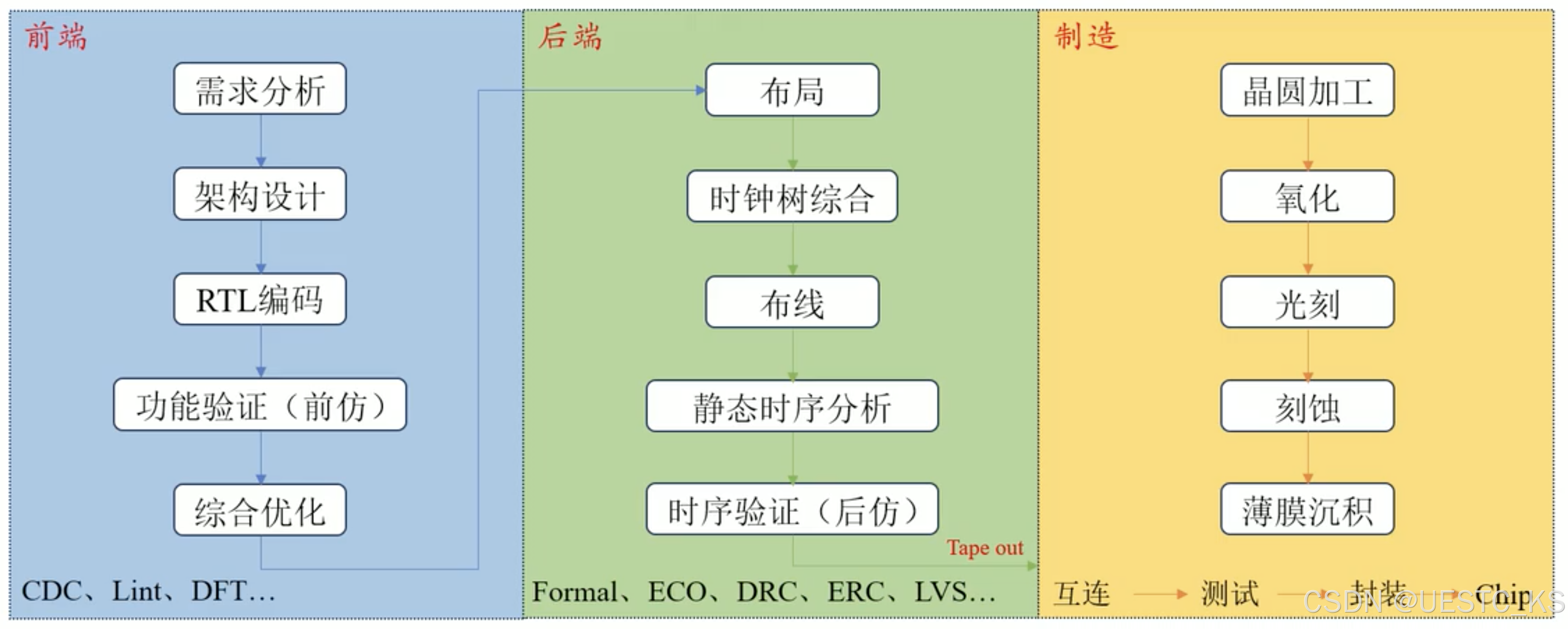

基于标准单元库的SOC设计流程

标准单元库包括版图库、符号库、电路逻辑库等。包含了组合逻辑、时序逻辑、功能单元和特殊类型单元。一般所有的芯片制造厂商会针对每个工艺提供相应的标准单元库。设计基于标准单元库的SOC时,设计人员通常需要进行如下的设计步骤。

(1)模块集成

模块集成指把SoC硬件部分中所有具有不同功能的模块集成到一起,形成一个完整硬件设计的过程。在该过程中,需要明确哪些模块或架构可以通过技术迭代实现,哪些模块需要进行复用,哪些关键模块需要IP授权或自主研发。模块集成通常基于硬件描述语言完成。

(2)前仿真

前仿真一般又称为功能仿真或寄存器转换级(Register Transfer Level, RTL)的电路仿真,其目的是基于硬件描述语言仿真器判断模块集成的结果是否符合需求规格说明中的功能要求。其中 RTL 是一种针对数字集成电路的高级抽象层次,在RTL.级中,设计者不再关注时序逻辑和组合逻辑的连接关系与数量,而仅仅描述寄存器至寄存器之间的逻辑功能,Verilog HDL 与VHDL 均为RTL的硬件描述语言。

(3)逻辑综合

逻辑综合指开发人员借助EDA 工具将完成前仿真的硬件设计转换成特定工艺下的门级网表。门级是比 RTL更低、更具体的层级,门级网表记录了设计中所有逻拜货源之间的互联关系。因此,在进行逻辑综合时,我们需要对设计的时序、面积、功耗等具体参数进行约束。

(4)版图布局规划

版图布局规划完威的主要任务是界定并优化设计中所有模块的定位,主要分为I/O规划、模块布置设计和电源设计。其中I/O规划主要是规划I/O、电源和连接口的地址;模块布置设计是定义各种组件和部分区域中的模块,并加以合理布置;电源设计则是设计完整的版图式电源网路,并对其进行拓扑优化。

(5)功耗分析(Power Network Analysis,PNA)

在设计过程中的多个生骤均可利用BDA工具对设计的功耗进行分析,从而指导设计的技术选代。在版图布局规划完成后,可对电源网络进行功耗分析,以决定电源线参数与电源引脚位置。在完成版图布线设计后,还可进行全版图的动态功耗和静态功耗分析。

(6) 静态时序分析

静态时序分析技术是一种通过穷举法对电路中所有路径延迟信息进行提取、分析的步骤。通过静态时序分析,可以发现时序约束的违例情况。由于静态时序分析不依赖外部激励,且可以对全部设计进行穷举检查,因此静态时序分析是SOC设计流程中的一项重要步骤,在逻辑综合和布局布线后均需要进行静态时序分析以进行检查。

(7) 形式验证

形式验证是一种针对逻辑功能的等效性检查。形式验证可根据两个电路的结构判断其逻辑功能是否等效。由于EDA工具通常具备一定的自动优化能力,因此在借助 EDA 工具进行SoC设计时,EDA工具常常会自行对设计进行优化修改。与此同时,SoC开发过程中的人为技术送代同样不可避免。为保证设计的一致性,整个设计流程中会多次引人形式验证。

(8)可测性设计

在SoC设计中,可测性设计是非常关键的过程。对于逻辑电路,通常会使用扫描链的可测试架构,而对于芯片的输人/输出接口,则通常使用边界扫描的可测试架构。

(9)布线

布线用来实现电路中全部节点的连接,布线分为全局布线与详细布线。在布局完成后,通常首先使用全局布线提取大致的时序信息,并将时序信息反标至网表中用来进行静态时序分析。当静态时序分析检查无误后,最后进行详细布线。

(10)提取寄生参数

寄生参数指版图上由于内部互连所导致的寄生电容和寄生电阻,寄生参数在SoC设计的初级阶段是无法获取的。实际上寄生参数被提取后将会被转换为标准的延迟格式反标至设计中,进行布局布线后的静态时序分析和后仿真。

(11)后仿真

后仿真也被称为时序仿真、门级仿真。基于布局布线后所获得的精确延迟参数,生成标准延时文件(Standard Delay Format, SDF),再次针对门级网表进行仿真,以验证网表的功能是否依然符合设计要求。

(12) 物理验证

物理验证一般包括针对版图的设计规则检验(Design Rule Check, DRC)、针对版图网表与逻辑网表的比较(Layout VS Schematie,LVS)和电气规则检查(Electrical Rule Checking,ERC)。其中,DRC一般用来检查接线距离和接线长度等情况能否达到工艺规定,用于保证设计在流片过程中的良率,LVS 用于确认版图网表结构是否与设计一致,ERC负责检测故障和开路等电器法规违例现象。

(13)流片

完成全部设计的版图最终转换为 GDSII文件,提交至制造厂进行芯片生产一流片(Tapeout)。

一般数字集成电路设计流程如下框图

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?