1.1设计思路

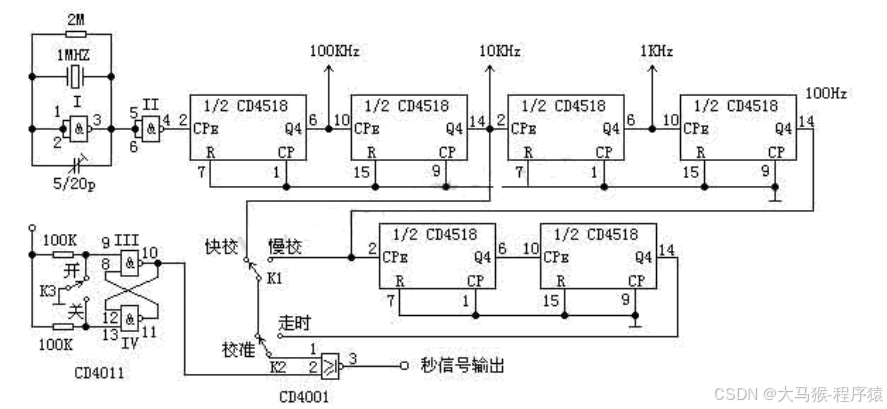

1秒脉冲发生器: 秒脉冲信号发生器需要产生一定精度和幅度的矩形波信号。实现这样矩形波的方法很多,可以由非门和石英振荡器构成,可由单稳态电路构成,可以由施密特触发器构成,也可以由555定时器构成等。

不同的电路队矩形波频率的精度要求不同,由此可以选用不同电路结构的脉冲信号发生器。本实验中由于脉冲信号作为计数器的计时脉冲,其精度直接影响计数器的精度,因此要求脉冲信号有比较高的精度。一般情况下,要做出一个精度比较高的频率很低的振荡器有一定的难度工程上解决这一问题的办法就是先做一个频率比较高的矩形波震荡器,然后将其输出信号通过计数器进行多级分项,就可以得到频率比较低 精度比较高的脉冲信号发生器,其精度取决于振荡器的精度和分级项数。

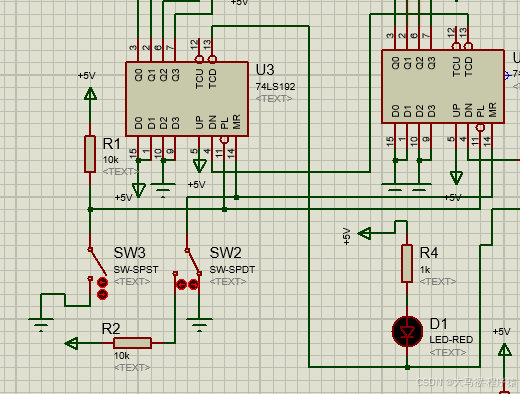

2.24秒减法计数器:24秒减法计数器采用74LS192设计,74LS192是十进制同步加法|减法计数器,采用8421BCD码编码,具有直接清零 异步置数功能。

74LS192的逻辑功能表如下:

| CPU | CPD | LD'

| CR | 操作 |

| × | × | 0 | 0 | 置数 |

| ↑ | 1 | 1 | 0 | 加计数 |

| 1 | ↑ | 1 | 0 | 减计数 |

| × | × | × | 1 | 清零 |

3.控制电路 按照系统的要求,电路应该完成以下4个功能;

1)当操作直接清零按键时,要求计数器清零。

2)当启动按键闭合时,首先将定时器校准为24秒,控制电路应封锁时钟信号CP(秒脉冲信号),同时计数器完成置数功能,显示器显示24秒字样。当启动按键释放时,计数器开始减法计数。

3)当暂停连续开关处于暂停状态时,控制电路封锁计数脉冲,计数器停止计数,显示器显示原来的数,而且保持不变,当暂停连续开关处于连续状态时,计数器正常计数,另外,外部操作开关都应该采取消抖措施,以防止机械抖动造成电路工作不稳定。

4)当计数器递减到零时,控制电路输出报警信号,计数器保持状态不变。

2方案设计与论证

2.1时间脉冲产生电路

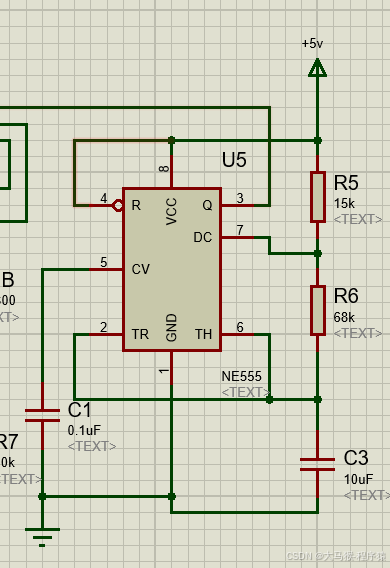

方案一:由集成电路定时器555与RC组成的多谐振荡器作为时间标准信号源。

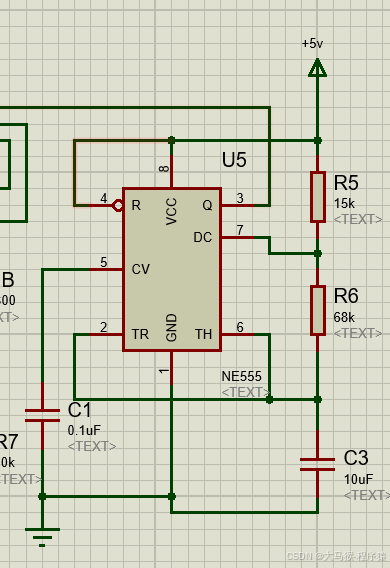

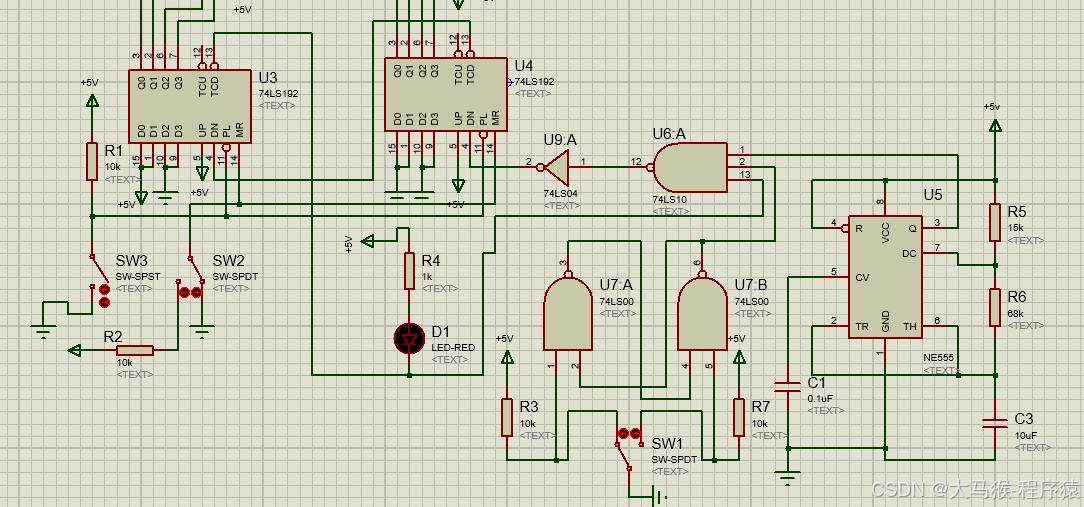

图 2 555与RC组成的多谐振荡器

方案二:由14位二进制串行计数器/分频器和振荡器CD4060、BCD同步加法计数器CD4518构成的秒信号发生器。

电路中利用CD4060组成两部分电路。一部分是14级分频器,其最高分频数为16384;另一部分是由外接电子表用石英晶体、电阻及电容构成振荡频率为32768Hz的振荡器。震荡器输出经14级分频后在输出端Q14上得到1/2秒脉冲并送入由1/2 CD4518构成的二分频器,分频后在输出断Q1上得到秒基准脉冲。

方案选择:

本课程设计中对秒脉冲信号的精度要求并不是很高,并且方案二中用CD4060和分频器构成的基准秒脉冲发生电路较于前者要复杂的多,而且CD4060和CD4518我们平常很少用,对其功能和引脚信息了解不多,所以,我们选用了方案一,用555定时器构成电路中的脉冲信号发生器。

2.2控制电路

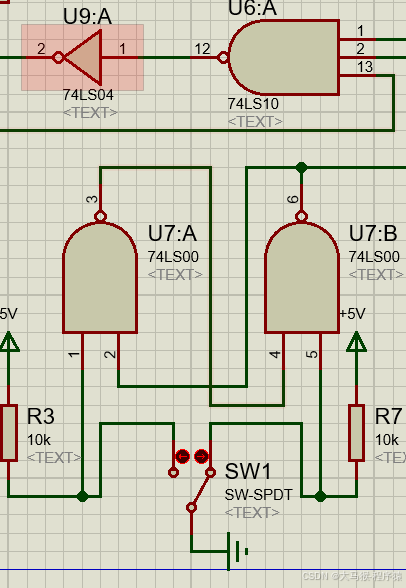

(1) 暂停/连续控制电路

电路中通过外部操作开关控制脉冲信号的连续与暂停来实现整个电路的连续与暂停功能。通过开关控制高低电平的接入,进而控制秒脉冲是否接入计数器,从而达到暂停和连续的功能。原理图如下所示。

(2) 置数/启动/清零复位控制电路

利用单刀双掷开关一端接地一端接电源,控制给计数电路的复位清零引脚接入高低电平。

2.3计数电路

在数字系统中使用的最多的时序电路要算是计数器了。计数器不仅能用于对时钟脉冲计数,还可以用于分频、定时、产生节拍脉冲和脉冲序列以及进行数字运算等。

计数器的种类非常多。如果按计数器中的触发器是否同时翻转分类,可以将计数器分为同步式和异步式两种。在同步计数器中,当时钟脉冲输入时触发器的翻转是同时发生的。而在异步计数器中,触发器的翻转由先有后,不是同时发生的。在设计中我们选择的是同步加/减计数器74LS192。它是双时钟同步可逆计数器,是8421BCD码计数,其详细引脚图及功能表如下:

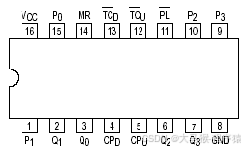

图3.3.1 74LS192引脚图

表3.3.1 74LS192功能表

| 输入 | 输出 | ||||||||||

| CR | LD | CPU | CPD | D3 | D2 | D1 | D0 | Q3 | Q2 | Q1 | Q0 |

| 1 | X | X | X | X | X | X | X | O | 0 | 0 | 0 |

| 0 | 0 | X | X | d | c | b | a | d | c | b | a |

| 0 | 1 | 1 | 1 | X | X | X | X | 保持 | |||

| 0 | 1 |

| 1 | X | X | X | X | 加计数 | |||

| 0 | 1 | 1 |

| X | X | X | X | 减计数 | |||

表中CR是清零端,LD是置数端,CPU是加计数时钟输入端,CPD是减计数时钟输入端,D3﹑D2﹑D1﹑D0DO都是计数器预置数输入端,Q3﹑Q2﹑Q1﹑Q0都是数据输出端,另外,C0是非同步进位输出端,BO是非同步借位端输出端。

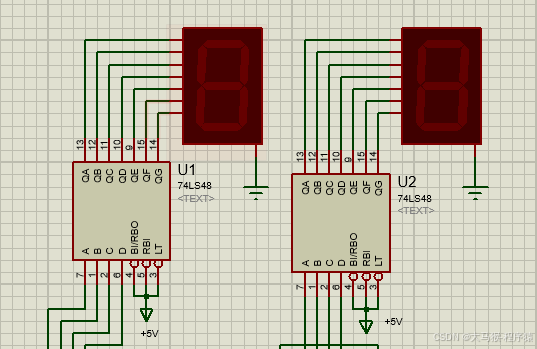

2.4译码驱动及显示单元电路

BCD码七段译码驱动器型号有74LS47(共阳)74LS48(共阴)、CD4511(共阴)等,本设计采用的是74LS48。

其中A-D为BCD码输入端;a-g为译码输出端,输出“1”有效,用来驱动LED共阴数码管;LT’为测试输入端,LT’=0时,译码输出全为“1”;BI’为消隐输入端,BI’=0,译码输出端全为“0”;LE为锁定端,LE=1时译码器处于锁定状态,译码输出端保持在LE=0时的数值,LE=0为正常译码。

74LS48内有上拉电阻,故只需要在输出端与数码管管脚端之间串入限流电阻即可工作。译码器还有拒伪码功能,当输入码超过1001时,输出全为“0”,数码管熄灭。

2.5 报警电路

设计中要求电路在计数为0时实现光电报警的功能。设计方案中发光二极管实现了这一功能。电路图如下图。

当高位计数器的数值减到0时,向前借位借口~BO又高电平变为低电平,有点路可知这是LED二极管亮,达到光电报警的作用。

3单元电路的设计

3.1时间脉冲产生电路的设计

产生1Hz时间脉冲的电路图

由于R5=15kΩ,R6=68kΩ,C1=0.1uF,C3=10uF,因为T=(R1+2R2)C㏑2 ,算得T=1.008s

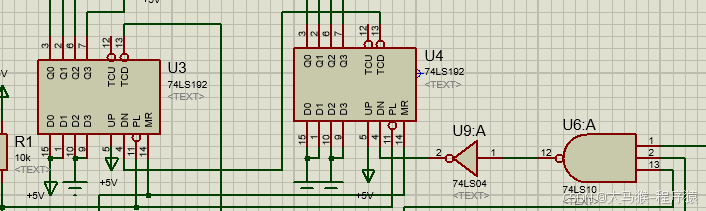

3.2计数电路的设计

24秒计时器,只需要进行单一的递减计算,所以在设计中我选择的是同步加/减计数器74LS192。它是双时钟同步可逆计数器,是8421BCD码计数。

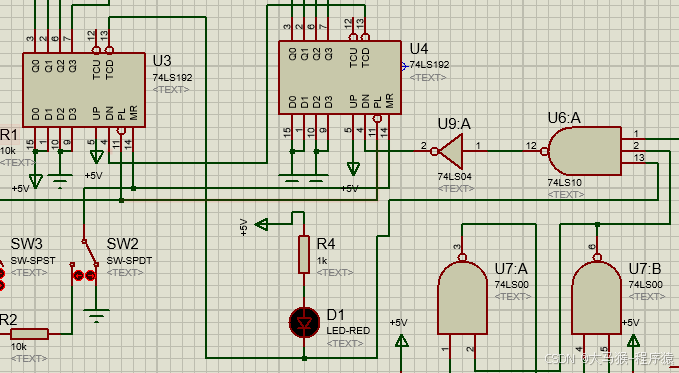

设计中通过两片74LS192的级联来实现一个24进制的计数器。当低位片从0跳到9时,高位片进位加一,直到实现二十四秒的计数功能。再者,因为要求中提到要求电路要实现倒数计时,所以74LS192的加计数器信号输入当应该加上无用性号(高电平)。计数电路的核心是置数部分。本设计中的30秒只需将两计数器的输入端分别置为0010和0101即可,采用同步置数的方式来实现24置数。因为74LS192是十进制的计数器,所以当倒计时为0时,计数器会跳到99,因此我们采用99置数来解决这个问题,最后让显示器停在24秒处。计数电路如下:

3.3 控制电路的设计

控制电路如上图所示,包括暂停/连续控制电路和置数/启动控制电路来实现整个装置的暂停计数和继续计数,重新置数和启动计数的功能。当B开关置于置数位置时,不管C置于哪端都不开始计数;当B开关置于启动端时,开关C至于连续端时开始计数,开关C至于暂停端时计数暂停。

3.4 译码及驱动显示电路

译码电路的功能是将计数器的输出代码进行翻译,变成相应的数字。用于驱动LED七段数码管的译码器常用的有74LS48。74LS48是BCD-7段译码器/驱动器,其输出是OC门输出且低电平有效,专用于驱动LED七段共阳极显示数码管。如图9所示。若将计数器的每位输出分别接到相应七段译码器的输入端,便可进行不同数字的显示。

5774

5774

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?