CRC(循环冗余校验)原理及Verilog代码

CRC(循环冗余校验)介绍

CRC(循环冗余校验)是一种常用的错误检测码,广泛应用于数据通信和存储系统中,用于检测数据传输过程中是否发生了错误。CRC校验通过在数据流中附加校验位(余数)的方式实现错误检测,具有高效性和可靠性。

下面是CRC校验的详细原理和步骤:

①生成多项式:CRC校验使用一个固定的生成多项式来进行计算。生成多项式通常表示为一个二进制数,如1011。

②数据处理:在数据发送端,需要将待发送的数据(比特流)与一定数量的零比特序列相连,以确保数据位数能够容纳生成多项式的位数。

③除法运算:将上一步得到的数据比特序列作为被除数,生成多项式作为除数,进行模2除法运算,即逐位异或操作。

④余数附加:将得到的余数添加到原始数据后面,形成带有CRC校验位的数据。

⑤数据传输:发送端将带有CRC校验位的数据发送给接收端。

⑥接收端校验:接收端接收到数据后,同样进行除法运算,并得到一个余数。如果接收端得到的余数为0,说明数据传输过程中没有出现错误;如果余数不为0,则说明数据可能存在错误。

CRC校验具有以下优点:

高效:CRC校验可以快速计算,适用于高速数据传输。

可靠性:CRC校验能够检测多种常见的传输错误,如单比特翻转、奇数个比特错误等。

灵活性:可以根据需求选择不同的生成多项式,以适应不同的数据传输环境。

总的来说,CRC校验是一种简单而有效的错误检测方法,被广泛用于数据通信领域,提高了数据传输的可靠性和稳定性。

CRC原理

(1)先选择(可以随机选择,也可按标准选择,具体在后面介绍)一个用于在接收端进行校验时,对接收的帧进行除法运算的除数(是二进制比较特串,通常是以多项方式表示,所以CRC又称多项式编码方法,这个多项式也称之为“生成多项式”)。

(2)看所选定的除数二进制位数(假设为k位),然后在要发送的数据帧(假设为m位)后面加上k-1位“0”,然后以这个加了k-1个“0“的新帧(一共是m+k-1位)以“模2除法”方式除以上面这个除数,所得到的余数(也是二进制的比特串)就是该帧的CRC校验码,也称之为FCS(帧校验序列)。但要注意的是,余数的位数一定要是比除数位数只能少一位,哪怕前面位是0,甚至是全为0(附带好整除时)也都不能省略。

(3)再把这个校验码附加在原数据帧(就是m位的帧,注意不是在后面形成的m+k-1位的帧)后面,构建一个新帧发送到接收端;最后在接收端再把这个新帧以“模2除法”方式除以前面选择的除数,如果没有余数,则表明该帧在传输过程中没出错,否则出现了差错。

通过以上介绍,大家一定可以理解CRC校验的原理,并且不再认为很复杂吧。

从上面可以看出,CRC校验中有两个关键点:一是要预先确定一个发送端和接收端都用来作为除数的二进制比特串(或多项式);二是把原始帧与上面选定的除进行二进制除法运算,计算出FCS。前者可以随机选择,也可按国际上通行的标准选择,但最高位和最低位必须均为“1”,如在IBM的SDLC(同步数据链路控制)规程中使用的CRC-16(也就是这个除数一共是17位)生成多项式g(x)= x16 + x15 + x2 +1(对应二进制比特串为:11000000000000101);而在ISO HDLC(高级数据链路控制)规程、ITU的SDLC、X.25、V.34、V.41、V.42等中使用CCITT-16生成多项式g(x)= x16 + x15 + x5+1(对应二进制比特串为:11000000000100001)。

CRC校验码的计算示例

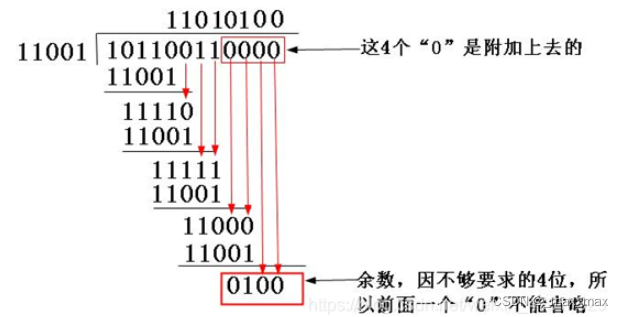

(1)首先把生成多项式转换成二进制数,由G(X) = X4 + X3 + 1可以知道(,它一共是5位(总位数等于最高位的幂次加1,即4+1=5),然后根据多项式各项的含义(多项式只列出二进制值为1的位,也就是这个二进制的第4位、第3位、第0位的二进制均为1,其它位均为0)很快就可得到它的二进制比特串为11001。

(2)因为生成多项式的位数为5,根据前面的介绍,得知CRC校验码的位数为4(校验码的位数比生成多项式的位数少1)。因为原数据帧10110011,在它后面再加4个0,得到101100110000,然后把这个数以“模2除法”方式除以生成多项式,得到的余数(即CRC码)为0100,如图所示。注意参考前面介绍的“模2除法”运算法则。

(3)把上步计算得到的CRC校验0100替换原始帧101100110000后面的四个“0”,得到新帧101100110100。再把这个新帧发送到接收端。

(4)当以上新帧到达接收端后,接收端会把这个新帧再用上面选定的除数11001以“模2除法”方式去除,验证余数是否为0,如果为0,则证明该帧数据在传输过程中没有出现差错,否则出现了差错。

通过以上CRC校验原理的剖析和CRC校验码的计算示例的介绍,大家应该对这种看似很复杂的CRC校验原理和计算方法应该比较清楚了。

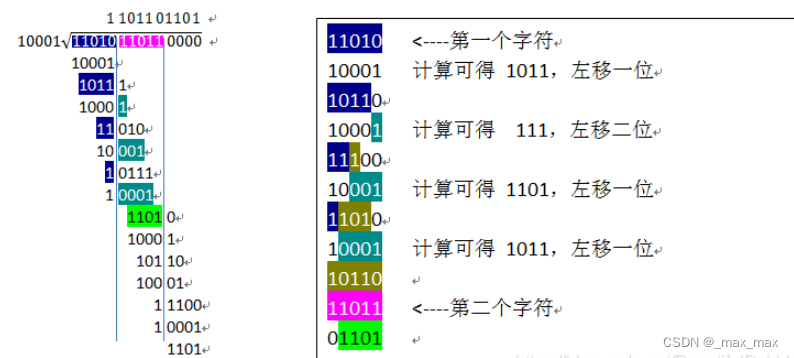

仔细观察计算的过程,可以发现其实每一次Xor都是固定不动的生成项与其对应的数据首位“消1”。那我们就可以假想出一个与生成项长度一致的“盒子”,取出一部分的数据出来若首位是1时就进行一次Xor,遇到0则左移到1为止,左移造成的右端的空缺用0补充。而这里0希望理解为一种“存储”,它“存储” 生成项中未和数据进行计算的那一部分,按顺序先后附加被计算数据的后面,当先一部分的数据全部计算之后,实际上“盒子”中剩下都是未和数据计算的部分的“和”11011 xor 10110 = 11011 xor ( 10000 xor 00100 xor 00010)(这里实际上就是Xor的交换律到后面就会体会到他的强大)。

Verilog实现

module crc_test(

input clk,

input rst,

input [7:0] data_in,

output reg[3:0] crc_out,

output reg crc_vld

);

parameter polynomial = 5'b11001;

localparam IDLE = 3'b001,

CRC = 3'b010,

DONE = 3'b100;

reg [11:0] temp = 0;

reg [2:0] state;

wire [11:0] signal_temp;

assign signal_temp = {data_in,4'b0};

always @ (posedge clk or posedge rst)begin

if(rst)begin

state <= IDLE;

crc_out <= 4'b0;

crc_vld <= 1'b0;

end

else case(state)

IDLE:begin

crc_out<= 4'b0;

crc_vld<= 1'b0;

temp <= signal_temp;

state <= CRC;

end

CRC:begin

state <= CRC;

crc_vld <= 1'b0;

if(temp[11]) temp[11:7] <= temp[11:7] ^ polynomial;

else if(temp[10])temp[10:6] <= temp[10:6] ^ polynomial;

else if(temp[9])temp[9:5] <= temp[9:5] ^ polynomial;

else if(temp[8])temp[8:4] <= temp[8:4] ^ polynomial;

else if(temp[7])temp[7:3] <= temp[7:3] ^ polynomial;

else if(temp[6])temp[6:2] <= temp[6:2] ^ polynomial;

else if(temp[5])temp[5:1] <= temp[5:1] ^ polynomial;

else if(temp[4])temp[4:0] <= temp[4:0] ^ polynomial;

else state<=DONE;

end

DONE:begin

crc_out <= temp[3:0];

crc_vld <= 1'b1;

state <= IDLE;

end

default : begin

crc_out <= 4'b0;

crc_vld <= 1'b1;

state <= IDLE;

end

endcase

end

endmodule

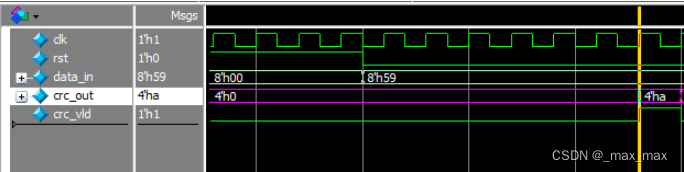

运行结果: 4’ha —>-4’b101

参考资料

CRC校验的Verilog自动生成

http://outputlogic.com/?page_id=321

5355

5355

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?