VCS & Verdi 联合仿真总结

一、VCS & Verdi 介绍

1.VCS介绍

VCS(Verilog Compilation and Simulation)是一种常用的Verilog编译和仿真工具,广泛应用于硬件设计和验证领域。它是Synopsys公司开发的一款商业化工具,提供了强大的功能和性能,被认为是业界的主流仿真工具之一。

VCS具有以下特点和功能:

- 编译器:VCS提供了高效的Verilog编译器,支持Verilog-1995、Verilog-2001和SystemVerilog语言标准。它能够将Verilog代码转换为可执行的仿真文件,并进行优化以提高仿真性能。

- 仿真器:VCS内置了高性能的仿真器,能够快速加载和执行编译后的仿真文件。它支持单线程和多线程仿真,可以在不同层次上对设计进行分层仿真,提供了丰富的调试和分析功能。

- 支持多个层次:VCS支持从单个模块到整个系统的多个层次的仿真。它能够处理包括RTL级别、门级级别和行为级别等各种层次的设计描述,并能够在不同层次之间进行仿真和调试。

- 高级调试功能:VCS提供了丰富的调试功能,包括信号波形查看、时序分析、变量跟踪、断点设置等。它还支持通过调试接口与其他EDA工具进行集成,方便进行综合、布局和时序分析等后续流程。

- 系统级仿真:VCS可以进行系统级仿真,支持多个模块之间的交互和通信。它能够处理复杂的设计结构,包括处理器、存储器、外设等,并能够模拟整个系统的行为和性能。

- 高度可配置:VCS提供了丰富的编译和仿真选项,可以根据设计需求进行灵活配置。它支持不同的仿真模式、优化选项、时钟域设置等,以满足各种验证和性能要求。

总结说,VCS是一个功能强大、性能高效的Verilog编译和仿真工具,被广泛应用于硬件设计和验证领域。它提供了丰富的功能和灵活的配置选项,能够满足不同层次、不同规模的设计仿真需求,并帮助工程师提高设计效率和验证准确性。

2.Verdi

Verdi是一种先进的交互式调试和仿真分析工具,用于硬件设计和验证领域。它由Synopsys公司开发,为设计工程师提供了强大的功能和直观的用户界面,帮助他们更高效地进行调试和验证。

Verdi具有以下特点和功能:

- 交互式调试:Verdi提供了一个直观的图形用户界面,使设计工程师能够以交互式的方式浏览和分析设计波形数据。它支持信号波形查看、变量跟踪、断点设置等调试功能,能够快速定位设计中的问题和错误。

- 灵活的波形查看:Verdi支持多种波形查看方式,包括波形图、列表、树状图等,可以根据需求选择最适合的显示方式。它还支持信号过滤、波形比较、波形标记等功能,方便用户对设计进行深入分析。

- 自定义布局和分析:Verdi允许用户自定义波形窗口布局,并支持多个窗口之间的交互和联动。它还提供了丰富的分析工具,如时序分析、状态机分析、层次分析等,帮助用户深入理解和验证设计的行为和性能。

- 高级调试功能:Verdi集成了先进的调试功能,如数据潜在问题的自动检测和报告、时序违规的分析和显示等。它还支持与其他EDA工具的集成,如仿真器、综合器、布局工具等,方便用户进行全面的设计流程调试和验证。

- 跨平台支持:Verdi可以在多个操作系统平台上运行,包括Windows和Linux等。这使得设计工程师可以根据自己的偏好选择合适的操作环境,并方便与团队成员进行共享和协作。

总的来说,Verdi是一款功能强大、易用性高的交互式调试和仿真分析工具。它提供了丰富的功能和直观的用户界面,帮助设计工程师快速定位和解决设计中的问题,并提高设计的准确性和可靠性。无论是对于小规模的设计还是复杂的系统级设计,Verdi都是一个不可或缺的工具。

3.VCS & Verdi个人认识

VCS仿真可看作两步:

①Compilation 编译:编译是仿真设计的第一步。在这个阶段,VCS 构建实例层次结构并生成一个二进制可执行文件 simv。这个二进制可执行文件稍后将用于仿真。

②Simulation 仿真:在编译过程中,VCS生成一个二进制可执行文件simv。可以使用 simv 来运行仿真。

VCS & Verdi用于前仿真,如果要后仿真,则可用DC工具。

二、VCS & Verdi常用的编译指令

常见的编译命令如下:

- -v lib_file:lib_file 是 Verilog 文件,包含了引用的 module 的定义,可以是绝对路径,也可以是相对路径。

- -y lib_dir:lib_dir 是参考库的目录,vcs 从该目录下寻找包含引用的 module 的 Verilog 文件,这些文件的文件名必须和引用的 module 的名一样。

- -f file_list.f:file_list.f是*.v或*.sv文件的目录列表。

- -full64:vcs 以 64 位模式编译,生成 64 位的 simv,如果不加这条命令则无法生成 simv。

- -R:编译后立即进行仿真。

- +v2k:支持 Verilog 2001 标准。

- -sverilog:提供对 Systemverilog 的支持。

- -l log_file:用于将编译产生的信息放在 log 文件内。

- -debug_all:用于产生debug所需的文件。

- -Mupdate:源文件有修改时,只重新编译有改动的.v文件,节约编译时间。

- -timescale=1ns/1ns 设置仿真精度,可以根据实际需要进行更改。

- -kdb:-kdb 选项支持输出 kdb 格式的数据,用于与 Verdi 在交互模式交换数据,而 kdb 格式属于 “Limited Customer Availability” 特性,必须通过 -lca 选项开启。

需注意,在使用VCS & Verdi 联合仿真时,需要在tb文件中加上以下内容:

initial begin

$fsdbDumpfile("*.fsdb");

$fsdbDumpvars(0);

end

用于生成 .fsdb 文件,fsdb文件是 Verdi 可识别的波形文件。

三、实战演示

编写.v文件和tb.v文件(.sv文件),之后创建file_list.f文件:

./xxx.v

./xxx_tb.v

file_list.f文件为.v/.sv文件的列表,方便后续用vcs编译和仿真时直接调用,不用一个一个打。

编写Makefile文件:

#-------------------------------------------------------------------------------------------------------

all : clean vcs verdi

#-------------------------------------------------------------------------------------------------------

vcs :

vcs \

-f filelist.f \

-timescale=1ns/1ps \

-full64 -R +vc +v2k -sverilog -debug_access+all\

| tee vcs.log

#-------------------------------------------------------------------------------------------------------

verdi :

verdi -f filelist.f -ssf tb.fsdb &

#-------------------------------------------------------------------------------------------------------

clean :

rm -rf *~ core csrc simv* vc_hdrs.h ucli.key urg* *.log novas.* *.fsdb* verdiLog 64* DVEfiles *.vpd

#-------------------------------------------------------------------------------------------------------

之后运行make all就可以用VCS & Verdi 联合仿真

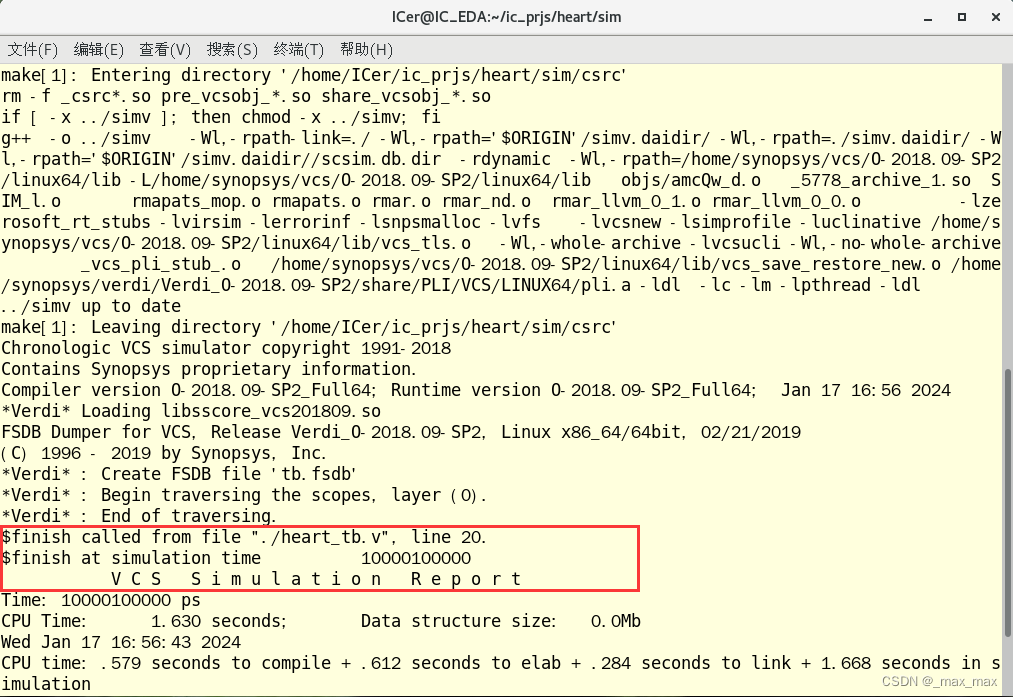

make vcs后出现如下现象,即代表编译成功

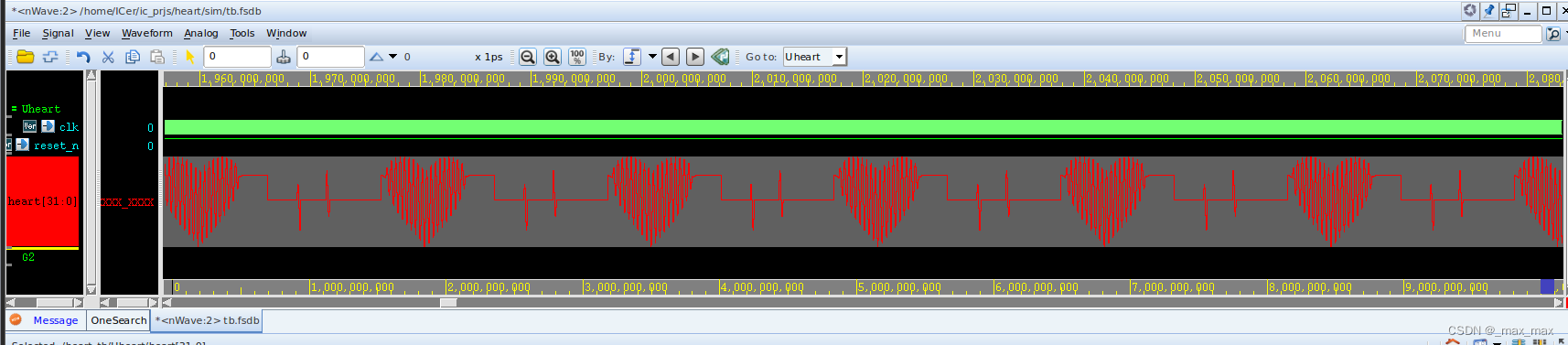

之后运行make verdi可查看波形

Waveform中可调整波形的格示,用法和vivado和modelsim中相似

四、总结

本文章只是VCS & Verdi 联合仿真的简单总结,需多加练习才能更熟练地使用。

本文介绍了VCS(VerilogCompilationandSimulation)作为Synopsys的主流仿真工具,其功能包括高效的编译、多层仿真、调试和系统级支持。同时,Verdi作为交互式调试工具,提供强大的分析功能。文章还展示了如何使用VCS和Verdi进行编译和实战演示,以及Makefile的使用。

本文介绍了VCS(VerilogCompilationandSimulation)作为Synopsys的主流仿真工具,其功能包括高效的编译、多层仿真、调试和系统级支持。同时,Verdi作为交互式调试工具,提供强大的分析功能。文章还展示了如何使用VCS和Verdi进行编译和实战演示,以及Makefile的使用。

4850

4850

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?