大部分内容来自野火的FPGA教学视频,笔者仅作整理,方便回顾。 视频地址:【野火】FPGA系列教学视频,真正的手把手教学,“波形图”教学法,现场画波形图写代码,硬件基于野火FPGA EP4CE10征途系列开发板,已完结_哔哩哔哩_bilibili

IP核的定义

IP(Intellectual Property),即知识产权,在半导体产业中将IP核定义为“用于ASIC或FPGA中的预先设计好的电路功能模块”,简而言之,这里的IP核即电路功能模块。

IP核往往不能跨平台使用;IP核不透明,看不到内部核心代码,无法进行修改优化;定制IP核需额外收费。

IP核的存在形式

HDL语言形式-----软核(软IP)

硬件描述语言;可进行参数调整、复用性强;布局、布线灵活;设计周期短、设计投入少。

这是大多数FPGA内IP核的存在形式,以nsdl源文件的形式提供,不涉及物理实现,为后续设计留下发挥空间,以加密的形式提供,用户看不到RTL代码,可通过头文件或GUI界面对参数进行设置。以源代码的形式提供,尽管有加密措施,但仍有知识产权问题。

网表形式----固核

完成了综合的功能块;可预布线特定信号或分配特定的布线资源。

软核与硬核的折中,适合于对时序要求严格的内核(例如PCIE)。有部分固定的布局,会影响其他电路的布局。

版图形式----硬核

硬核是完成提供设计的最终阶段产品--掩膜(Mask);缺乏灵活性、可移植性差;更易于实现IP核的保护。

Mega Wizard插件管理器调用IP核(Quartus II软件)

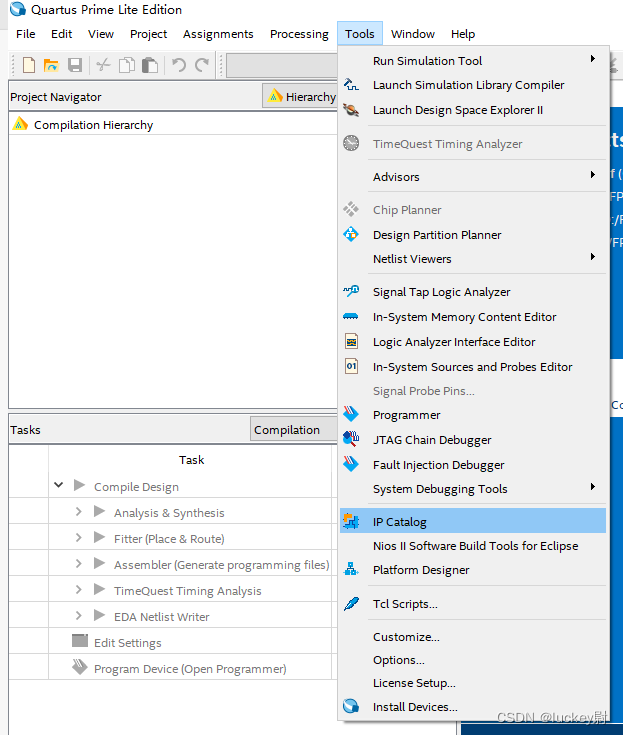

新版本的Quartus II 14.0 的Tools菜单中不再有“MegaWizard Plug-In Manager”,而是更名为“IP CATALOG”了。

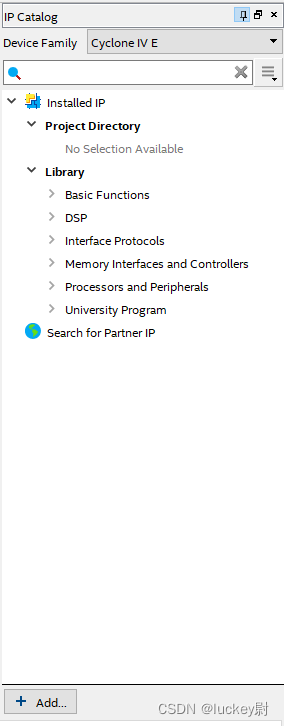

点击Tool菜单下IP CATALOG选项,在屏幕右侧出现IP核选择界面,点击Device Family选择所用的FPGA芯片系列,之后在搜索框中搜索或分类中找到要用的IP核,选中并点击下方Add。

如果是在工程内部打开IP CATALOG则没有Device Family选项,因为工程中已经确定使用的FPGA芯片,所以不再有芯片系列选择选项,忽略即可。

点击Add后会出现文件保存、语言选择的界面,根据需要选择即可。之后便进入IP核配置界面,这部分详见各IP核介绍。

调用IP核

与普通的实例化相同,在成功生成IP核的个文件后,点击xx_inst.v文件,复制到相应的文件中,修改参数完成实例化即可。

复制生成的IP核

复制生成的IP核文件,在工程中添加文件,添加IP核的.qip文件即可。

常用IP核介绍(Quartus II软件)

PLL IP核介绍

PLL(Phase Locked Loop),即锁相环,其性能强大,可以对输入到FPGA的时钟信号进行任意分频、倍频、相位调整、占空比调整,从而输出一个期望时钟。 PLL IP核能对输入的时钟信号进行优化,使信号在抖动等方面的性能更好,所以即使不对输入的时钟做参数上的修改也可以使用PLL。

配置过程

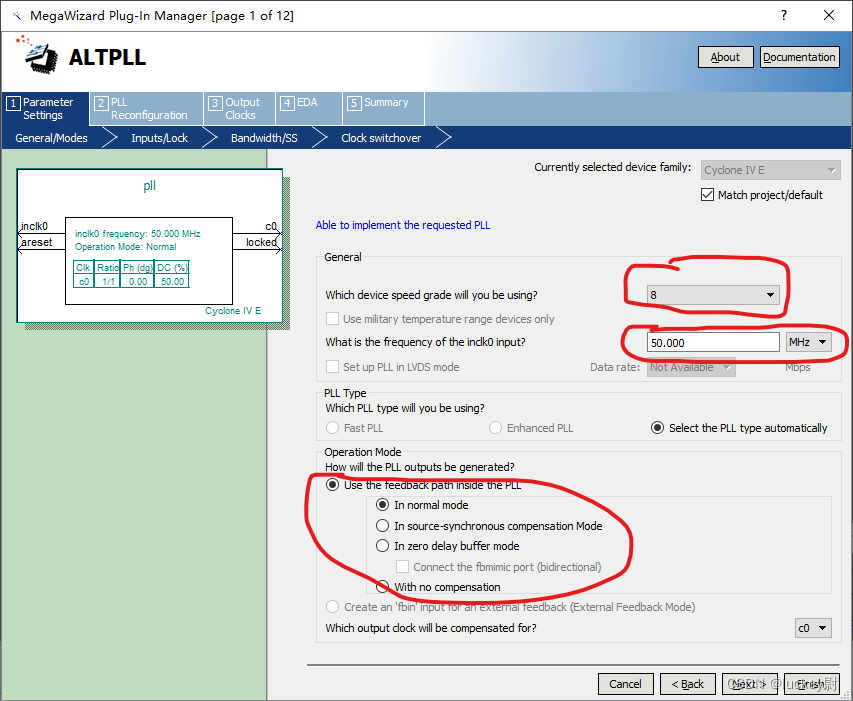

一、进入pll配置界面后,如下图所示,分别设置1、芯片的速度等级;2、输入时钟信号的频率(也可更改单位,输入时钟信号的周期等);3、选择PLL的工作模式。然后点击下一步。四种工作模式的特点如下,根据需要选择。

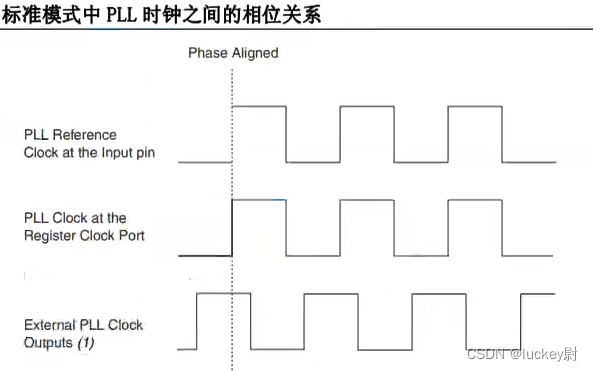

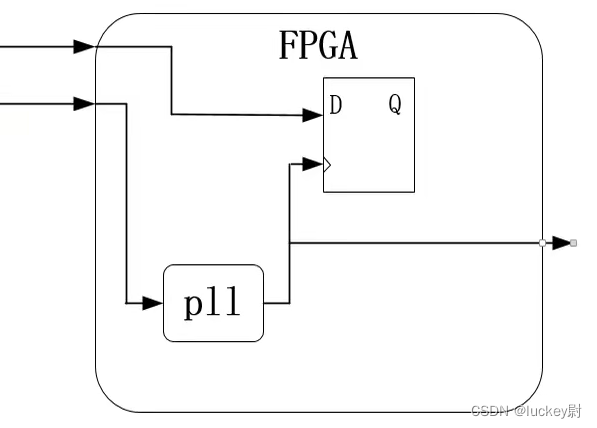

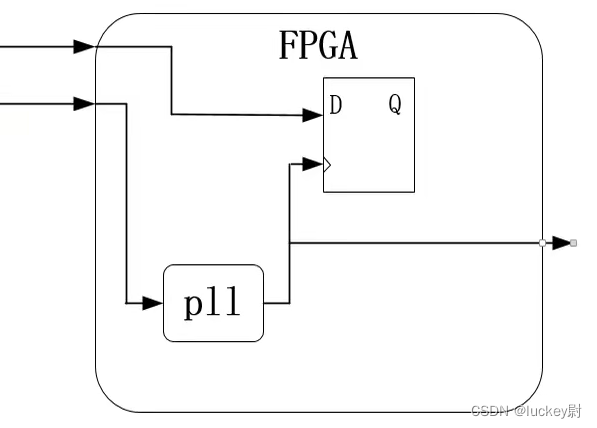

标准模式:对FPGA时钟输入和PLL核产生的用于内部寄存器的时钟进行补偿,使两者的相位相同,不考虑PLL产生的输出到FPGA外部的时钟,如下图所示。所以该模式下PLL产生的时钟使用在内部寄存器上,不要用于时钟输出。

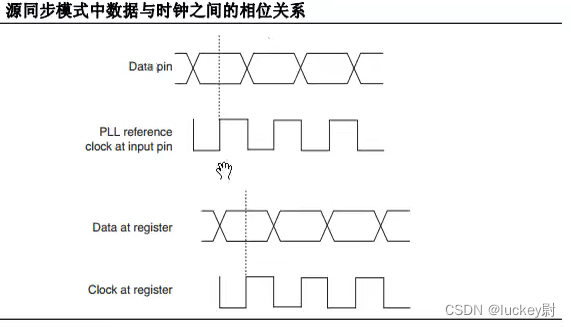

源补偿模式:即数据和时钟来源于同一个数据源。 对数据输入和时钟输入进行补偿,使FPGA输入端口上数据输入和时钟输入之间的相位关系与寄存器上的数据输入和时钟输入保持一致(整体有延迟),如下图所示。该模式用于数据接口,特别是高速数据接口。

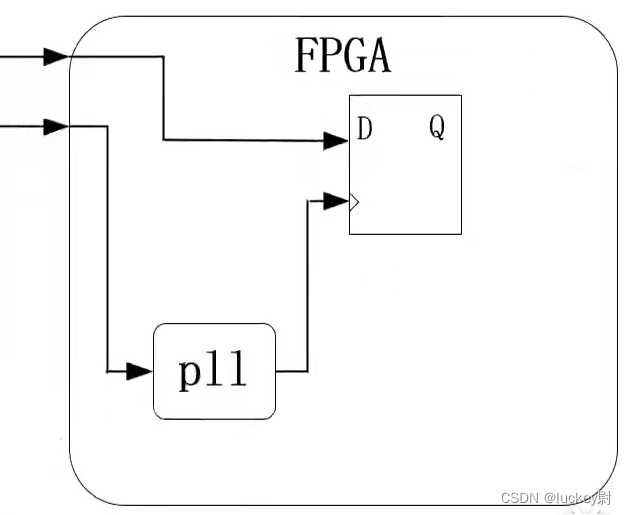

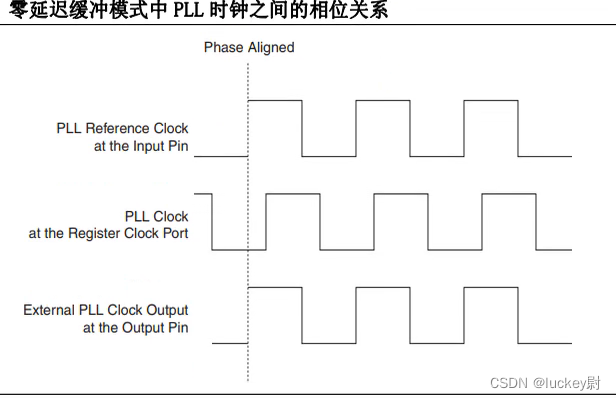

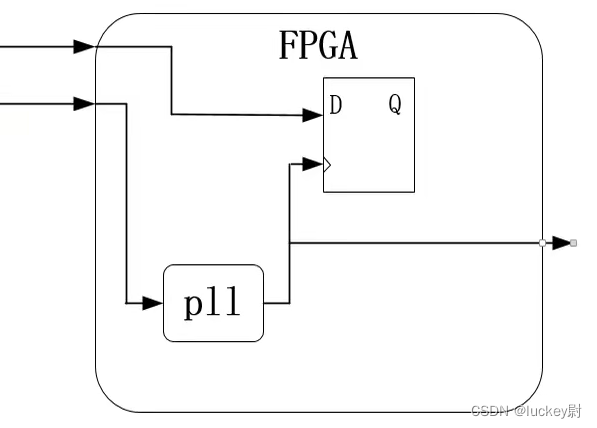

零延时缓冲模式:该模式与标准模式相反,PLL产生的时钟中,用于输出到FPGA外部的时钟进行了补偿,使之输入的时钟相位相同,而不考虑用于内部寄存器的时钟,内部寄存器时钟相位有偏差,如下图所示。该模式产生的时钟用于输出。

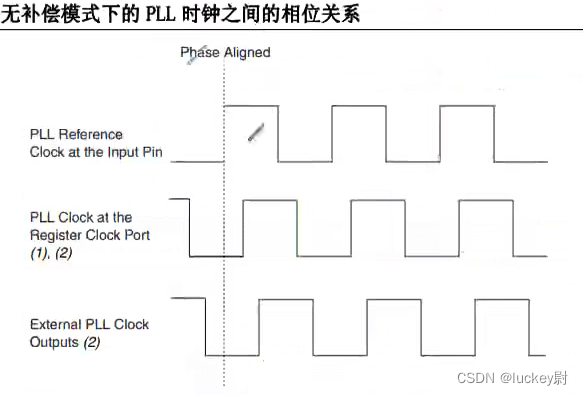

无补偿模式:不进行任何补偿。

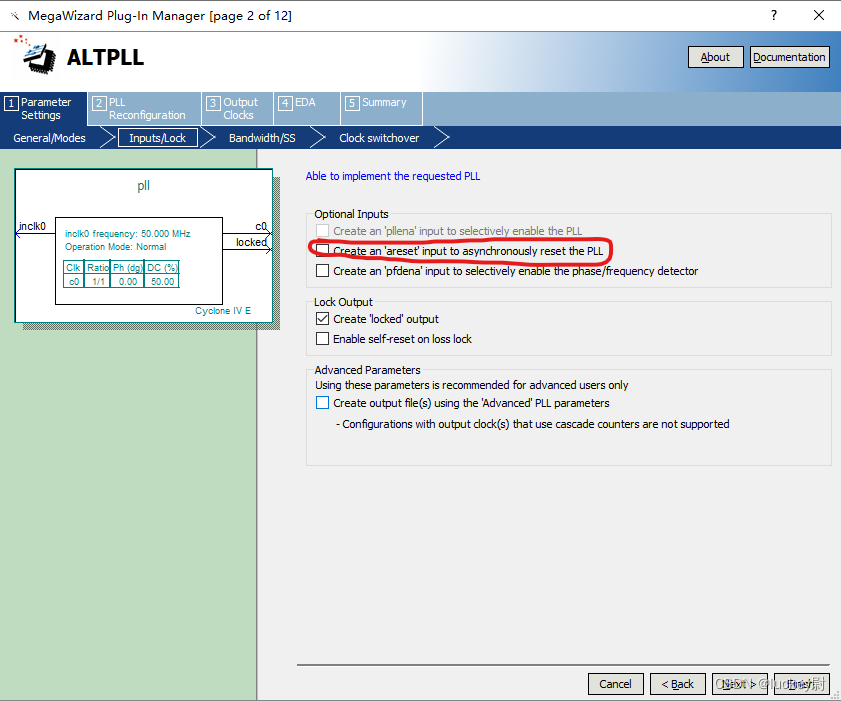

二、如下图所示,红圈中选项为创建异步复位信号,一般不用,根据需要选择,这里选择取消。在Lock Output中勾选了创建锁定输出,该选项选中后会有一个锁定输出,该输出为高电平时有效,表示输出的时钟可用,低电平时表示输出的时钟还不能使用,这里选择勾选上。点击下一步

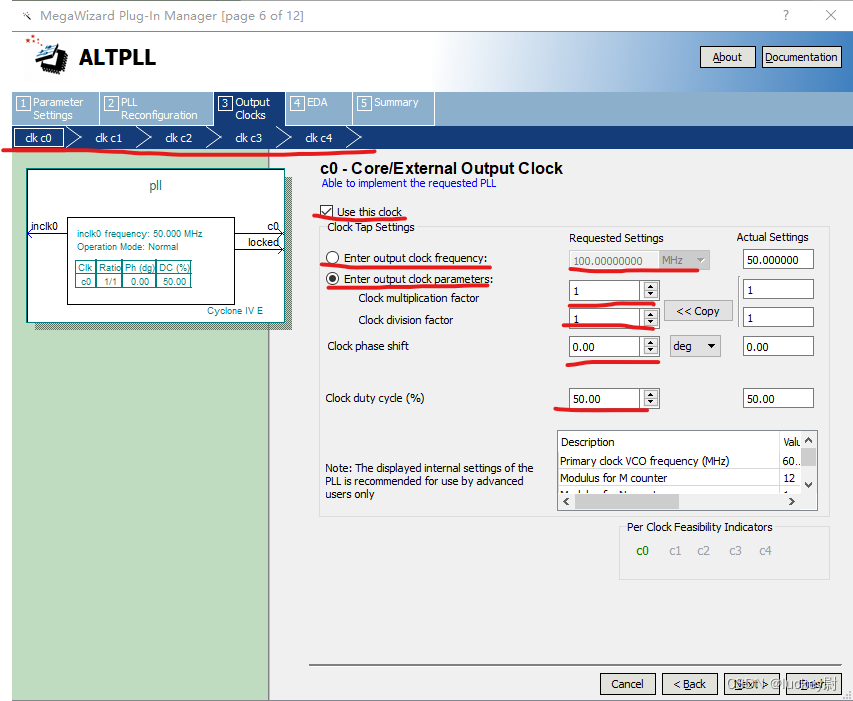

三、连续点击下一步,进入输出时钟配置选项卡,如下图所示,期间的其他界面为PLL的其他高级功能,这里不做介绍。PLL IP核最多可输出5个时钟,在时钟输出配置选项卡下方可选择c0到c4子选项卡,在相应的子选项卡下勾选Use this dock则启该时钟输出。

所有的参数设置框右侧都有着另一个框,这个参数框不能编辑,是系统根据用户在左侧输入的参数,结合实际电路设置的实际参数,会尽量接近用户设置的参数理想输入。例如若在相位调整中输入10.00,实际右侧为10.08,这便是系统能调整的最接近10.00的值。

选中enter output clock parameter,在输出时钟参数设置中可输入乘法因子和除法因子,最终该时钟输出的时钟频率为FPGA输入时钟除以除法因子,在乘以乘法因子,也可选中enter output clock frequency,输入需要的时钟频率,系统会计算并自动设置除法和乘法因子,输出最接近的时钟频率,注意对于无法通过因子乘除得到的频率,只会输出最接近的频率。

在clock phase shift中输入相位值可对相位进行调整,可选择角度和时间单位。在clock duty cycle中调整占空比。所有参数设置完毕后,点击下一步,进入EDA选项卡。

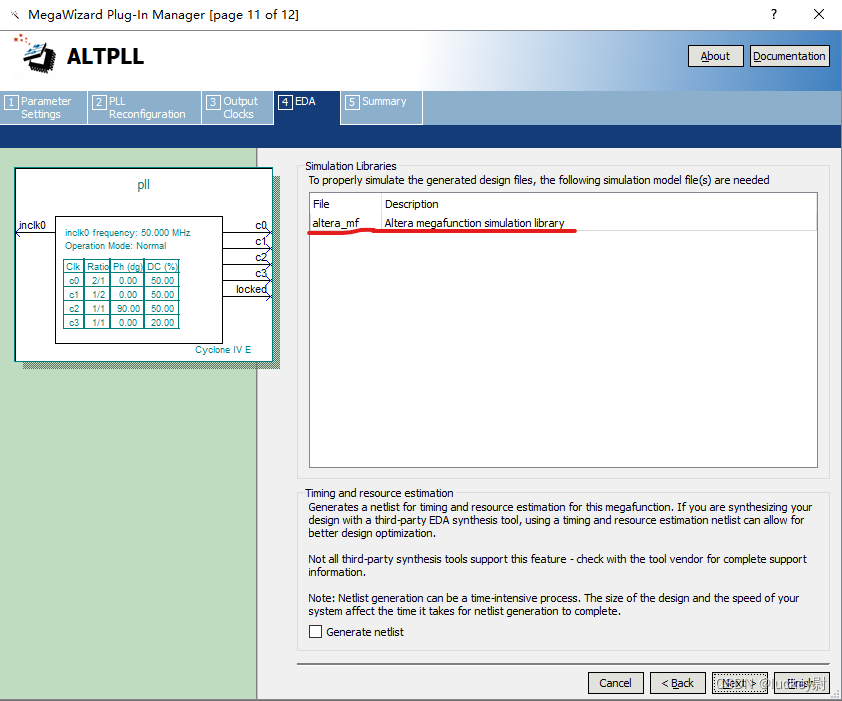

四、 该选项卡下,如下图所示,划红线为仿真所需的库文件,当使用quartus与modlesim联合仿真时,该文件自动添加,但如果用modelsim单独仿真,需要手动添加。点击下一步。

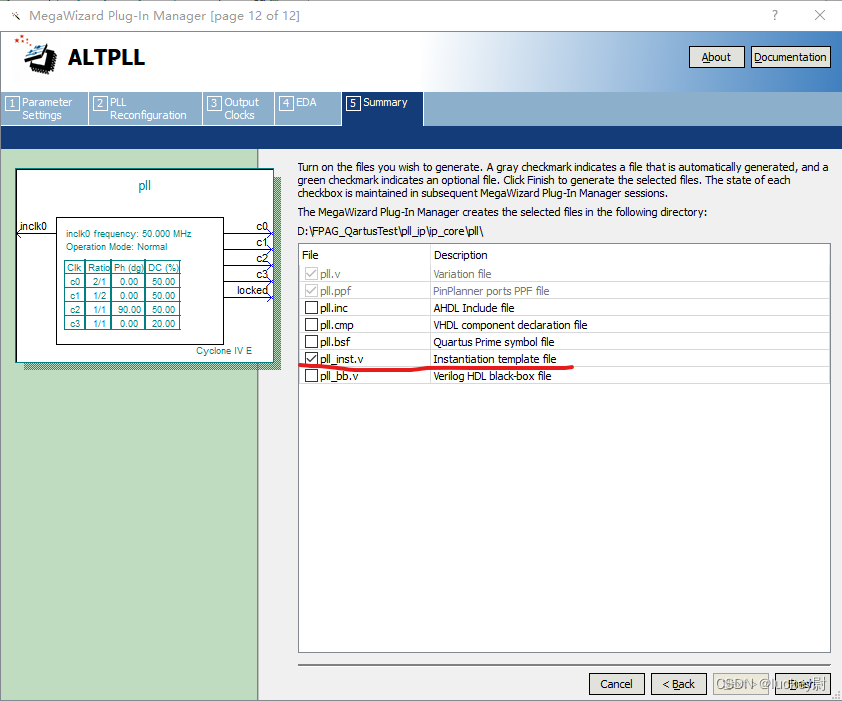

五、进入Summary选项卡,这里设置需要输出的文件,除了必须输出的.v和.ppf文件外,还需输出一个xx_inst.v文件,其他文件不推荐,如下图所示。点击finish完成PLL的配置。

262

262

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?