摘要:

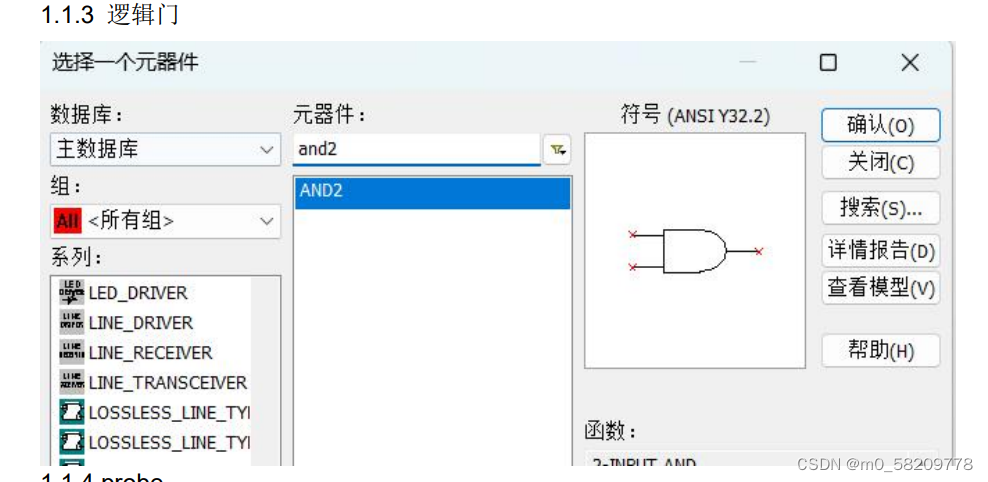

本实验通过Multsim和Quartus软件完成对同步十三进制计数器的仿真,运用Quartus软件编VHDL程序,实现波形图的生成,并且运用Multsim软件进行电路图仿真。同时,加深 对数字电路和VHDL语言的理解,提高实验操作能力。

关键词:Quartus;Multsim;VHDL

引言

随着数字电路技术的迅猛进步,VHDL已成为硬件描述语言中的关键利器。 利用VHDL,工程师能够精准地描绘电路逻辑,并通过仿真工具验证设计的准确 性,进而生成对应的波形图。在本文中,我们将依据同步十三进制计数器的原 理,采用Quartus软件编写VHDL代码,以直观地展示并生成所需的波形图,并借 助Mutsim软件对电路图进行仿真,使用数码管直观显示十三进制计数器。这样 的工作流程使得电路设计、验证与仿真更加高效、精确。

2.同步十三进制计数器的VHDL程序

2.同步十三进制计数器的VHDL程序

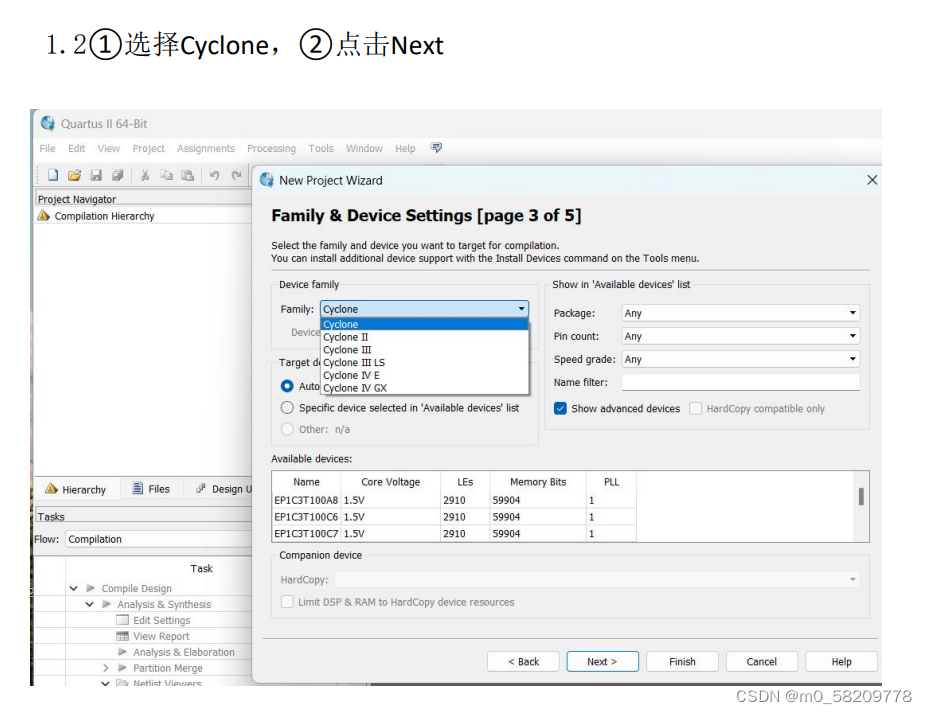

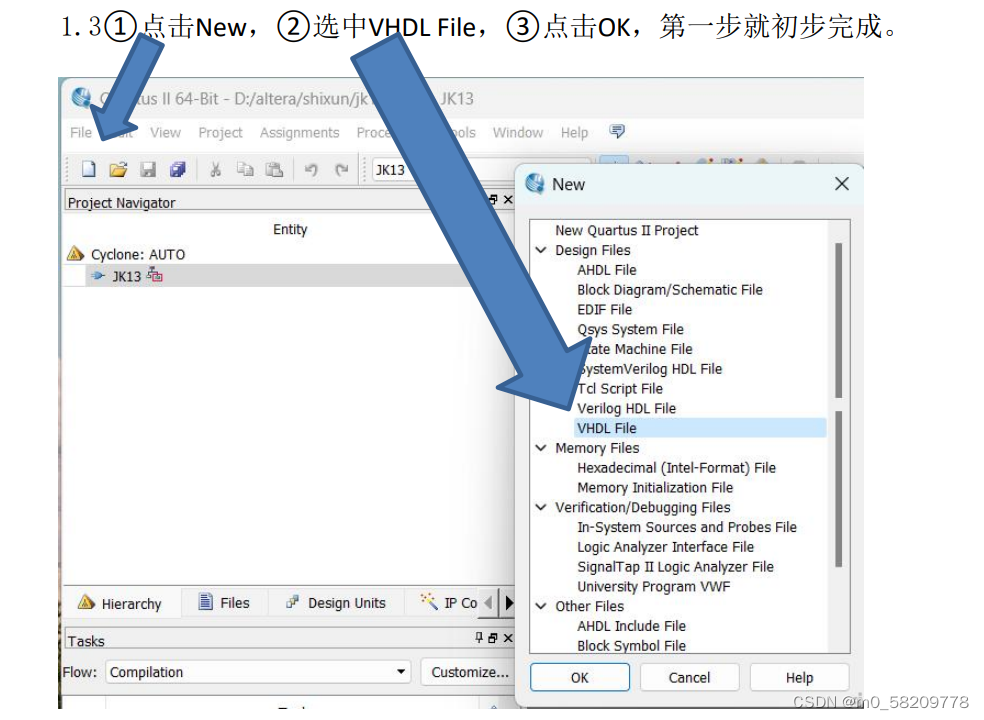

VHDL(VHSIC Hardware Description Language)是一种文本化的硬件描述语言, 它允许工程师精确地定义数字系统的结构和行为。在Quartus软件中,使用VHDL 的数据流描述方法来进行数字系统设计,通常遵循以下步骤:

2.1. 定义实体(Entity):

(1)在VHDL代码中明确指定数字系统的接口。

(2)包括所有输入输出端口的数据类型、位宽和方向。

2.2. 架构化设计(Architecture):

(1)详细描述系统内部的工作机制和逻辑。

(2)定义数据如何在各个组件之间流动和处理。

2.3. 构建层次结构:

(1)将定义的实体和架构组合起来,形成一个完整的系统模型。

(2)通过VHDL的层次化描述,实现复杂系统的模块化设计。

通过这种VHDL描述方式,工程师可以在Quartus软件中高效地创建、模拟和验证 数字系统,确保设计的正确性和可靠性。

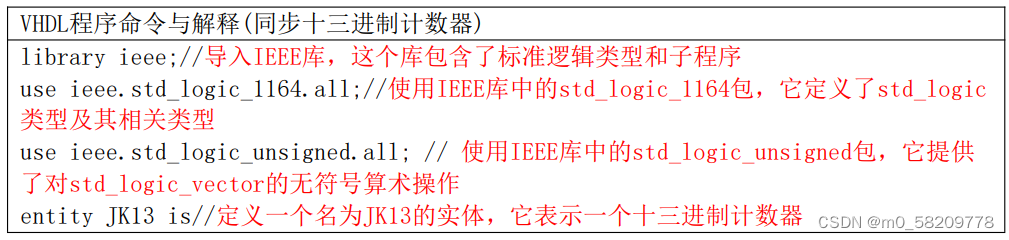

VHDL程序命令与解释(同步十三进制计数器)

library ieee;//导入IEEE库,这个库包含了标准逻辑类型和子程序

use ieee.std_logic_1164.all;//使用IEEE库中的std_logic_1164包,它定义了std_logic

类型及其相关类型

use ieee.std_logic_unsigned.all; // 使用IEEE库中的std_logic_unsigned包,它提供

了对std_logic_vector的无符号算术操作

entity JK13 is//定义一个名为JK13的实体,它表示一个十三进制计数器

EDA

20

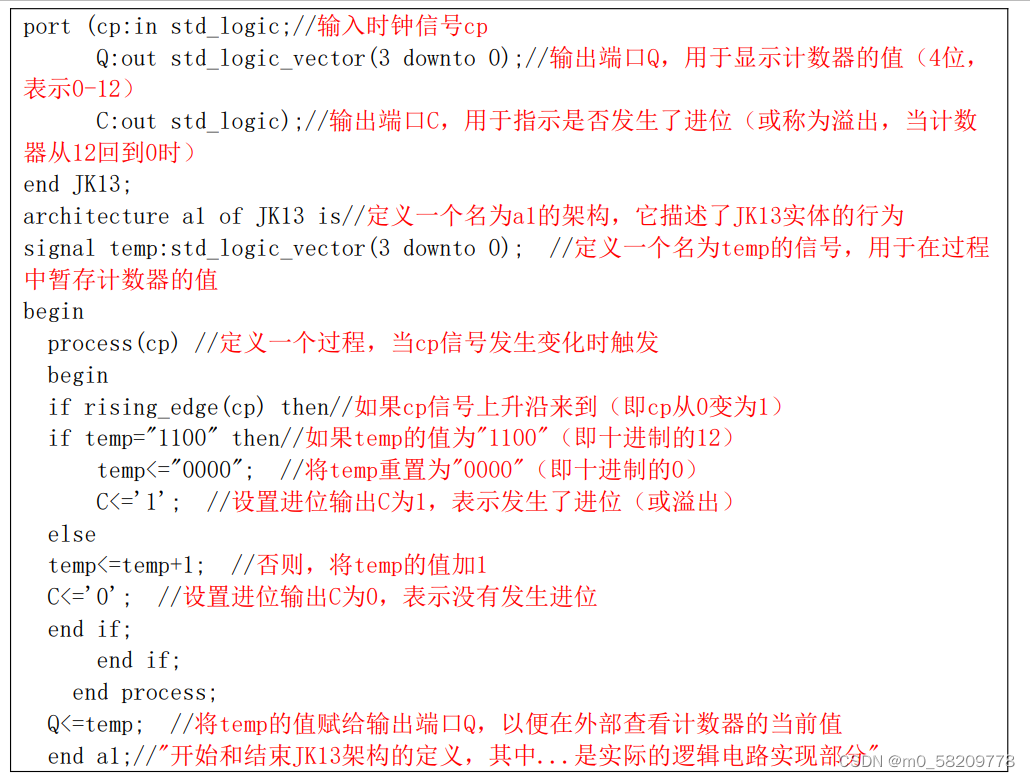

port (cp:in std_logic;//输入时钟信号cp

Q:out std_logic_vector(3 downto 0);//输出端口Q,用于显示计数器的值(4位,

表示0-12)

C:out std_logic);//输出端口C,用于指示是否发生了进位(或称为溢出,当计数

器从12回到0时)

end JK13;

architecture a1 of JK13 is//定义一个名为a1的架构,它描述了JK13实体的行为

signal temp:std_logic_vector(3 downto 0); //定义一个名为temp的信号,用于在过程

中暂存计数器的值

begin

process(cp) //定义一个过程,当cp信号发生变化时触发

begin

if rising_edge(cp) then//如果cp信号上升沿来到(即cp从0变为1)

if temp="1100" then//如果temp的值为"1100"(即十进制的12)

temp<="0000"; //将temp重置为"0000"(即十进制的0)

C<='1'; //设置进位输出C为1,表示发生了进位(或溢出)

else

temp<=temp+1; //否则,将temp的值加1

C<='0'; //设置进位输出C为0,表示没有发生进位

end if;

end if;

end process;

Q<=temp; //将temp的值赋给输出端口Q,以便在外部查看计数器的当前值

end a1;//"开始和结束JK13架构的定义,其中...是实际的逻辑电路实现部分"

总结

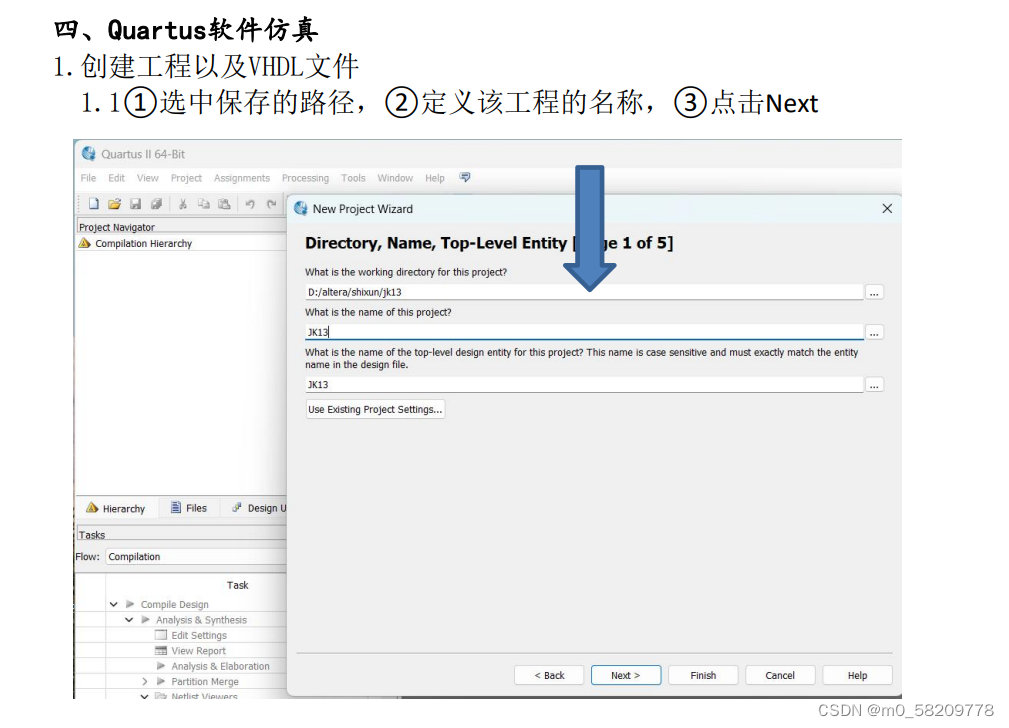

一.本次实验通过使用Quartus软件编写了一个JK触发器的VHDL代码,并进行了 波形仿真验证。以下是对代码和实验结果的总结:

1.VHDL代码编写:

(1)使用了IEEE标准库,包括std_logic_1164和std_logic_unsigned。

(2)定义了实体(entity)JK13,其中包括一个时钟输入端口cp、一个4位输 出端口Q以及一个输出端口C。

(3)在结构(architecture)a1 中,使用了一个过程(process)来响应时钟 信号。

(4)在时钟上升沿检测到时,根据当前状态进行状态转移,具体逻辑为:如果 当前状态为"1100",则将状态重置为"0000",并将输出信号C置为高电平;否则 ,状态加一,并将输出信号C置为低电平。

(5)最后,将状态信号temp赋值给输出端口Q。

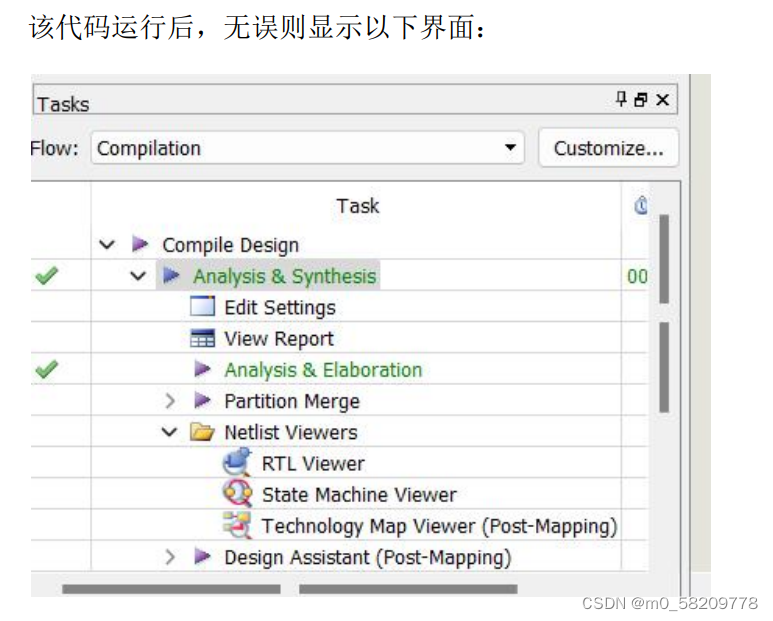

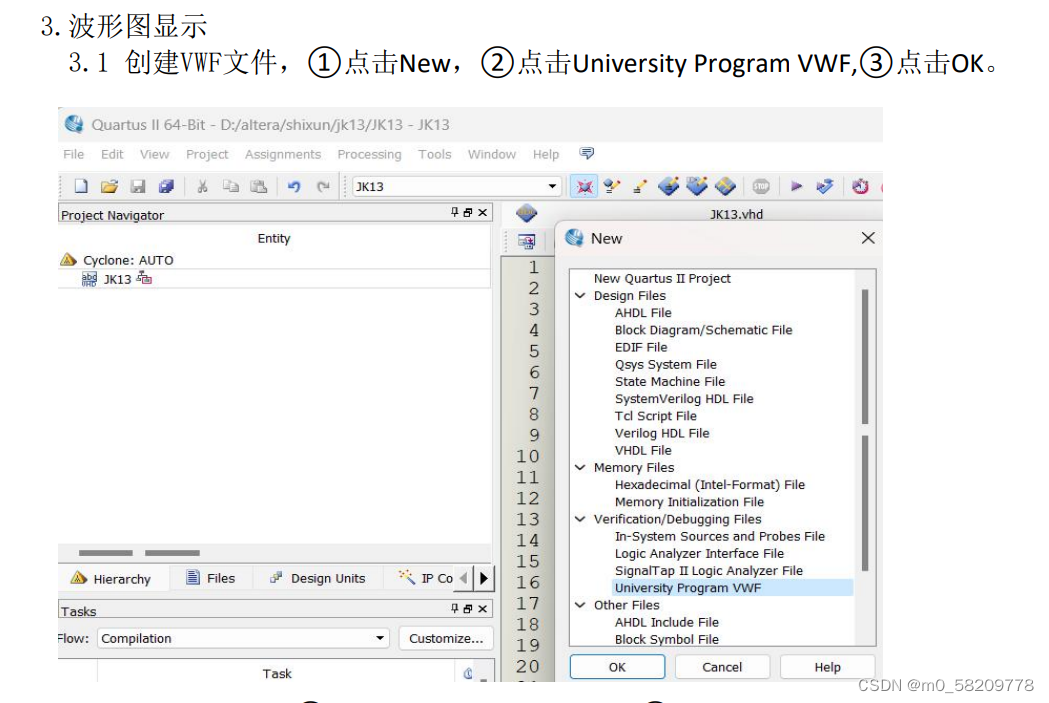

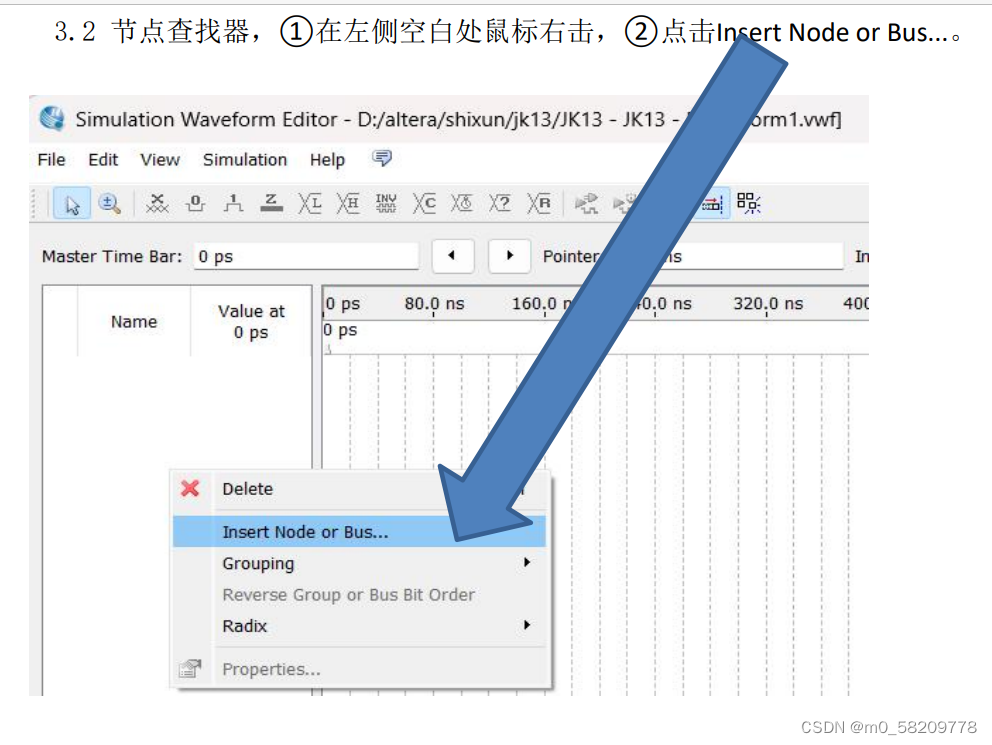

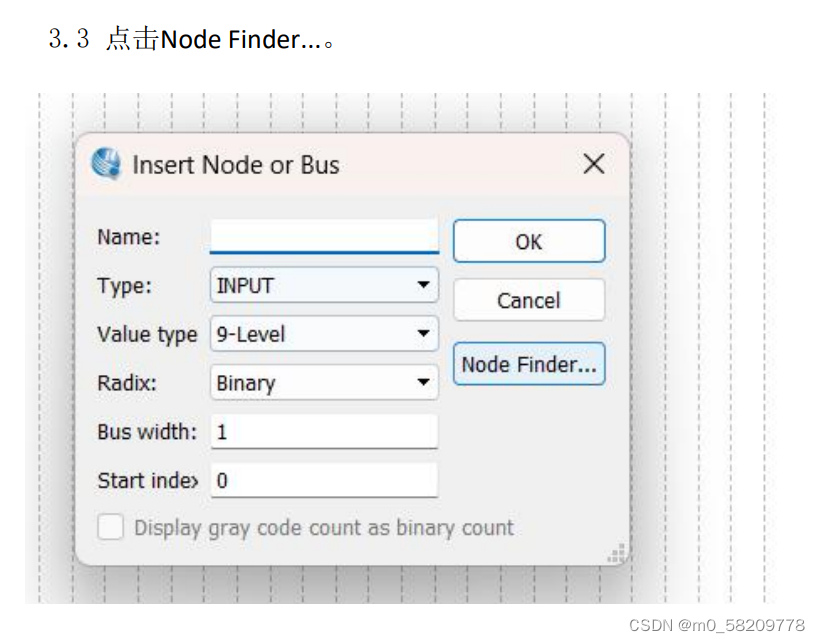

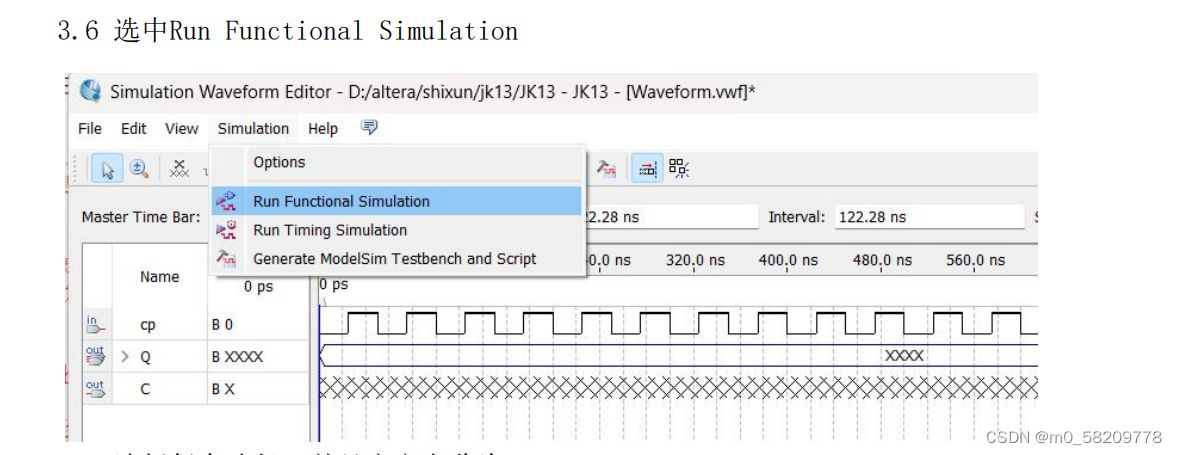

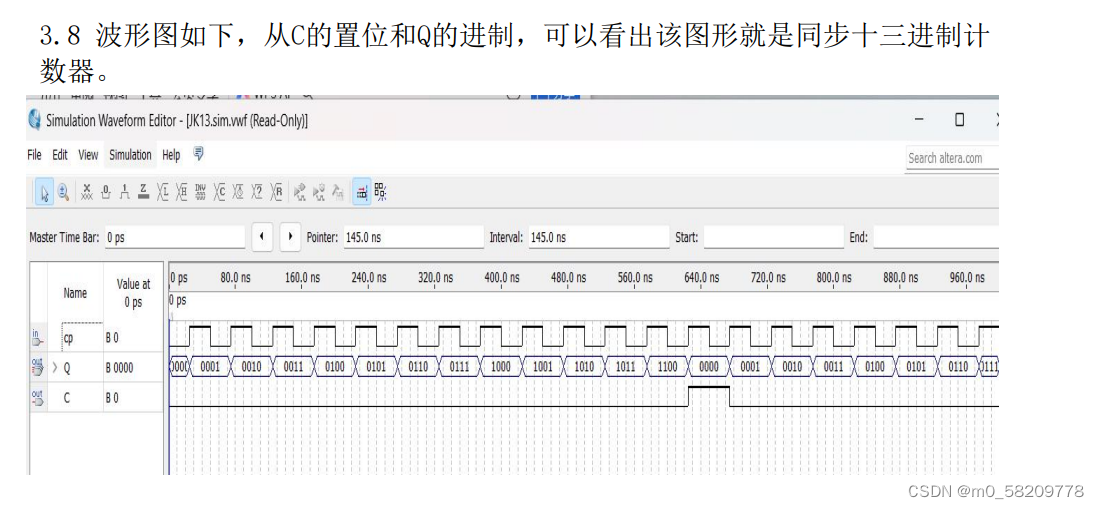

2.波形仿真结果:

(1)通过Quartus软件进行了波形仿真,观察了输入时钟信号cp和输出信号Q、 C的波形变化。 (2)可以看到,随着时钟信号的变化,输出信号Q呈现出了符合JK触发器逻辑 的变化,并且输出信号C在状态转移时也表现出了正确的行为。

3.本次实验通过VHDL语言描述了JK触发器的逻辑功能,并利用Quartus软件进行 了验证。

4.VHDL语言的编写使得描述数字电路逻辑变得简单清晰,而Quartus软件提供了 方便的仿真工具,能够直观地观察数字电路的行为。

5.实验过程中也发现了仿真可能存在的问题,例如干扰因素对结果的影响,需 要进行更深入的分析和理解。

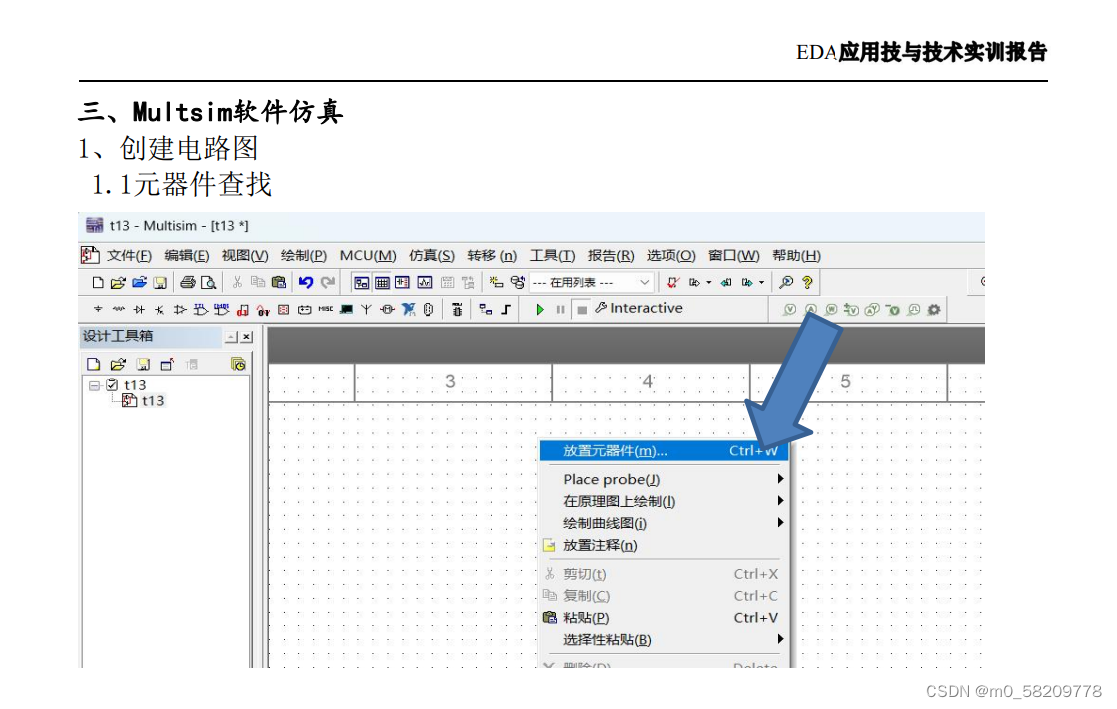

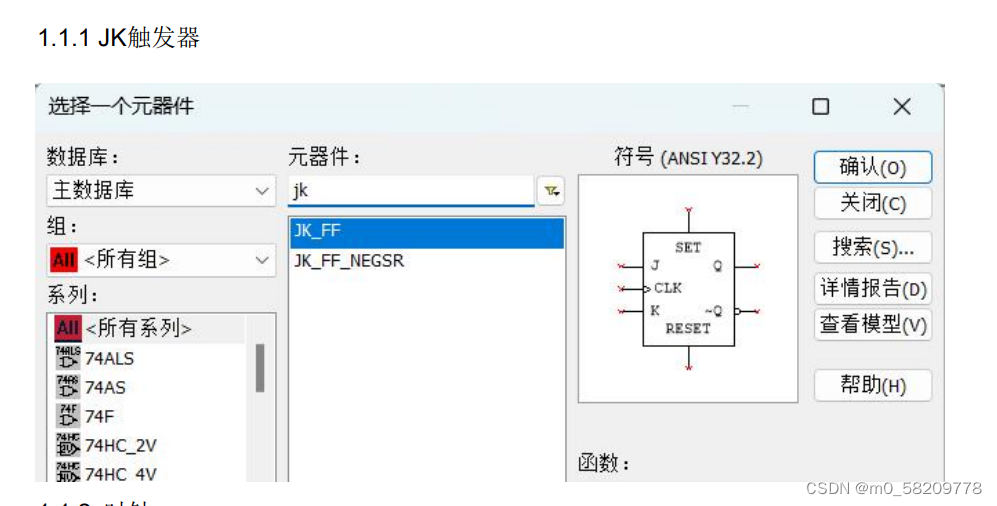

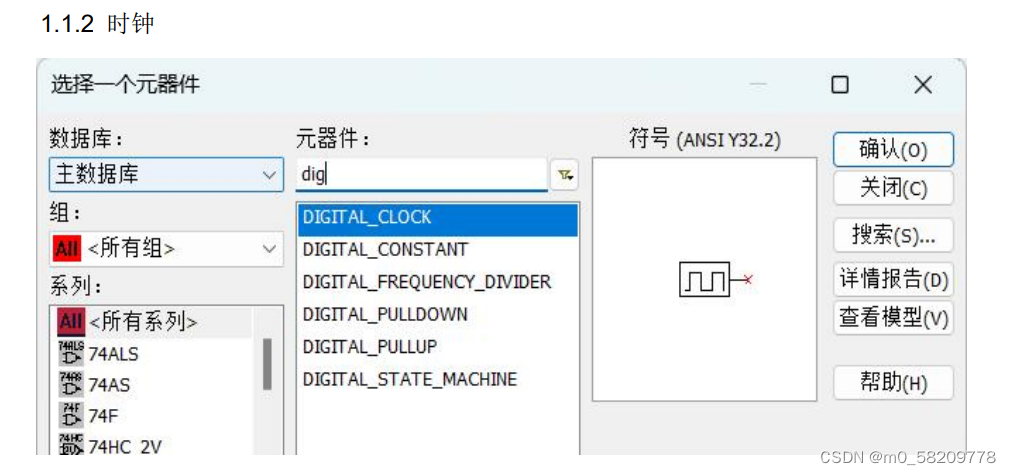

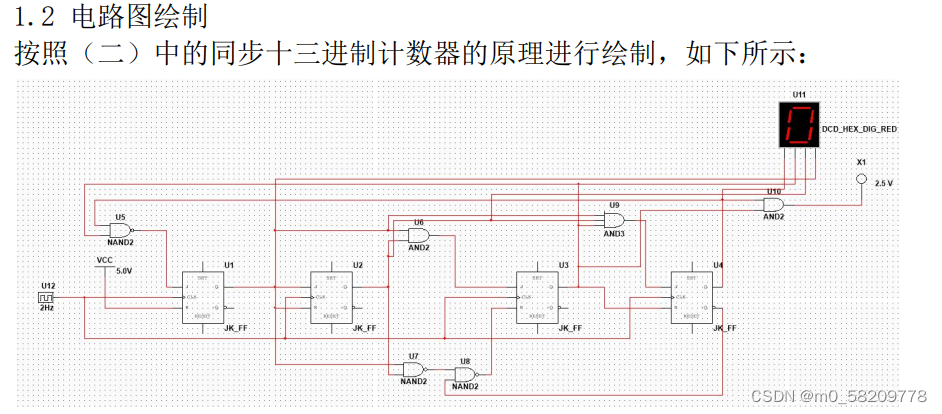

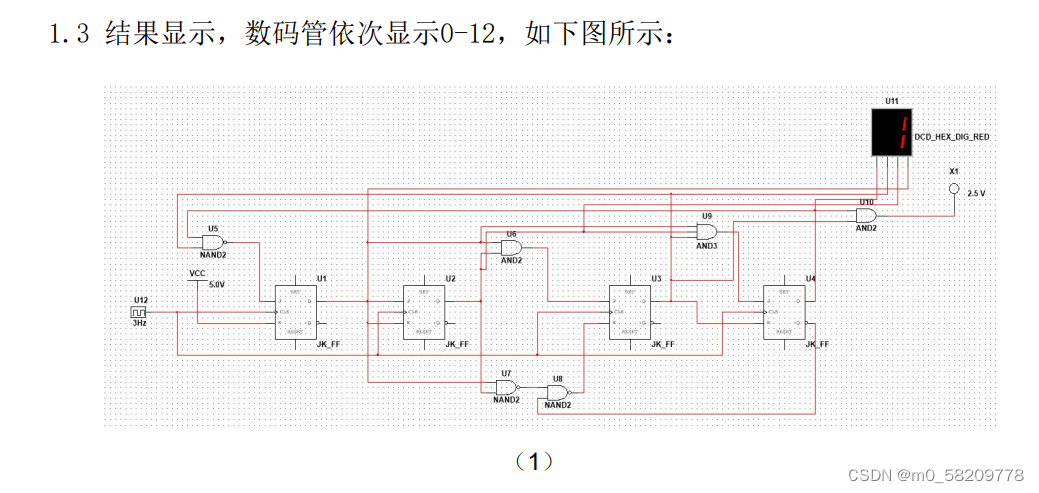

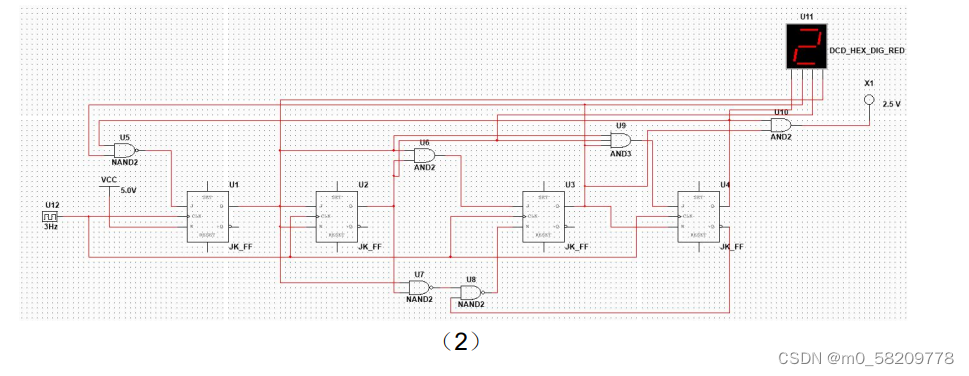

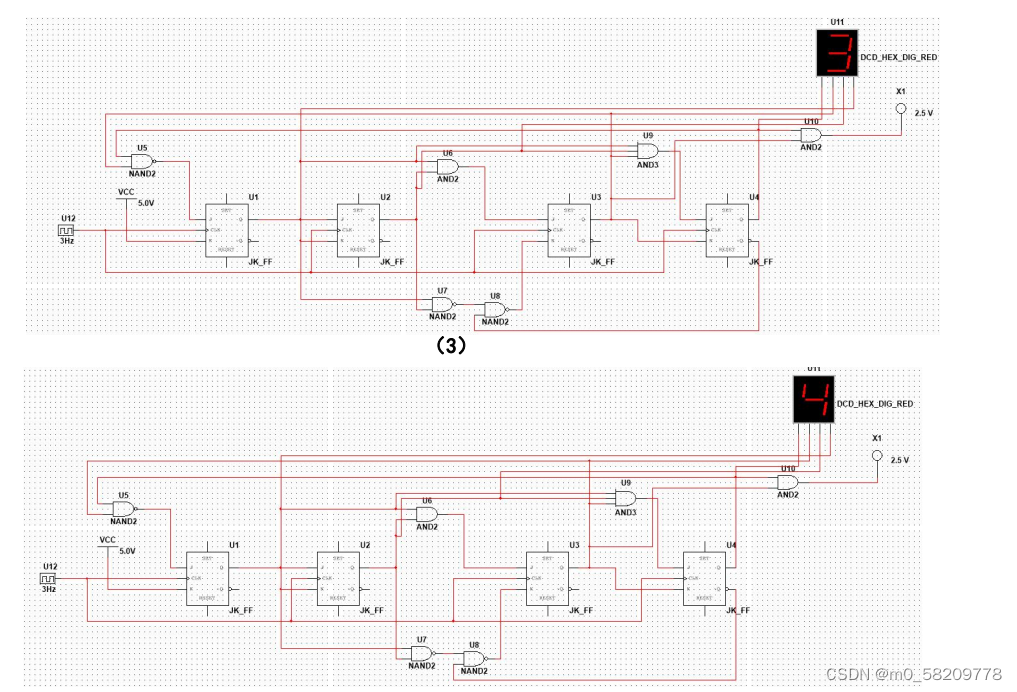

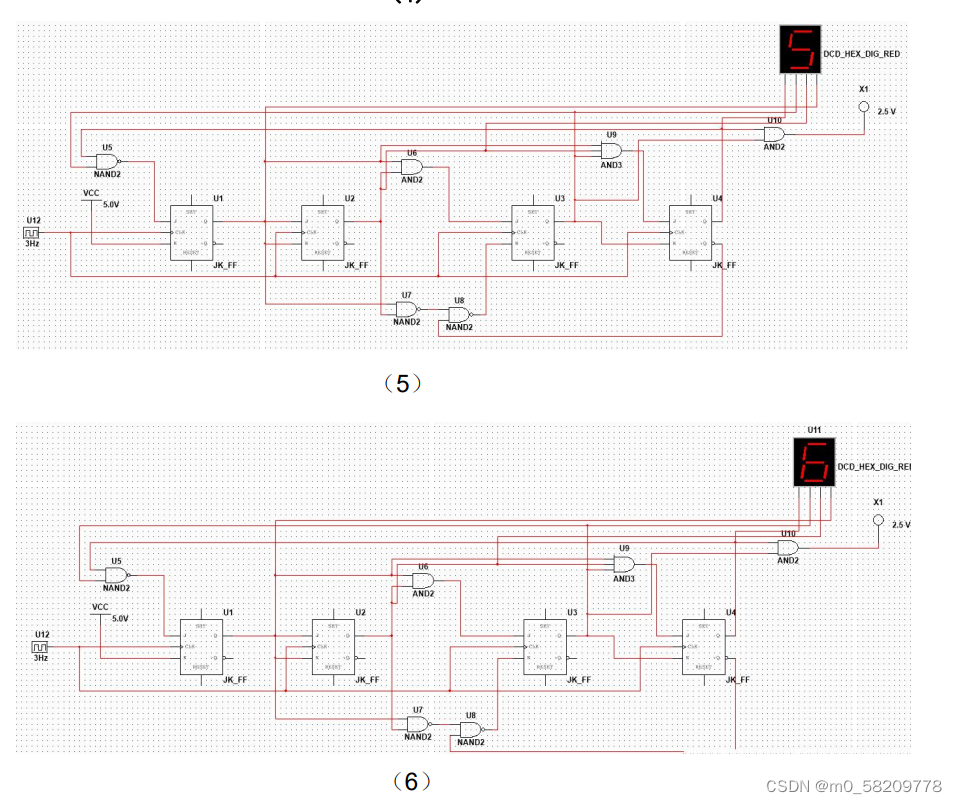

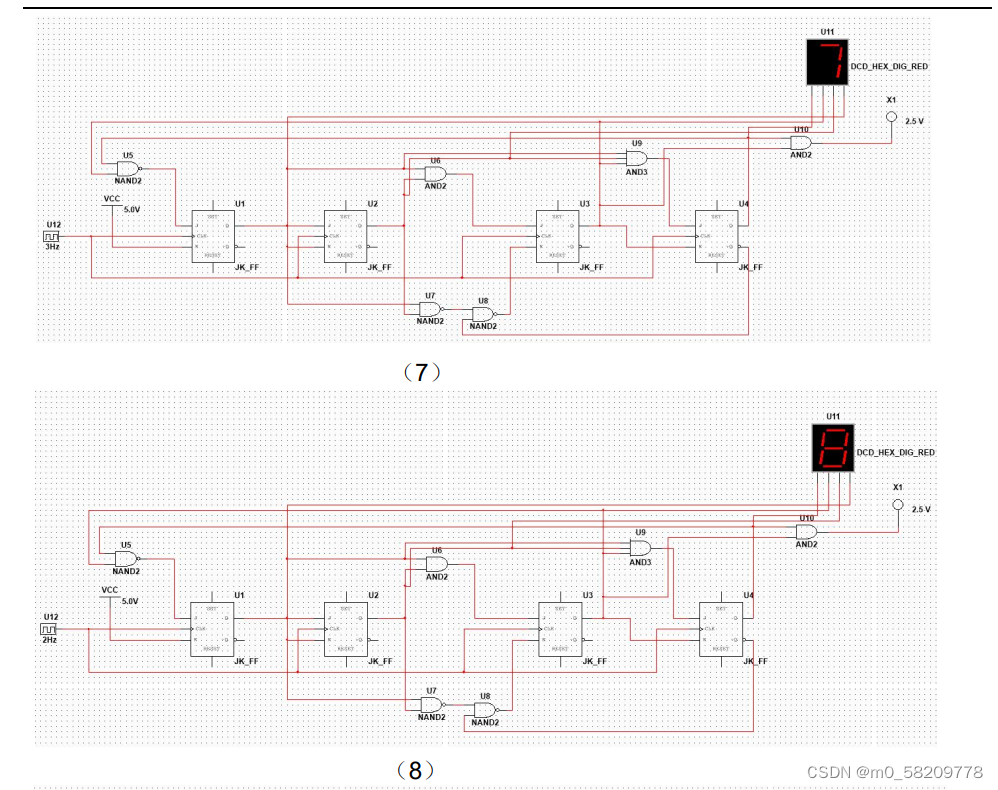

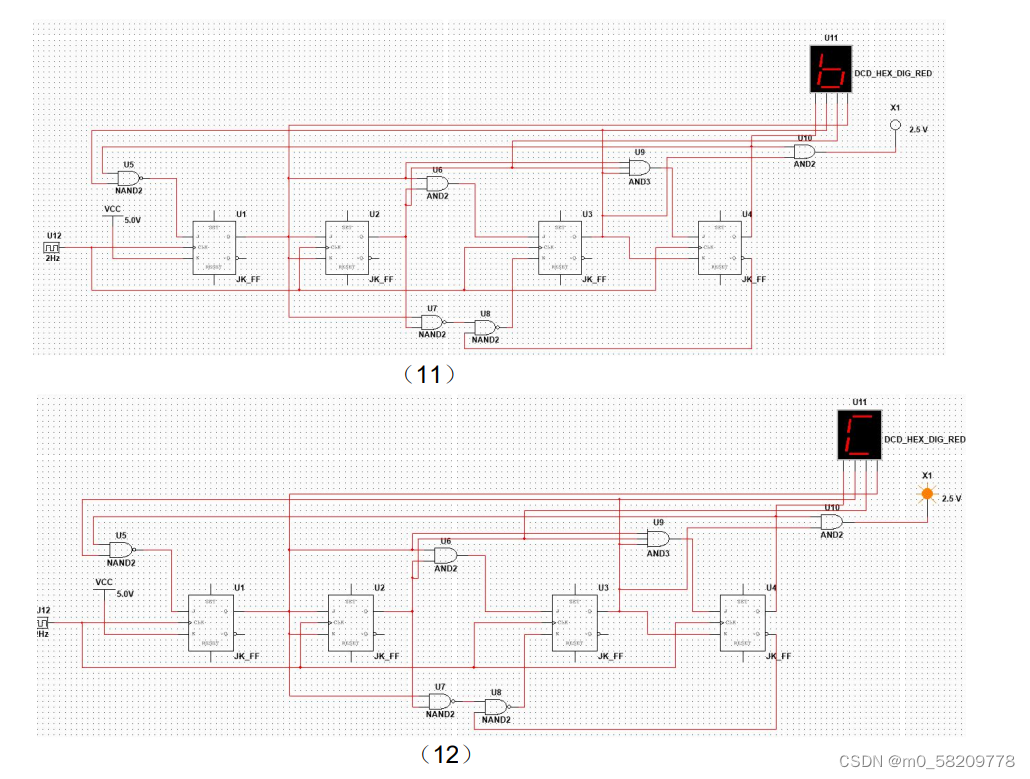

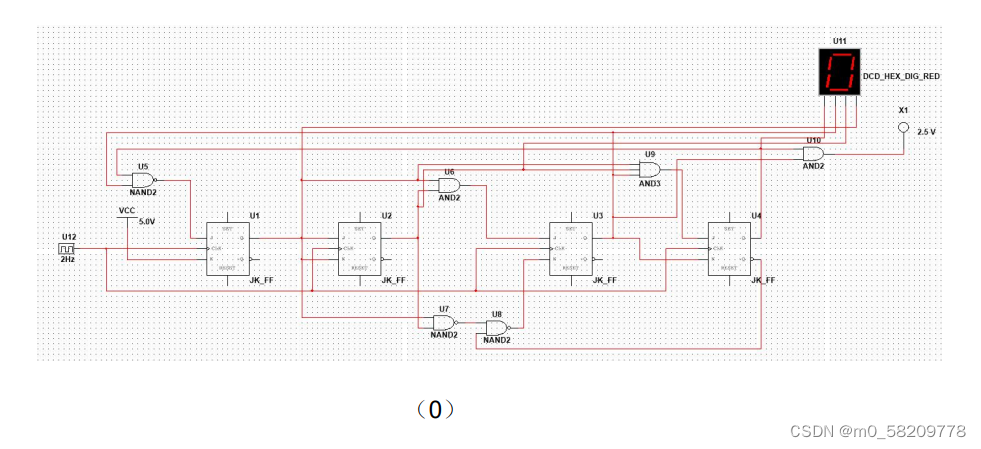

二.在本次实验中,我学会了使用Multisim软件进行电路设计和仿真,以验证数 字电路的逻辑功能。以下是对实验结果的总结:

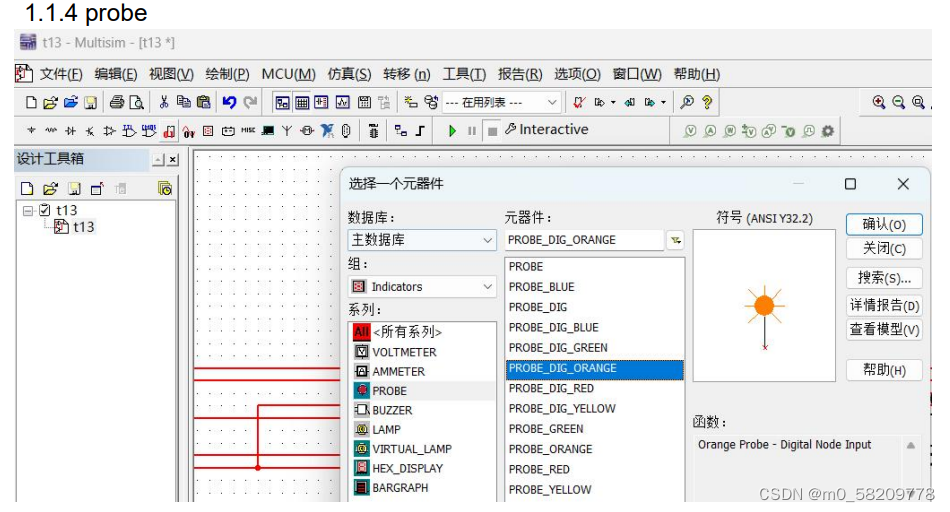

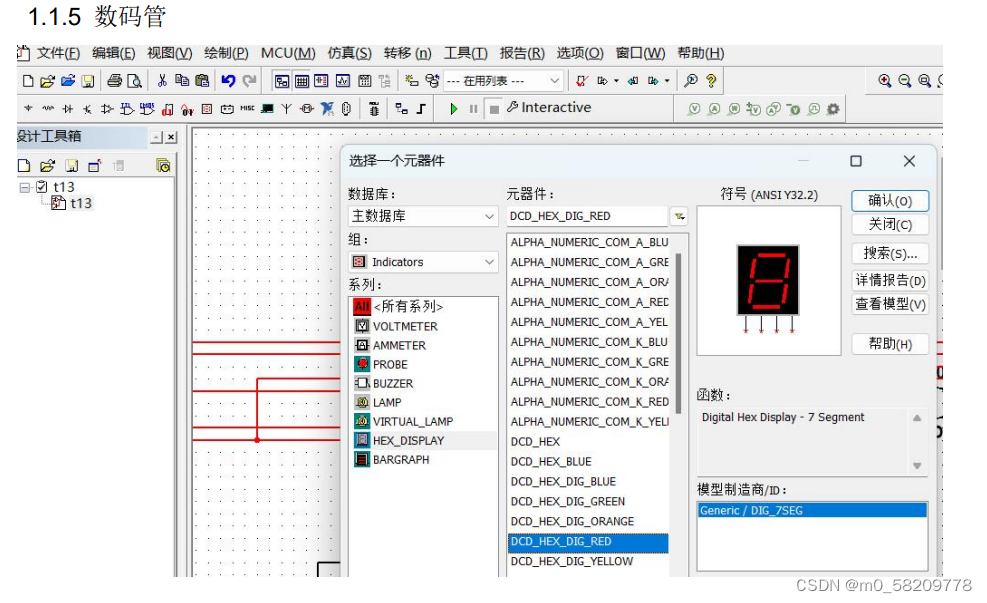

1、通过该实验,我掌握了Multisim软件的基本操作方法,包括创建电路图、添 加元件、连接元件以及设置仿真参数等。

2、通过仿真观察和分析,我成功验证了JK触发器的同步上升沿十三进制计数器 的逻辑功能。该计数器能够在每个时钟的上升沿按十三进制顺序计数,并在达 到最大计数值时自动归零,实现了预期的功能。

3、在仿真过程中,我注意到了一些问题和挑战。例如,在设置仿真参数时,需 要确保时钟信号的频率和脉冲宽度符合设计要求,以确保仿真结果的准确性。 此外,仿真过程中还需要考虑电路中可能存在的干扰因素,以及如何处理这些 干扰对仿真结果的影响。

4、通过这次实验,我不仅加深了对JK触发器和十三进制计数器的理解,还提高 了使用Multisim软件进行数字电路设计和仿真的技能。我将继续努力学习,不 断提升自己在数字电路设计和仿真方面的能力,以应对更复杂的电路设计和仿 真任务。 总体而言,本次实验提高了对数字电路设计和仿真的理解,同时也锻炼了解决 问题的能力。

致谢

在此,我要向我的导师11老师表示最诚挚的感谢。在整个实验报告撰写的 过程中,1老师始终给予我悉心的指导和耐心的解答。他渊博的学识、对专业的 热情与执着,以及严谨认真的工作态度,都对我产生了深远的影响。他的亲历亲 为、追求完美的精神,不仅教会了我专业知识,更传授了我做人的道理。同时, 我也要感谢所有在实验过程中给予我们指导和帮助的老师们。是您们的专业知识 和丰富经验,为我们指明了方向,提供了宝贵的建议。您们的严谨治学态度和无 私奉献的精神,是我们学习的楷模,让我们在实验过程中收获满满,受益匪浅。

1599

1599

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?