module LTC2344(

input sys_clk,//FPGA 50MHz的时钟

input sys_rst_n,

input busy,//正在转换标识

input sdo0,

input sdo1,

input sdo2,//三个二进制给FPGA

output wire cs,//始终保持为0

output reg cnv,//采样开始标志

output reg scki,//采样时钟频率暂定为25MHz,最大可以是100MHz。

output reg sdi,//输入电压范围选取0~2.048V,sdi定为000_001_001_001,第四通道不用

output reg [15:0] data,

output reg [15:0] data1,

output reg [15:0] data2

);

assign cs=1'b0;

reg [5:0] cnt;

always@(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

begin

cnt<=6'd1;

cnv<=1'b0;

scki<=1'b0;

sdi<=1'b0;

end

else if(busy)

begin

cnt<=6'd1;

cnv<=1'b1;

scki<=1'b0;

sdi<=1'b0;

end

else begin

cnv<=1'b0;

if(cnt<6'd49) begin

scki<=~scki;

cnt<=cnt+1'b1;

end

else scki<=1'b0;

case(cnt)//sdi定为000_001_001_001,第四通道不用

6'd1:begin

sdi<=1'b0;data[15]<=sdo0;data1[15]<=sdo1;data2[15]<=sdo2;end

6'd2:begin

sdi<=1'b0;data[15]<=sdo0;data1[15]<=sdo1;data2[15]<=sdo2;end

6'd3:begin

sdi<=1'b0;data[14]<=sdo0;data1[14]<=sdo1;data2[14]<=sdo2;end

6'd4:begin

sdi<=1'b0;data[14]<=sdo0;data1[14]<=sdo1;data2[14]<=sdo2;end

6'd5:begin

sdi<=1'b0;data[13]<=sdo0;data1[13]<=sdo1;data2[13]<=sdo2;end

6'd6:begin

sdi<=1'b0;data[13]<=sdo0;data1[13]<=sdo1;data2[13]<=sdo2;end

6'd7:begin

sdi<=1'b0;data[12]<=sdo0;data1[12]<=sdo1;data2[12]<=sdo2;end

6'd8:begin

sdi<=1'b0;data[12]<=sdo0;data1[12]<=sdo1;data2[12]<=sdo2;end

6'd9:begin

sdi<=1'b0;data[11]<=sdo0;data1[11]<=sdo1;data2[11]<=sdo2;end

6'd10:begin

sdi<=1'b1;data[11]<=sdo0;data1[11]<=sdo1;data2[11]<=sdo2;end

6'd11:begin

sdi<=1'b1;data[10]<=sdo0;data1[10]<=sdo1;data2[10]<=sdo2;end

6'd12:begin

sdi<=1'b0;data[10]<=sdo0;data1[10]<=sdo1;data2[10]<=sdo2;end

6'd13:begin

sdi<=1'b0;data[9]<=sdo0;data1[9]<=sdo1;data2[9]<=sdo2;end

6'd14:begin

sdi<=1'b0;data[9]<=sdo0;data1[9]<=sdo1;data2[9]<=sdo2;end

6'd15:begin

sdi<=1'b0;data[8]<=sdo0;data1[8]<=sdo1;data2[8]<=sdo2;end

6'd16:begin

sdi<=1'b1;data[8]<=sdo0;data1[8]<=sdo1;data2[8]<=sdo2;end

6'd17:begin

sdi<=1'b1;data[7]<=sdo0;data1[7]<=sdo1;data2[7]<=sdo2;end

6'd18:begin

sdi<=1'b0;data[7]<=sdo0;data1[7]<=sdo1;data2[7]<=sdo2;end

6'd19:begin

sdi<=1'b0;data[6]<=sdo0;data1[6]<=sdo1;data2[6]<=sdo2;end

6'd20:begin

sdi<=1'b0;data[6]<=sdo0;data1[6]<=sdo1;data2[6]<=sdo2;end

6'd21:begin

sdi<=1'b0;data[5]<=sdo0;data1[5]<=sdo1;data2[5]<=sdo2;end

6'd22:begin

sdi<=1'b1;data[5]<=sdo0;data1[5]<=sdo1;data2[5]<=sdo2;end

6'd23:begin

sdi<=1'b1;data[4]<=sdo0;data1[4]<=sdo1;data2[4]<=sdo2;end

6'd24:begin

sdi<=1'b0;data[4]<=sdo0;data1[4]<=sdo1;data2[4]<=sdo2;end

6'd25:begin

sdi<=1'b0;data[3]<=sdo0;data1[3]<=sdo1;data2[3]<=sdo2;end

6'd26:begin

sdi<=1'b0;data[3]<=sdo0;data1[3]<=sdo1;data2[3]<=sdo2;end

6'd27:begin

sdi<=1'b0;data[2]<=sdo0;data1[2]<=sdo1;data2[2]<=sdo2;end

6'd28:begin

sdi<=1'b0;data[2]<=sdo0;data1[2]<=sdo1;data2[2]<=sdo2;end

6'd29:begin

sdi<=1'b0;data[1]<=sdo0;data1[1]<=sdo1;data2[1]<=sdo2;end

6'd30:begin

sdi<=1'b0;data[1]<=sdo0;data1[1]<=sdo1;data2[1]<=sdo2;end

6'd31:begin

sdi<=1'b0;data[0]<=sdo0;data1[0]<=sdo1;data2[0]<=sdo2;end

6'd32:begin

sdi<=1'b0;data[0]<=sdo0;data1[0]<=sdo1;data2[0]<=sdo2;end

default:sdi<=1'b0;

endcase

end

endmodule1.上述代码为采用三个通道的驱动程序。测试代码TestBench如下

`timescale 1ns/1ns

module LTC2344_tb();

parameter T=20;

reg sys_clk;

reg sys_rst_n;

reg busy;

reg sdo0;

reg sdo1;

reg sdo2;

wire cs;

wire cnv;

wire scki;

wire sdi;

wire [15:0]data;

wire [15:0]data1;

wire [15:0]data2;

always #(T/2) sys_clk=~sys_clk;

initial begin

sys_clk=1'b0;

sys_rst_n=1'b0;

busy=1'b0;

sdo0=1'b0;

sdo1=1'b0;

sdo2=1'b0;

#20 begin

sys_rst_n=1'b1;

busy=1'b1;

end

#1405 begin

busy=1'b0;

sdo0=1'b0;

sdo1=1'b1;

sdo2=1'b0;

end

#40 begin

sdo0=1'b1;

sdo1=1'b0;

sdo2=1'b1;

end

#40 begin

sdo0=1'b0;

sdo1=1'b0;

sdo2=1'b0;

end

#1000 begin

busy=1'b1;

sdo0=1'b0;

sdo1=1'b0;

sdo2=1'b0;

end

#1405 begin

busy=1'b0;

sdo0=1'b0;

sdo1=1'b1;

sdo2=1'b0;

end

#40 begin

sdo0=1'b1;

sdo1=1'b0;

sdo2=1'b1;

end

#40 begin

sdo0=1'b0;

sdo1=1'b0;

sdo2=1'b0;

end

#1000 begin

busy=1'b1;

sdo0=1'b0;

sdo1=1'b0;

sdo2=1'b0;

end

#1405 begin

busy=1'b0;

sdo0=1'b0;

sdo1=1'b1;

sdo2=1'b0;

end

#40 begin

sdo0=1'b1;

sdo1=1'b0;

sdo2=1'b1;

end

#40 begin

sdo0=1'b0;

sdo1=1'b0;

sdo2=1'b0;

end

#1000 begin

busy=1'b1;

sdo0=1'b0;

sdo1=1'b0;

sdo2=1'b0;

end

end

LTC2344 u_LTC2344(

.sys_clk(sys_clk),

.sys_rst_n(sys_rst_n),

.busy(busy),

.sdo0(sdo0),

.sdo1(sdo1),

.sdo2(sdo2),

.cs(cs),

.cnv(cnv),

.scki(scki),

.sdi(sdi),

.data(data),

.data1(data1),

.data2(data2)

);

endmodule

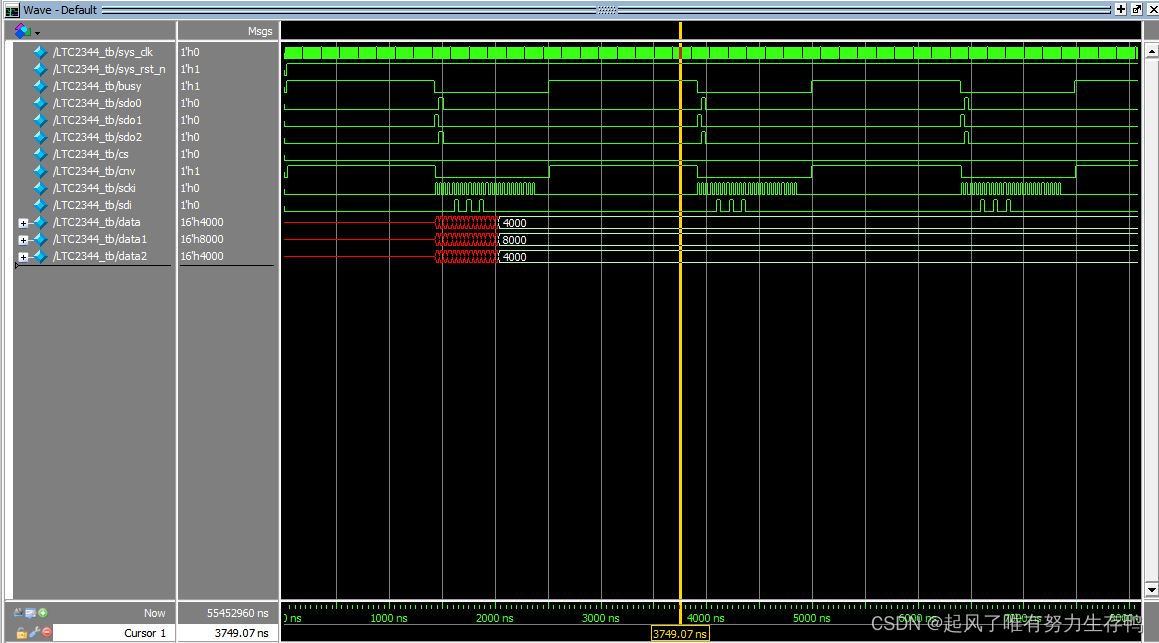

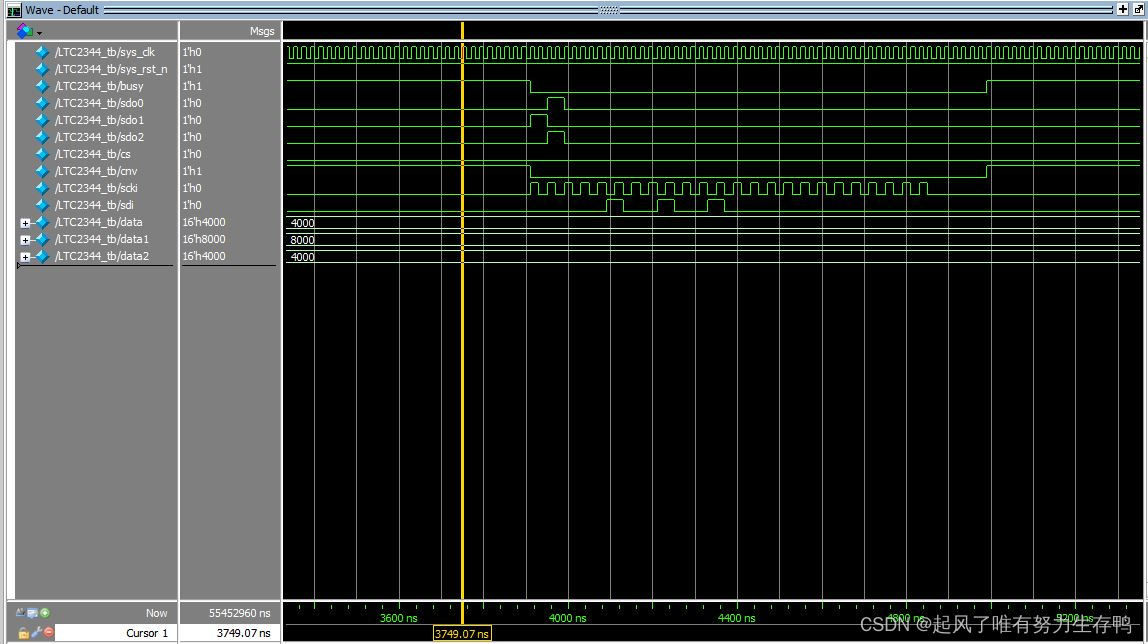

2.采用联合仿真,在modelsim下运行得到仿真图

1176

1176

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?