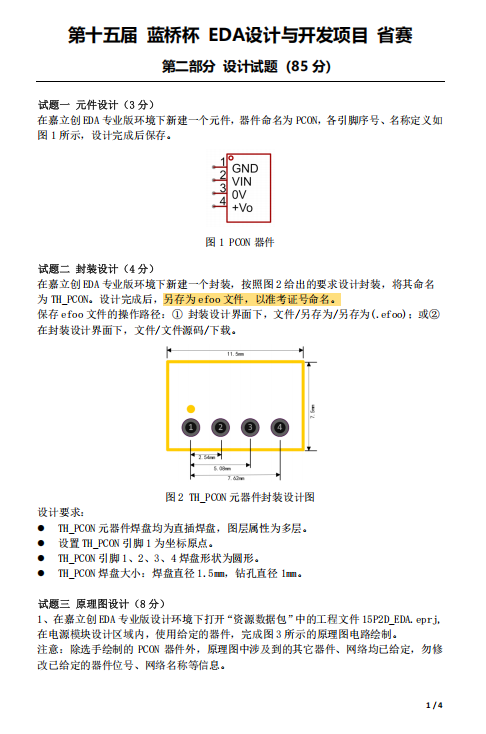

一、符号库设计

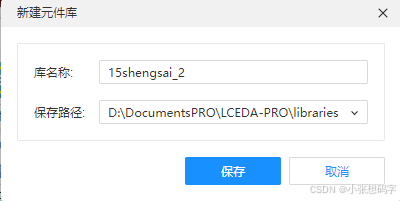

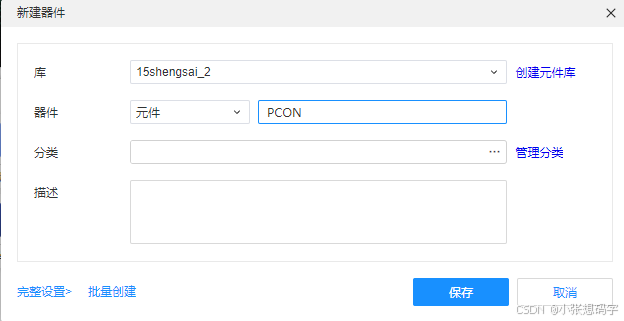

首先要明确,在设计元器件符号之前,需要新建一个元件库,“文件→新建→元件库”,按照要求进行命名,一般为自己的准考证号。

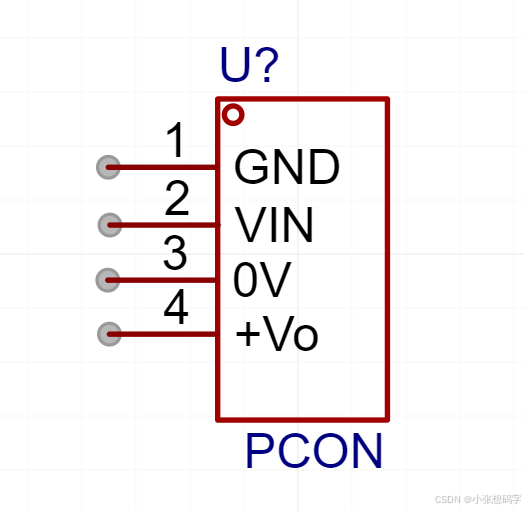

再次在“文件→新建→元件→选择新建的库,定义元件名称,确认”。选择矩形(Alt+R),以原点为中心点→放置引脚(Alt+P),逆时针顺序放置4个引脚,依次更改引脚名称,保存,完成。

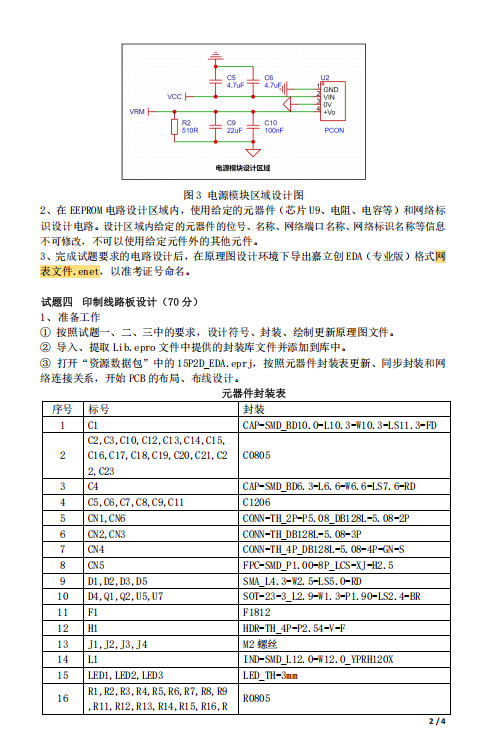

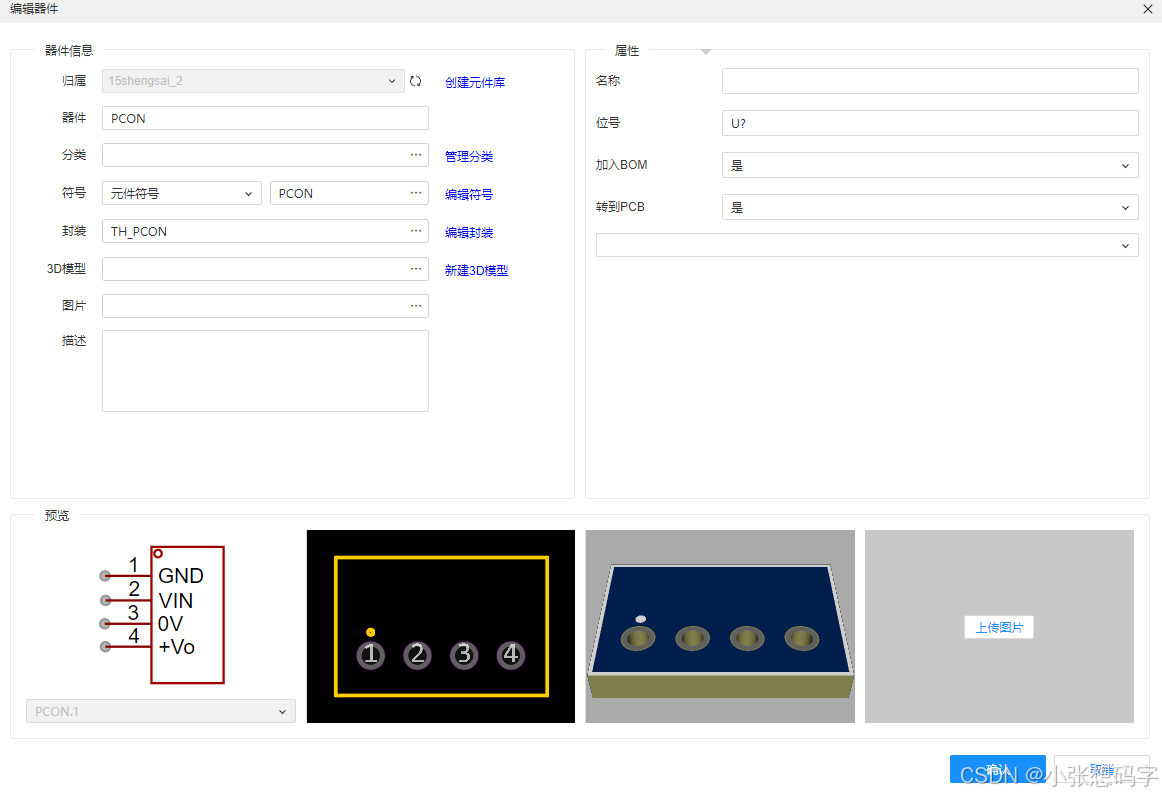

二、封装库设计

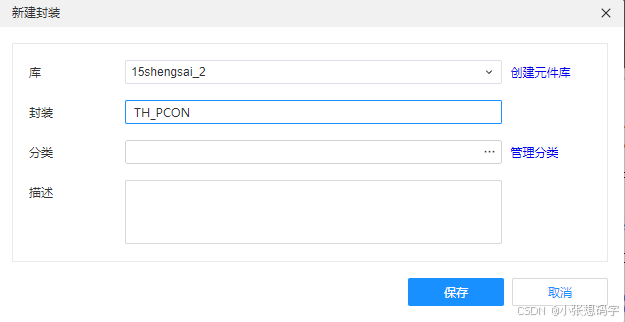

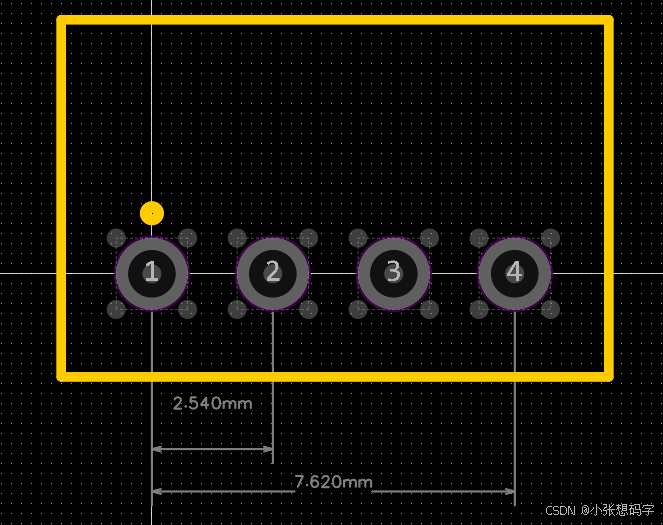

文件→新建→封装→选择新建的库,定义封装名称,确认

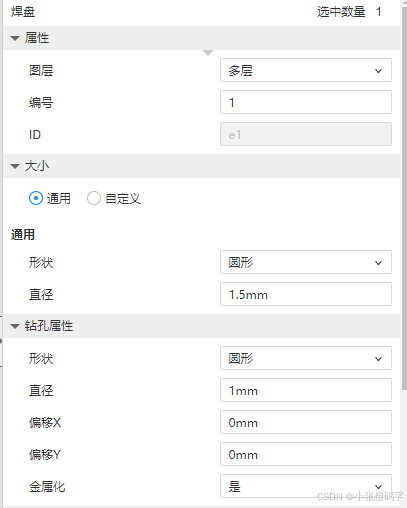

根据要求进行绘制,放置一个焊盘(Alt+P),属性→图层为多层,形状为圆形,设置直径为1.5mm,钻孔直径为1mm,复制--粘贴,逆时针放置5个焊盘,更改编号;

工具→智能尺寸,选中1号焊盘中心位置,按住Ctrl,继续选择其他焊盘,依次进行间距更改,完成如图所示的焊盘位置摆放;

放置→线条→矩形,属性→此时设置的线宽为0.2mm,位于顶层丝印层,再次选择放置→画布原点→从第一个焊盘,完成1引脚在坐标原点上。保存。

与器件PCON进行关联:选择下方的库,找到试题一保存的器件PCON,编辑→封装一栏选择...,找到封装为,确认,再次确认,完成关联。

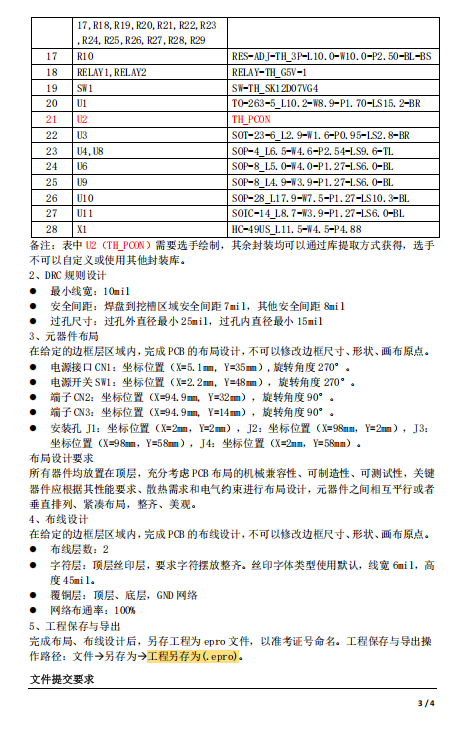

三、原理图设计

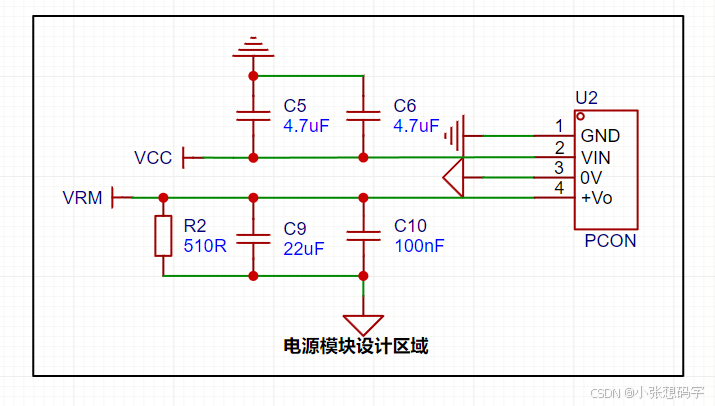

1、电源模块设计

完全按照所给图3进行原理图设计操作,不需要更改任何器件信息,如果存在导入PCON器件的编号不是“U2”,需要更改,其他器件均不修改。

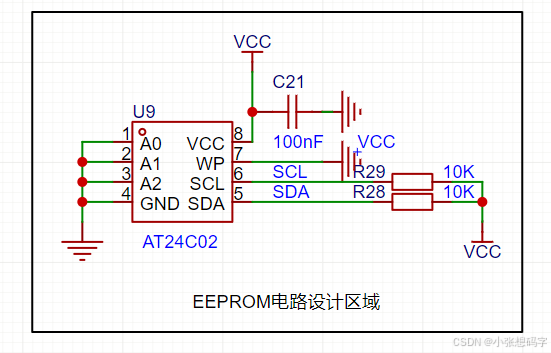

2、 EEPROM电路设计

分析:通过I2C接口与微控制器或其他设备进行通信。

EEPROM(AT24C02):存储器,保存数据,其中SDA为I2C数据线,用于数据传输;SCL为I2C时钟线,用于同步数据传输;WP为写保护,防止意外写入;A0-A2为地址引脚,用于设置总线上的设备地址。

电阻R28和R29:上拉电阻,确保信号线在没有信号时保持高电平。

电容C21:滤波电容,稳定VCC电源。

总结:该EEPROM电路通过AT24C02芯片实现非易失性数据存储,使用I2C接口与主设备通信。电阻R28和R29作为上拉电阻,确保I2C信号线的正常工作。电容C21用于滤除电源噪声,确保电源稳定。设计时需要考虑I2C总线速度、写保护功能和设备地址设置等因素,以确保电路的可靠性和稳定性。

3、元器件封装

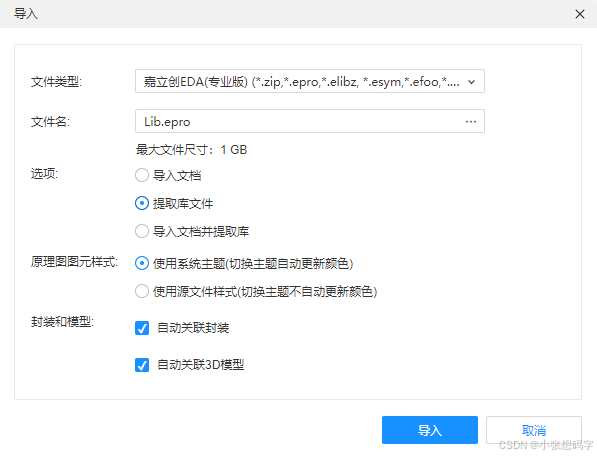

导入文件夹中的Lib.epro封装库文件,具体设置“文件→导入→嘉立创专业版→Lib.epro”,选择提取库文件,确认

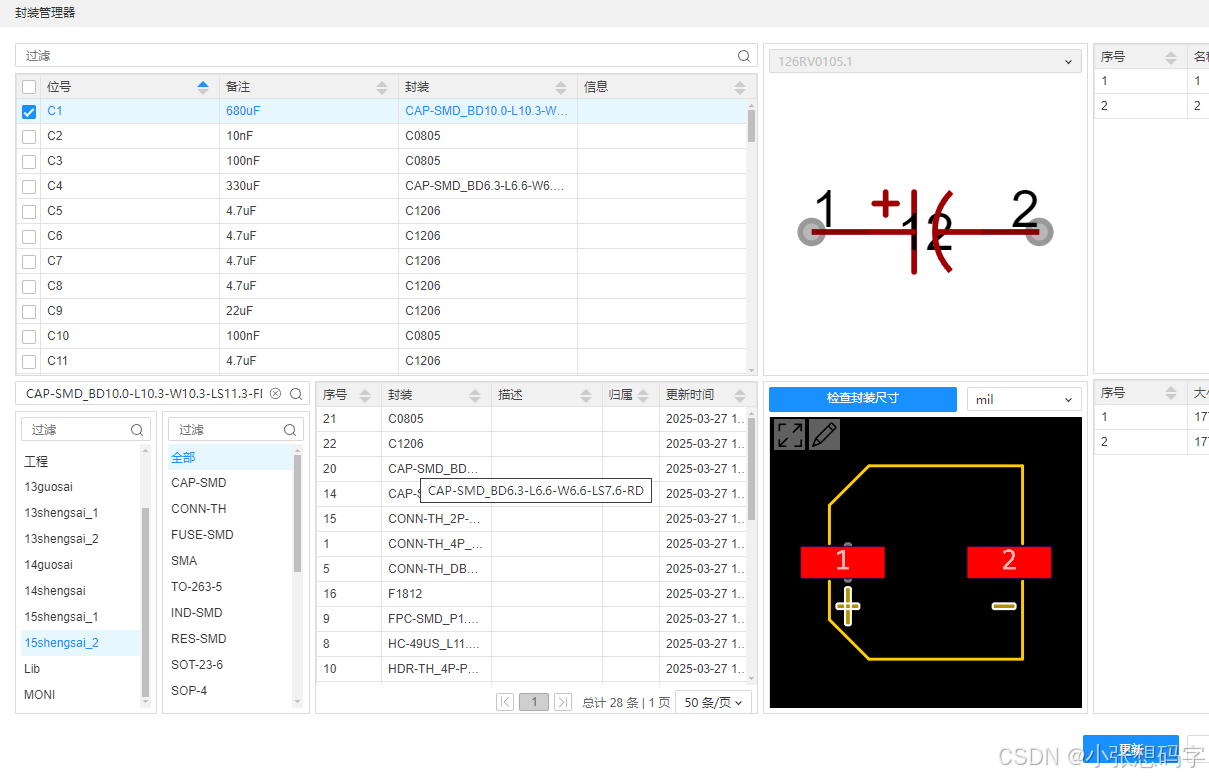

工具→封装管理器(Alt+F),每次修改都需要进行更新,按照元器件封装表进行逐一修改即可。

注:此处可进行二次检查,防止在布局过程中会出现元器件封装不匹配情况,导致布局布线出现错误。

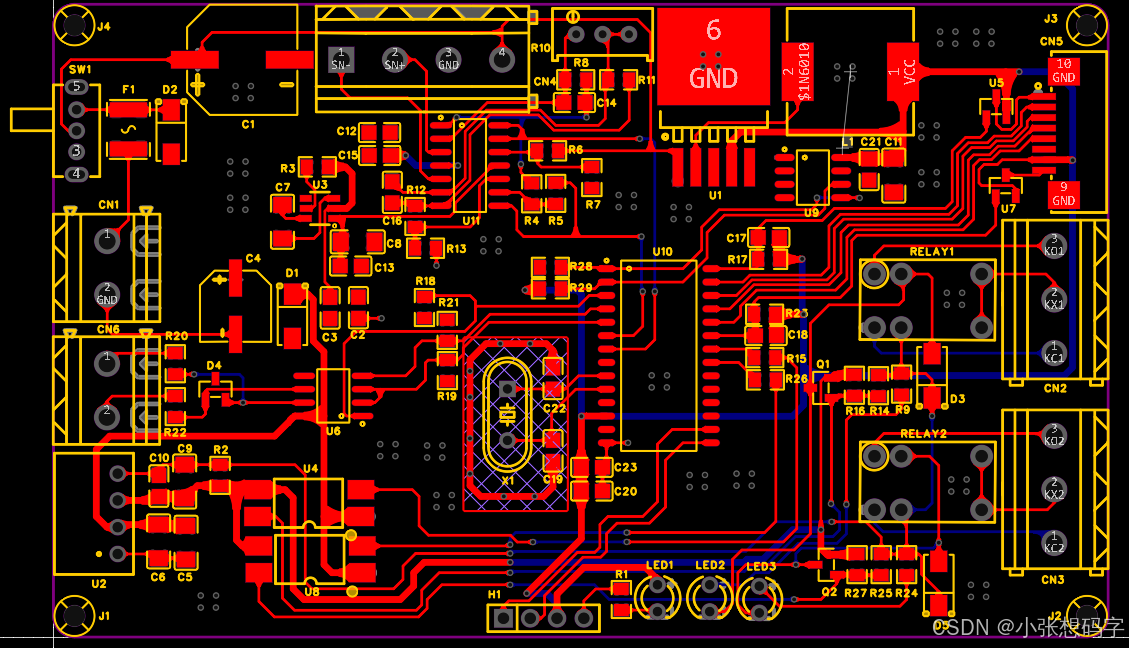

四、布局布线设计

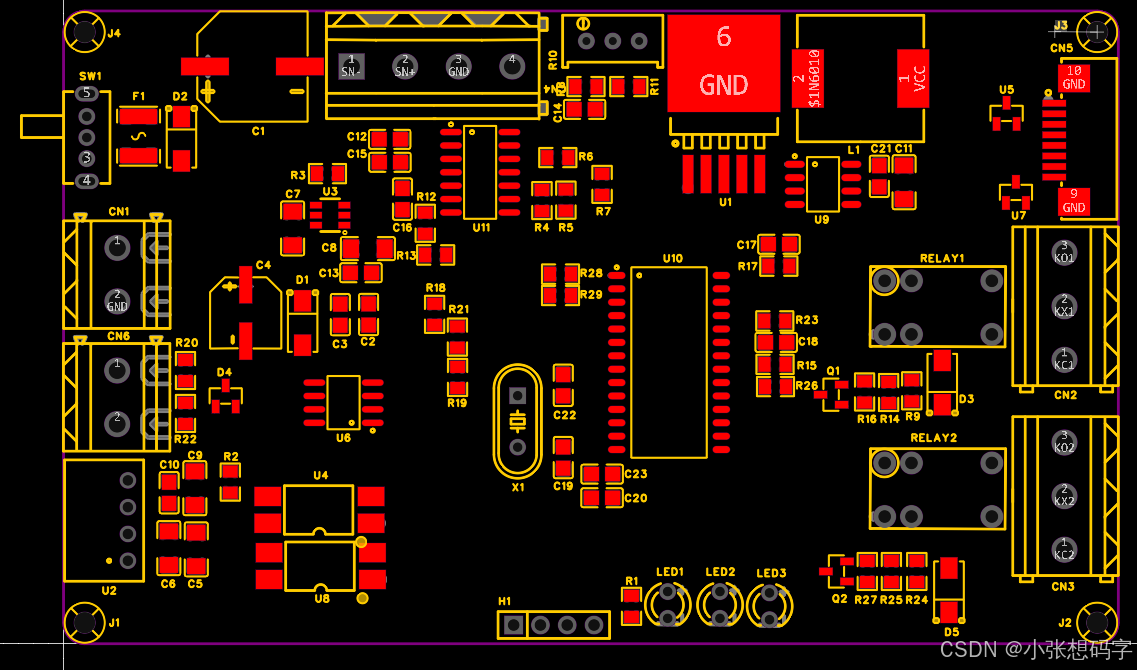

1、布局

按照要求对要求的元器件进行固定位置设置,在设置好参数后需要锁定,防止后续操作会变更位置。其余元器件按照模块化进行摆放,以原理图的位置和顺序,保证元件之间相互平行或垂直排列,元器件全部置于顶层。

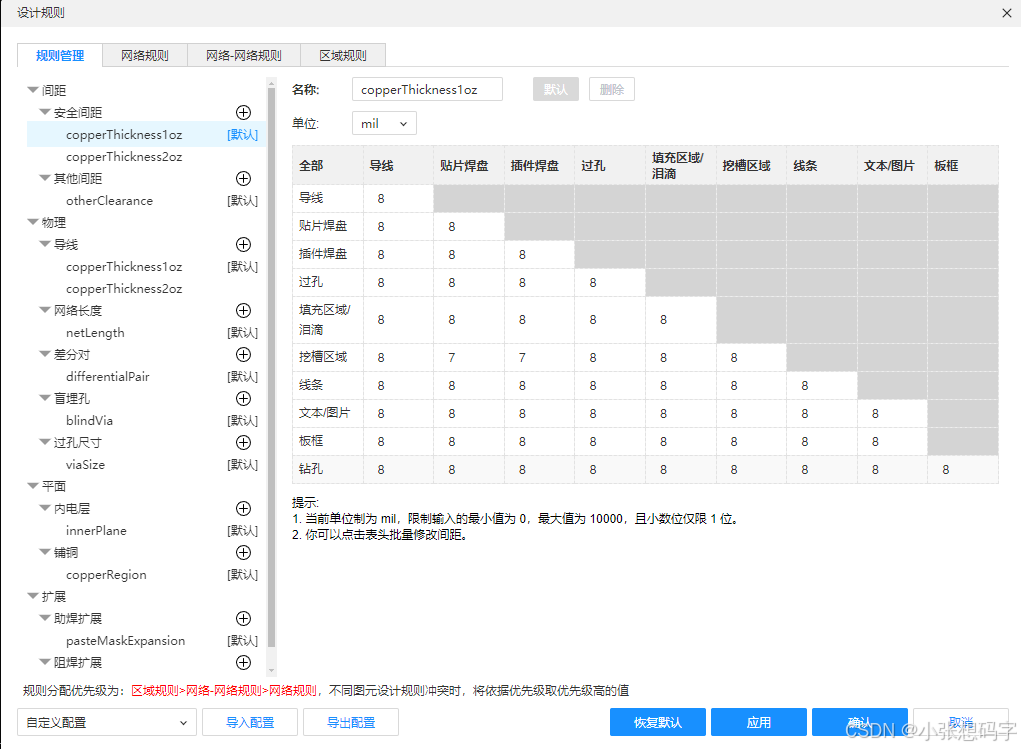

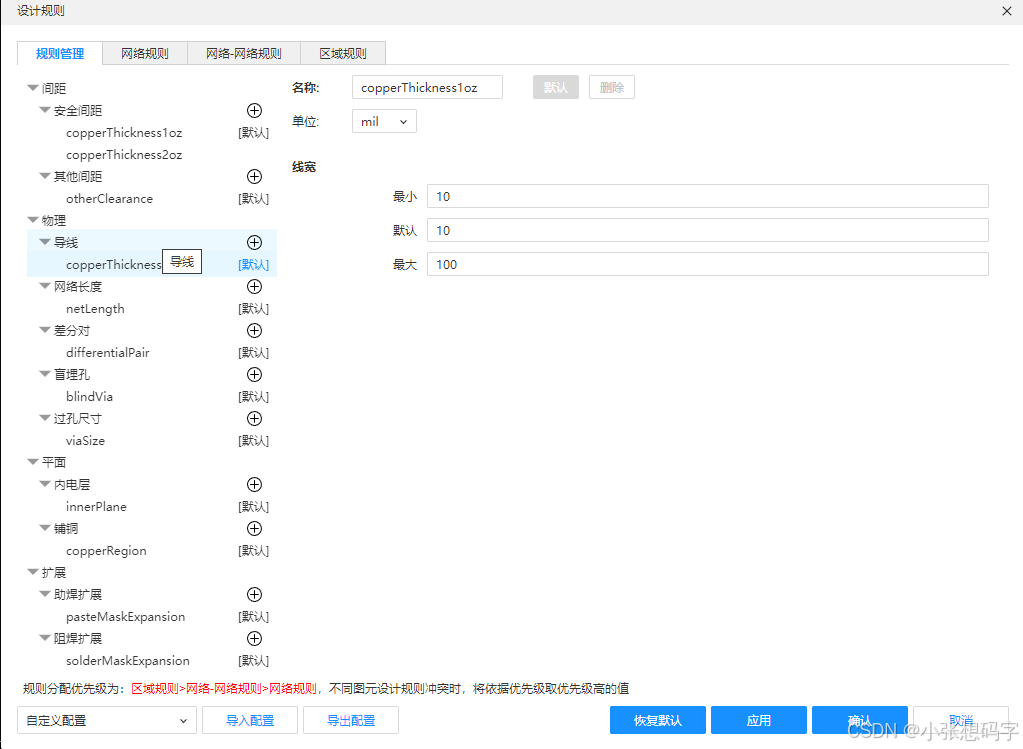

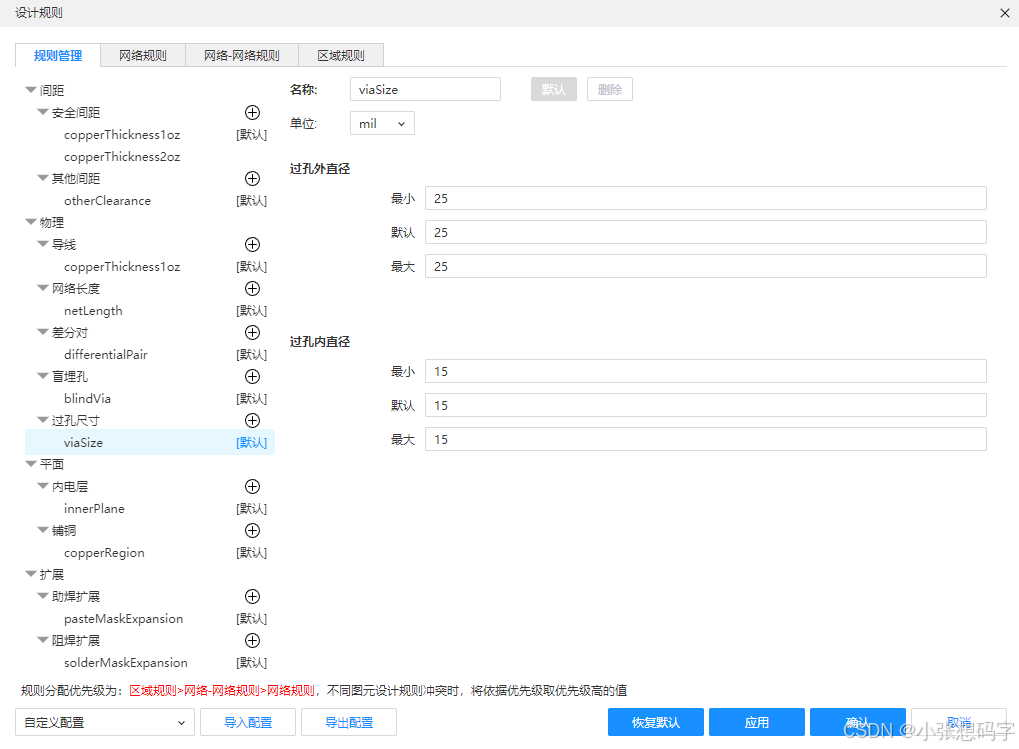

2、布线DRC规则

导线最小宽度10mil,电源线需要加粗(25-40mil),一般情况下,笔者选择25mil;

安全间距:焊盘到挖槽区域7mil,其余均为8mil。

过孔尺寸最小为15mil,最大为25mil。

设置→设计规则,分别选择间距→安全间距,物理→导线,过孔尺寸

3、布线设计

隐藏GND连接飞线,优先短飞线,再处理长飞线;

默认线宽10mil,电源部分线宽在20-30mil之间,根据相应引脚位置动态调整,对于电源部分和开关部分可以使用3V3铺铜进行连接处理。

晶振进行包地操作,GND导线进行加粗处理,打过孔,多层禁止铺铜。

添加泪滴,圆弧状。

GND铺铜,顶层和底层均要。

五、文件提交

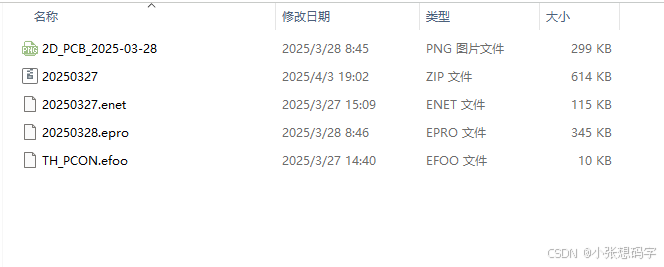

文件总共封装文件.efoo,网表文件.enet,2D图片文件.png,工程文件.epro,按照试题要求进行更改名称,打包压缩上传,完成。

导出网表:导出→网表→网表类型:嘉立创EDA(专业版).enet→导出。

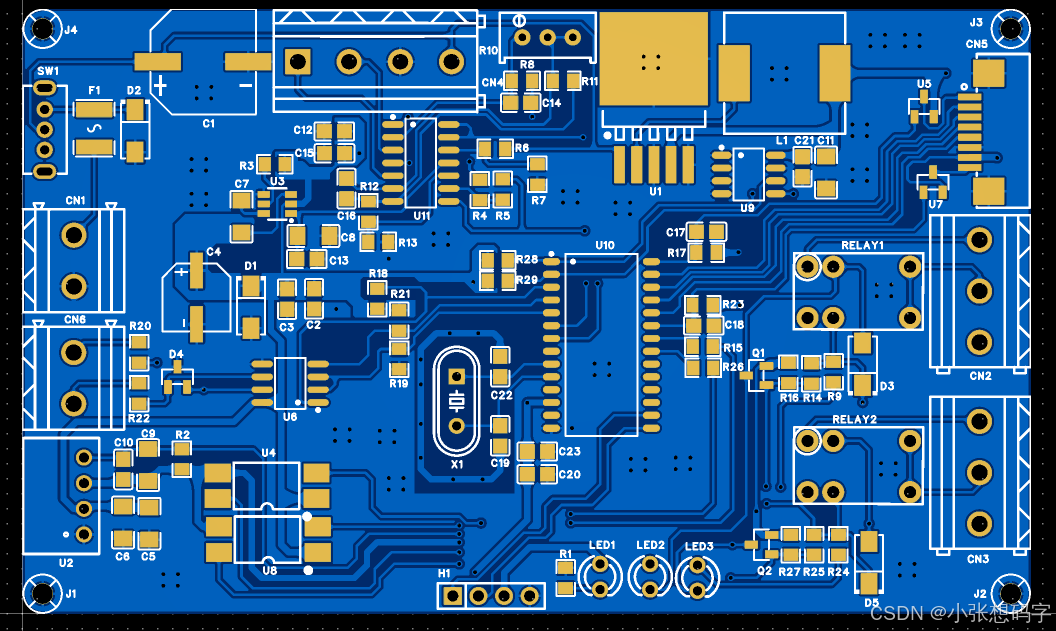

导出2D图片:在PCB界面下选择视图→2D预览,再选择文件→导出→PNG,修改名称,保存完成。

导出文件和压缩包汇总:

第十五届蓝桥杯EDA省赛第二场已完成。 本文内容全部为学习记录,仅作为学习使用。

1031

1031

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?