注:内容参考王道2024考研复习指导

数制与编码

在计算机系统内部,所有信息都是用二进制进行编码的,这样做的原因有以下几点。

- 二进制只有两种状态,使用有两个稳定状态的物理器件就可以表示二进制数的每一位,制造成本比较低,例如用高低电平或电荷的正负极性都可以很方便地表示0和1。

- 二进制位1和0正好与逻辑值“真”和“假”相对应,为计算机实现逻辑运算和程序中的逻辑判断提供了便利条件。

- 二进制的编码和运算规则都很简单,通过逻辑门电路能方便地实现算术运算。

进位计数制

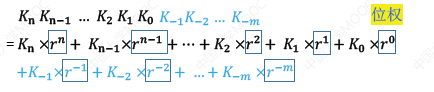

r进制计数法法

基数:每个数码位用到的不同符号的个数,r进制的基数为r。

位权:用基数r的i次幂表示。

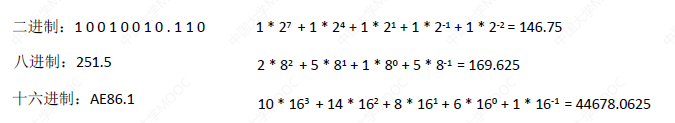

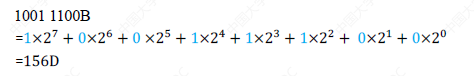

任意进制转十进制

需要将每位的数值和对应位权相乘再求和

二进制转八进制、十六进制

二进制转八进制,需要每3位一组,每组转换成对应的八进制符号。八进制转二进制则将每位八进制转换成对应3位的二进制。

二进制转十六进制,需要每4位一组,每组转换成对应的十六进制符号。十六进制转二进制则将每位十六进制转换成对应的4位二进制。

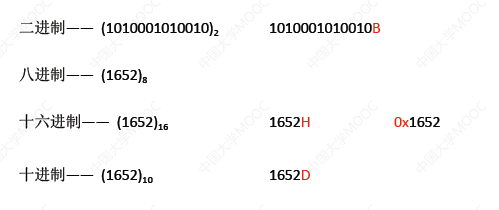

各种进制的常见书写方式

二进制以下标2或者末尾B作为标识

八进制用下标8作为标识

十六进制以下标16或末尾H或者开头0x作为标识

十进制以下标10或者末尾D作为标识

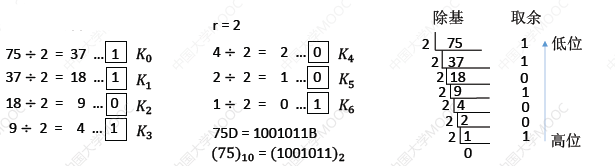

十进制转任意进制

需要整数部分和小数部分分开计算后再合并

以十进制转二进制为例:

- 整数部分,采用除基取余法。

用十进制数除以目标进制的基数,可以得到一个商和一个余数,余数作为目标进制数的低位表示,商作为下一次的被除数再次除以基数,循环直到商得零。

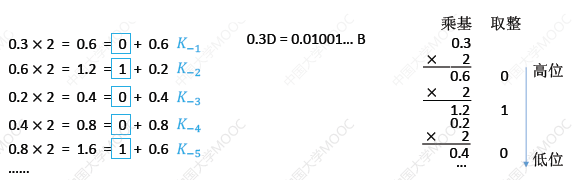

- 小数部分,采用乘基取整法(小数部分可能会得到无限小数,需要按精度舍入)。

用十进制的小数数乘上目标进制的基数,可以得到一个积,取出积的整数部分,作为目标进制的小数部分的高位表示,将积剩余部分作为乘数进行下一次的乘基取整。直到乘积为1.0时结束或者达到精度要求。

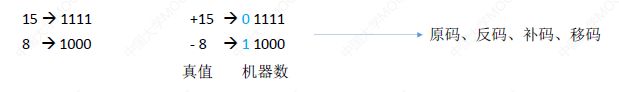

真值和机器数

真值:符合人类习惯的数字,带正负号的数。

机器数:数字实际存到机器的形式,正负号需要被“数字化”。

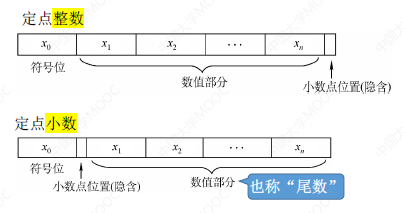

定点数的编码表示

定点数,小数点的位置固定,例如十进制下的常规计数,996.007

浮点数,小数点的位置不固定,例如十进制下的科学技术法表示,9.96007*10^2

二进制的定点数、浮点数与之类似。

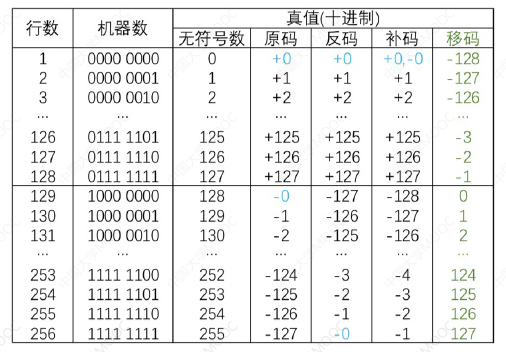

无符号数的表示

通常只有无符号整数,没有无符号小数

无符号数:整个机器字长的全部二进制位均为数值位,没有符号位,相当于数的绝对值。

对于n位的无符号数,其表示范围为: 0 ∼ 2 n − 1 0 \sim 2^{n-1} 0∼2n−1

有符号数的表示

- 整数+小数:例如1.24、10.34,小数点在指定某个位置

有符号数的定点表示

- 纯整数:例如整数100,小数点其实在最后一位,所以忽略不写

- 纯小数:例如:0.123,小数点固定在最高位

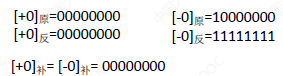

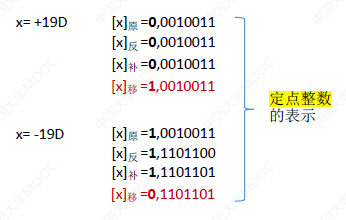

注:可用原码、反码、补码三种方式来表示定点整数和定点小数。还可用移码表示定点整数。若真值为x,则用[x]原、[x]反、[x]补、[x]移分别表示真值所对应的原码、反码、补码、移码。

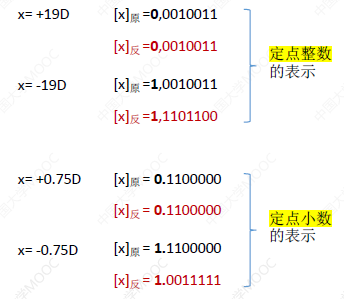

原码

用尾数表示真值的绝对值,符号位“0/1”对应“正/负”。若机器字长为n+1位,则尾数占n位。

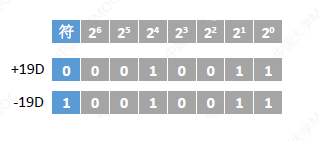

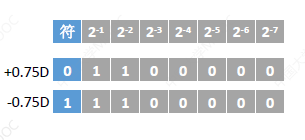

对于+19D和-19D,字长为8位的机器数原码表示如上图所示,-19D的原码可写为[x]原=10010011,第一位为符号位。

对于-0.75D和+0.75D,字长为8位的机器数原码表示如上图所示,-0.75D的原码可写为[x]原=1.1100000,小数点前的一位为符号位。

-

若机器字长为n+1位,原码整数的表示范围: − ( 2 n − 1 ) ≤ x ≤ 2 n − 1 -(2^n-1) \leq x \leq 2^n-1 −(2n−1)≤x≤2n−1,关于原点对称。真值有+0和-0两种形式。

-

若机器字长为n+1位,原码小数的表示范围: − ( 1 − 2 − n ) ≤ x ≤ 1 − 2 − n -(1-2^{-n}) \leq x \leq 1-2^{-n} −(1−2−n)≤x≤1−2−n,关于原点对称。真值有+0和-0两种形式。

反码

反码,若符号位为0,则反码与原码相同;若符号位为1,则数值位全部取反。

反码只是原码转变为补码的一个中间状态,实际无用。

反码的表示范围和原码的表示范围一致。

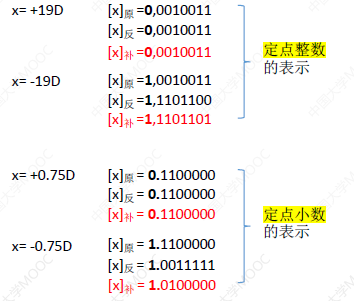

补码

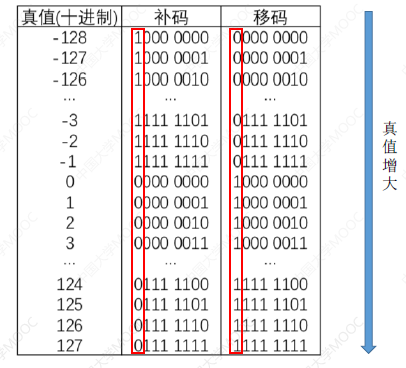

正数的补码等于原码,负数的补码等于反码末位加1(考虑包括符号位在内的进位)。

将负数补码转回原码的方法相同,尾数取反,末位加1。即[[X]补]补=[X]原。

补码中,真值0只有一种表示形式。

定点整数补码[x]补=10000000表示 x = − 2 7 x=-2^7 x=−27。

-

若机器字长为n+1位,补码整数的表示范围: − ( 2 n ) ≤ x ≤ 2 n − 1 -(2^n) \leq x \leq 2^n-1 −(2n)≤x≤2n−1,比原码表示多一个 − 2 n -2^n −2n(即原来-0的表示,人为规定为 − 2 n -2^n −2n)。

-

若机器字长为n+1位,补码小数的表示范围: − 1 ≤ x ≤ 1 − 2 − n -1 \leq x \leq 1-2^{-n} −1≤x≤1−2−n,比原码表示多一个-1。

注:对于已知[X]补,求[-X]补,则需要符号位和数值位取反(全部取反),末尾加1可以得到。

或者可以找出[X]补最右边的1,将其左边(包括符号位,不包括本身)的数字全部取反,也可以得到。

移码

移码,在补码的基础上将符号位取反。

注:移码只能用于表示整数

移码的表示范围与补码的定点整数的表示范围相同。

移码表示的整数很方便进行大小对比,如下图所示:

用几种码表示定点整数

原码和反码的真值0有两种表示,补码和移码的真值0只有一种表示,补码和移码可以多表示一个负数。

##零扩展&符号扩展

为什么需要对数据进行长度扩展?

- ALU的位数是固定的,运算前可能需要把短数据扩展为长数据

- 通用寄存器位数是固定的,把数据存入寄存器时,可能需要进行长度扩展

- 主存内的各种数据长度不一,有时需要把短数据扩展为长数据

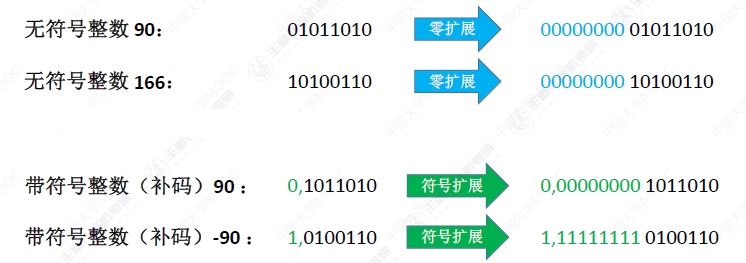

零扩展:适用于无符号整数,用0扩展高位

符号扩展:适用于带符号整数(补码),用符号位扩展高位

C语言中的强制类型转换

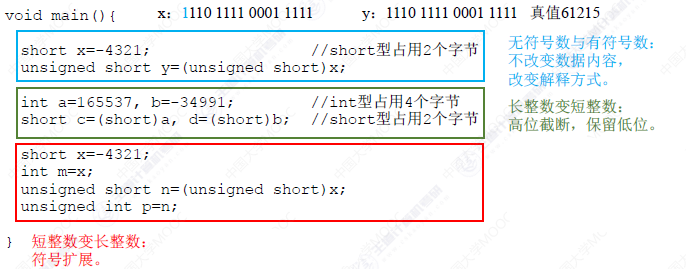

注:C语言中的定点整数使用补码存储的。

无符号数与有符号数:不改变数据内容,改变解释方式。

长整数变短整数:高位截断,保留低位。

短整数变长整数:符号扩展

注:若同时有无符号数和有符号数参与运算,则C语言标准规定按无符号数进行运算。

运算方法和运算电路

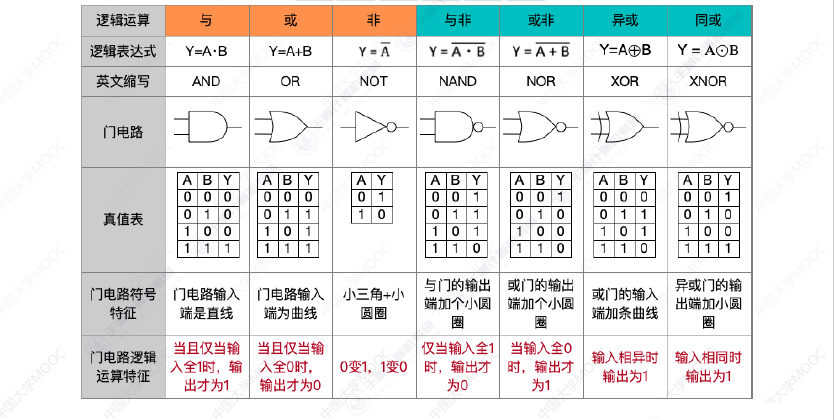

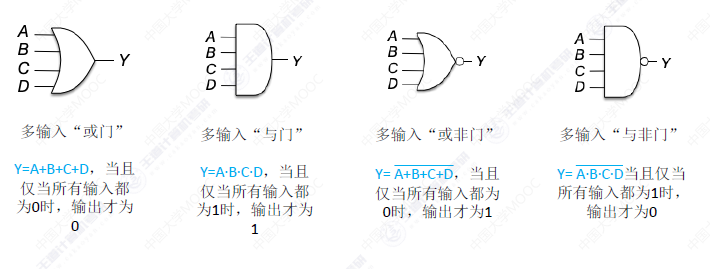

逻辑门电路基础

总结

门电路变形画法

加法器

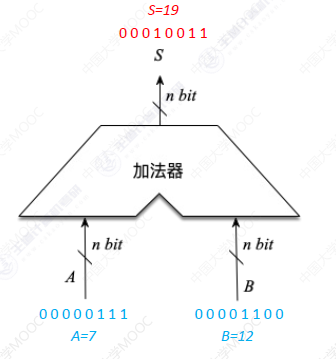

加法器的基本功能

7+12=19,用8bit表示被加数A、加数B、和S。

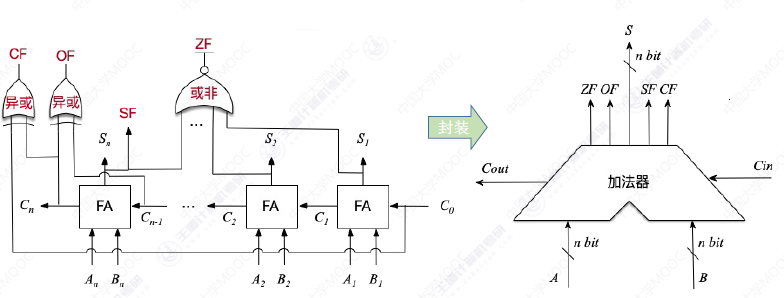

一位全加器

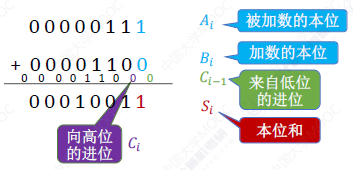

8bit的加法,每一位的加法计算过程如下所示,输入被加数的本位、加数的本位、来自低位的进位,输出本位和、向高位的进位。

其中,本位和 S i = A i ⊕ B i ⊕ C i − 1 S_i=A_i \oplus B_i \oplus C_{i-1} Si=Ai⊕Bi⊕Ci−1,输入中有奇数个1时输出1; C i = A i B i + ( A i ⊕ B i ) C i − 1 C_i=A_iB_i+(A_i \oplus B_i)C_{i-1} Ci=AiBi+(Ai⊕Bi)Ci−1,输入中至少2个1时输出1。

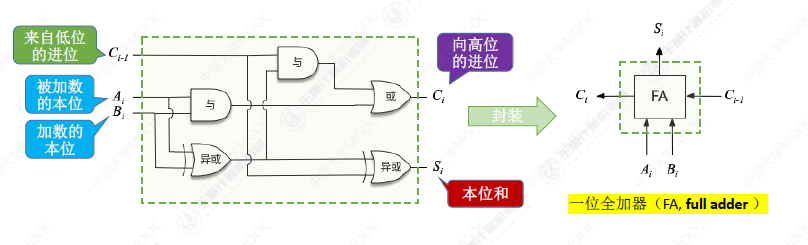

逻辑电路经过封装后便构成了一位全加器,如图所示。

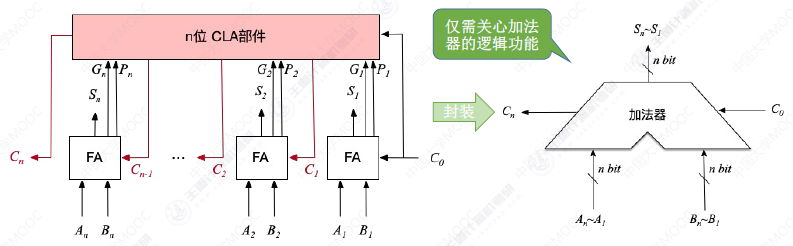

n bit加法器

把n个一位全加器串联起来,就可以进行两个n bit数的相加。

这种加法器的进位信息是串行产生的,位数越多,运算速度越慢。

- 两个输入端允许并行输入n bit,属于并行加法器

- 进位信息是串行产生的,属于串行进位加法器

综上,该加法器称为”串行进位的并行加法器“。

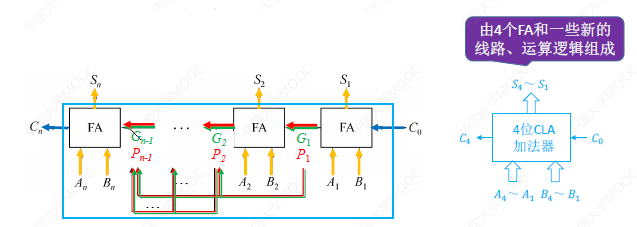

并行进位的并行加法器

并行进位的并行加法器,各级进位信号同时形成,又称为先行进位、同时进位。

并行进位的并行加法器,所有进位信息都是同时产生的,几乎没有延迟。特点是运算速度比“串行进位的并行加法器”更快。

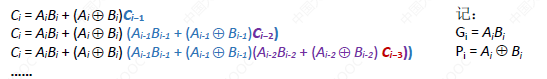

通过刚开始已有的信息可以展开得到每一位的进位。如下图所示:

结论:第i位向更高位的进位 C i C_i Ci可以根据被加数、加数的第 1 ∼ i 1 \sim i 1∼i位,再结合 C 0 C_0 C0即可确定。

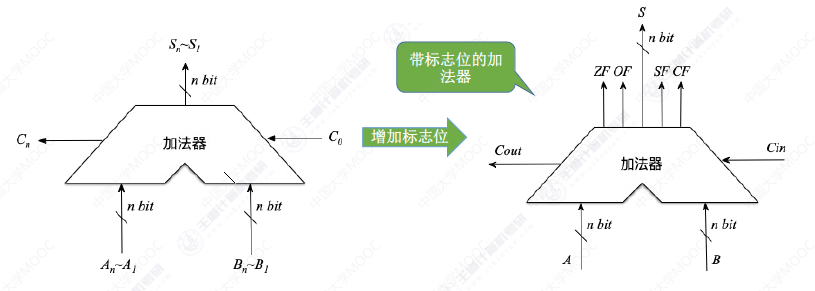

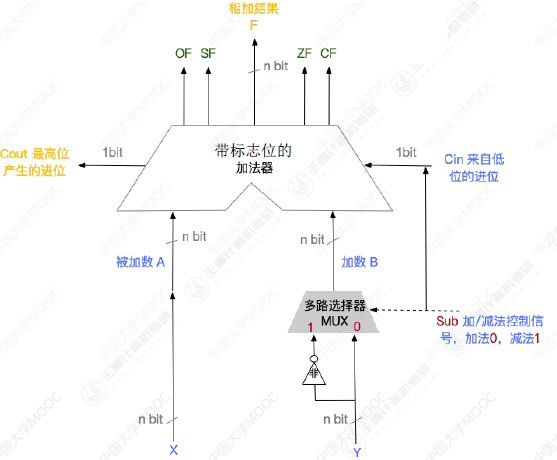

带标志位的加法器

各类表示说明如下:

- OF(Overflow Flag)溢出标志,用于判断带符号整数加减运算是否溢出。OF=1溢出;OF=0未溢出

- SF(Sign Flag)符号标志,用于判断带符号数加减运算结果的正负性。SF=1结果为负;SF=0结果为正

- ZF(Zero Flag)零标志,用于判断加减运算的结果是否为0。ZF=1表示结果为0;ZF=0表示结果不为0

- CF(Carry Flag)进位/借位标志,用于判断无符号数的加减运算是否溢出。CF=1溢出;CF=0未溢出

标志位的生成

O F = C n ⊕ C n − 1 OF=C_n \oplus C_{n-1} OF=Cn⊕Cn−1,最高位的进位异或次高位的进位,反应带符号数加减运算是否溢出。

S F = S n SF=S_n SF=Sn,取运算结果的最高位(符号位),反应带符号数加减运算的正负性。

Z F = S n + . . . + S 2 + S 1 ‾ ZF=\overline{S_n+...+S_2+S_1} ZF=Sn+...+S2+S1,仅当运算结果所有bit全为0时,ZF才为1,此时表示运算结果为0。

C F = C o u t ⊕ C i n = C n ⊕ C 0 CF=C_{out} \oplus C_{in}=C_n \oplus C_0 CF=Cout⊕Cin=Cn⊕C0,反应无符号数加减运算是否溢出。

多路选择器&三态门

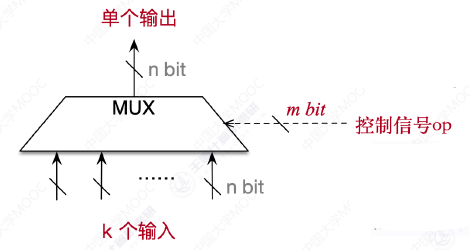

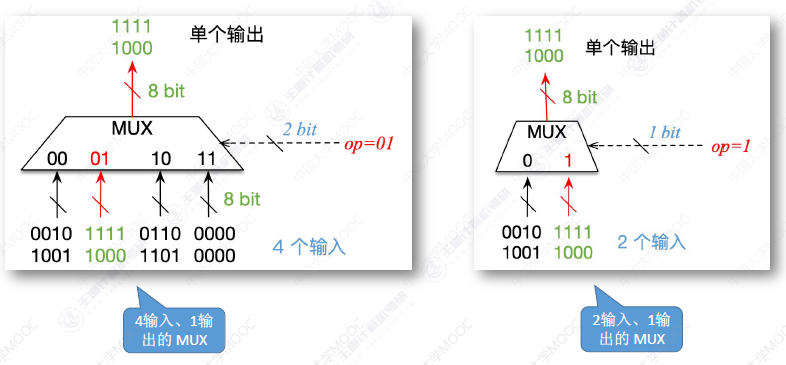

多路选择器

多路选择器(multiplexer,MUX),作用是在多个输入数据中,只允许其中一个数据通过MUX。

图形通常用“梯形”表示,有多个输入、一个输出、一个控制信号(梯形的更长的一边是输入端、更短的一边是输出端)

若有 k k k个输入,则控制信号的位数 m ≥ ⌈ log 2 k ⌉ b i t m \geq \lceil \log_2k \rceil \ bit m≥⌈log2k⌉ bit

注:在电路图中,控制信号常用英文缩写“XXXop”表示,图形常用“虚线箭头”。

示例如下:

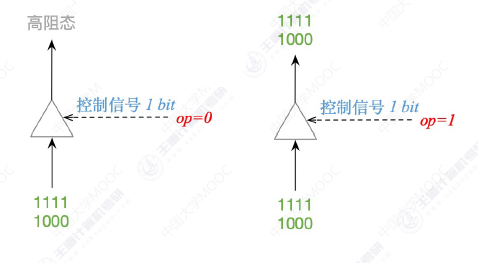

三态门

三态门,作用是根据控制信号决定是否让输入的数据通过。

图形是小三角。有一个输入、一个输出、一个控制信号。

三态门的控制信号通常只需要1bit。op=1表示允许数据通过;op=0表示不允许数据通过。

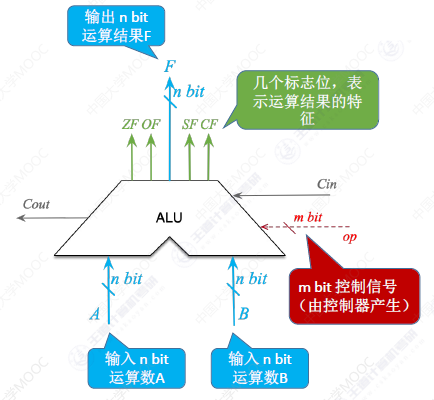

算数逻辑单元ALU

ALU是一种组合逻辑电路,实现了加/减/乘/除、与/或/非等功能。因此ALU是运算器的核心。

由于加减乘除等运算都要基于“加法”来实现,因此加法器是ALU的核心。

重点总结:

- 如果ALU支持k种功能,则控制信号位数 m ≥ ⌈ log 2 k ⌉ m \geq \lceil \log_2 k \rceil m≥⌈log2k⌉

- ALU的运算数、运算结果位数与计算机的机器字长相同

- ZF/OF/SF/CF标志位,用于表示本次运算结果的特征

- 标志信息送入PSW程序状态字寄存器(标志寄存器FR)

定点数的移位运算

移位:通过改变各个数码位和小数点的相对位置,从而改变各数码位的位权。可用移位运算实现乘法、除法。

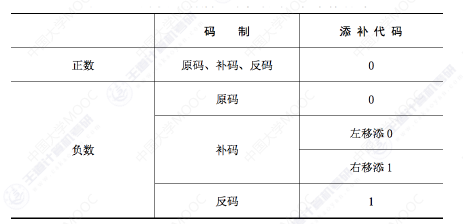

算术移位

计算机中的有符号数都是用补码表示的,对于有符号整数的移位操作应采用补码算术移位方式。规则如下:左移低位补0,若左移前后符号位不同,则发生溢出;右移高位补符号位,或低位舍弃的比特位为1,则会丢失精度。

注:下文关于三种码的算数移位,酌情阅读:

- 原码的算数移位,符号位保持不变,仅对数值位进行移位。

右移,高位补0,低位舍弃。若舍弃的位=0,则相当于÷2;若舍弃的位≠0,则会丢失精度;

左移,低位补0,高位舍弃。若舍弃的位=0,则相当于×2;若舍弃的位≠0,则会出现严重误差。

- 反码的算数移位

正数的反码与原码相同,因此对正数反码的移位运算也和原码相同。

负数的反码数值位与原码相反,因此负数反码的移位运算规则为:右移,高位补1,低位舍弃;左移,低位补1,高位舍弃。

- 补码的算数移位

正数的补码与原码相同,因此对正数补码的移位运算也和原码相同。

负数补码=反码末位+1,导致反码最右边几个连续的1都因进位而变为0,直到进位碰到第一个0为止。

规律为负数补码中,最右边的1及其右边同原码。最右边的1的左边同反码,即右移(同反码),高位补1,低位舍弃;左移(同原码),低位补0,高位舍弃。

总结如下:

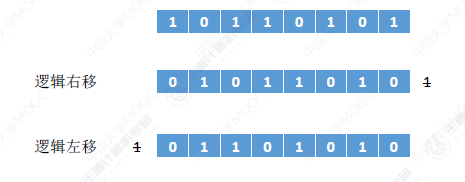

逻辑移位

逻辑右移:高位补0,低位舍弃。

逻辑左移:低位补0,高位舍弃。

可以把逻辑移位看作是对“无符号数”的算数移位。

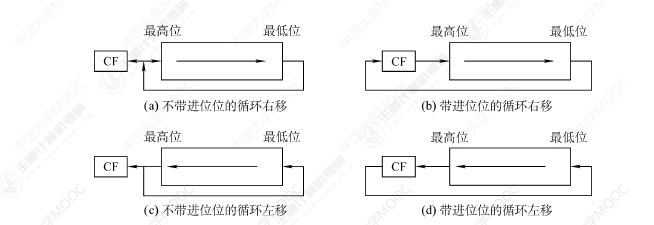

循环移位

不带进位位,用移出的位补上空缺;带进位位,移出的位放到进位位,原进位位补上空缺。

定点数的加减运算

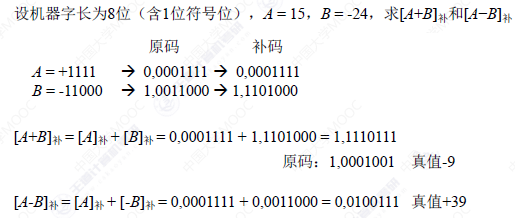

补码的加减运算

[X+Y]补=[X]补+[Y]补;[X-Y]补=[X]补+[-Y]补

对于补码来说,无论加法还是减法,最后都变成加法,由加法器实现运算,符号位也参与运算。

若最终结果位数大于n+1位,则高位丢弃,只保留n+1位。

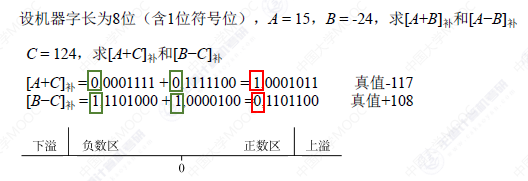

溢出判断

只有“正数+正数”才会上溢——正+正=负;只有“负数+负数”才会下溢——负+负=正。

补码定点数加减运算的溢出判断有三种方法:

- 方法一:采用一位符号位,A的符号位为 A s A_s As,B的符号位为 B s B_s Bs,运算结果的符号位为 S s S_s Ss。溢出逻辑表达式为 V = A s B s S s ‾ + A s B s ‾ S s V=A_sB_s \overline{S_s}+\overline{A_sB_s}S_s V=AsBsSs+AsBsSs,若V=0表示无溢出;若V=1表示有溢出。

即,参加操作的两个数符号相同,结果又与原操作数的符号不同,则表示结果溢出。

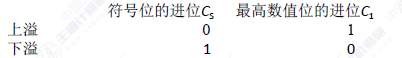

- 方法二:采用一位符号位,根据数据位进位情况判断溢出,符号位的进位 C s C_s Cs,最高数值为的进位 C 1 C_1 C1。溢出逻辑表达式为 V = C s ⊕ C 1 V=C_s \oplus C_1 V=Cs⊕C1,若V=0表示无溢出;若V=1表示有溢出。

即,最高位(符号位)的进位与次高位(最高数值位)的进位相同,说明无溢出,否则说明溢出。

- 方法三:采用双符号为,正数符号为00,负数符号为11,即两个符号位为 S s 1 , S s 2 S_{s1},S_{s2} Ss1,Ss2。溢出逻辑表达式为 V = S s 1 ⊕ S s 2 V=S_{s1} \oplus S_{s2} V=Ss1⊕Ss2,若V=0表示无溢出;若V=1表示有溢出。

即,运算结果的两个符号位相同,表示未溢出,否则表示溢出。

注:双符号位补码又称模4补码,实际存储时只存储1个符号位,运算时会复制一个符号位。单符号位补码又称模2补码(只有在ALU中采取双符号位)。

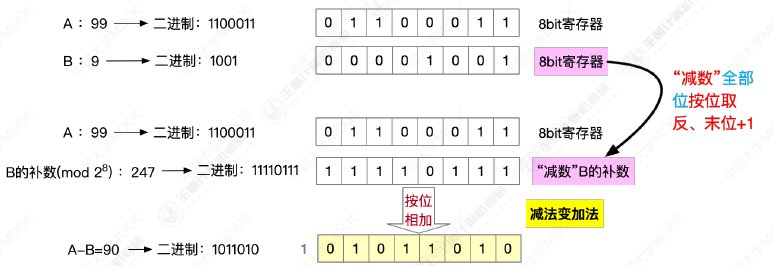

无符号数的加减运算

注:在计算机内部,无符号数的加减法等同于补码进行加减法,只是最后对于结果的解释不一样。

无符号数的加法运算

从最低位开始,按位相加,并往更高位进位。

无符号数的减法运算

- 被减数不变,减数全部按位取反,末位加1,减法变加法

- 从最低位开始,按位相加,并往更高位进位

溢出判断

手算判断溢出的方法:n bit无符号整数表示范围 0 ∼ 2 n − 1 0 \sim 2^n-1 0∼2n−1,超过此范围则溢出。

计算机判断溢出的方法:

- 无符号加法的溢出判断:最高位产生的进位=1时,发生溢出,否则未溢出。

- 无符号数减法的溢出判断:减法变加法,最高位产生进位=0时,发生溢出,否则未溢出。

##原码的加减运算

加法运算

-

正+正=绝对值做加法,结果为正

-

负+负=绝对值做加法,结果为负

-

正+负=绝对值大的减绝对值小的,符号同绝对值大的数

-

负+正=绝对值大的减绝对值小的,符号同绝对值大的数

正+正和负+负可能会发生溢出。

减法运算

减数符号取反,转变为加法运算。

补码加减运算电路

原码的乘法运算

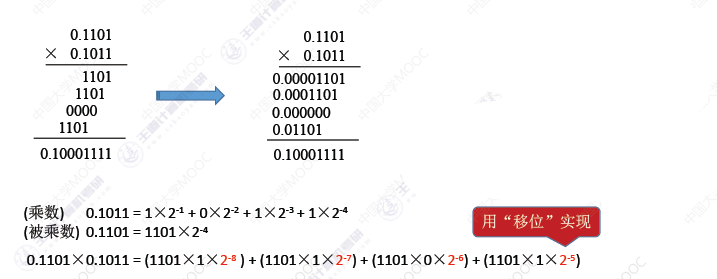

手算乘法(二进制)

原码一位乘法

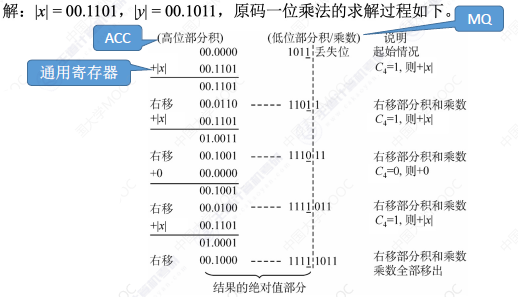

例:设机器字长为n+1=5位(含1位符号位),[x]原= 1.1101,[y]原= 0.1011,采用原码一位乘法求x*y

计算过程中,符号位单独处理,符号位= x s ⊕ y s x_s \oplus y_s xs⊕ys,数值位取绝对值进行乘法运算。

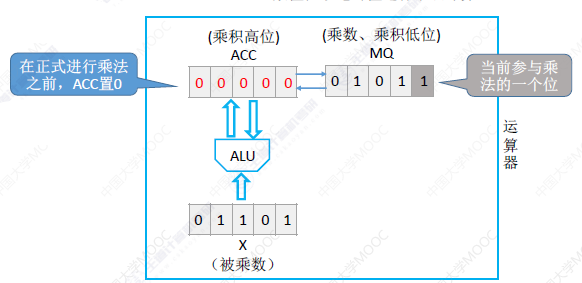

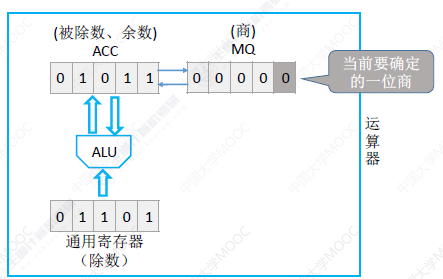

需要使用运算器的ACC(累加器,存放乘积高位)、MQ(乘商寄存器,存放乘数、乘积低位)、X(通用的操作数寄存器,存放被乘数)

实现方法:先加法再移位,重复n次。

- 加法:当前为=1,则ACC加上被乘数;当前位=0,则ACC加上0

- 移位:对ACC与MQ内的二进制数看作连续的一个二进制数,一起进行逻辑右移,高位补0,ACC低位移到MQ(留在ACC的部分+此部分可称为“部分积”),而MQ的移出的低位则直接丢弃。

重复n次后,得到如下结果:

最后,修改小数点前的符号位为1,计算完毕。

原码一位乘法手算模拟

设机器字长为5位(含1位符号位,n=4),x = −0.1101,y = +0.1011,采用原码一位乘法求x*y

解答过程如下:

注:

- 乘数的符号位不参与运算,可以省略

- 原码一位乘可以只用单符号位

- 答题时最终结果最好写为原码机器数

最后计算符号位,得x*y=-0.10001111

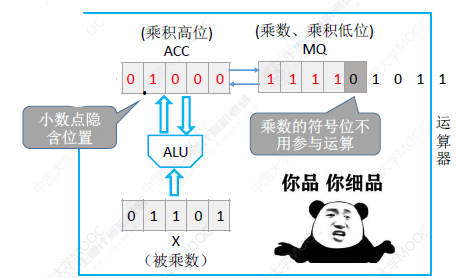

补码的乘法运算

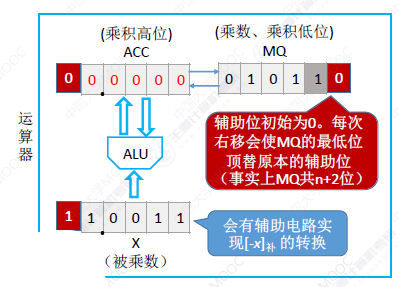

补码一位乘法

补码一位乘法也叫做Booth算法。一般来说,Booth算法的被乘数、部分积采用双符号位补码。

对比原码一位乘法

| 原码一位乘法 | 补码一位乘法 |

|---|---|

| 进行n轮加法、移位 | 进行n轮加法、移位,最后再来一次加法,加[X]补 |

| 每次加法可能+0、+[|X|]原(根据MQ的最低位) | 每次加法可能+0、+[X]补、+[-X]补(根据MQ的最低位、辅助位) |

| 每次移位是逻辑右移 | 每次移位是补码的算数右移 |

| 符号位不参与运算 | 符号位参与运算 |

| MQ最低位=1,(ACC)+[|X|]原; MQ最低为=0,(ACC)+0 | 辅助位-MQ最低位=1,(ACC)+[X]补 辅助位-MQ最低位=0,(ACC)+0 辅助位-MQ最低位=-1,(ACC)+[-X]补 |

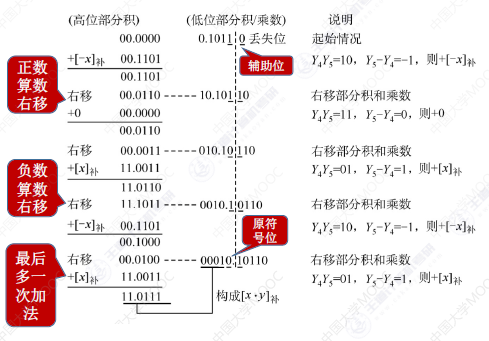

例:设机器字长为5位(含1位符号位,n=4),x = −0.1101,y = +0.1011,采用Booth算法求x·y。[x]补=1.0011,[−x]补=0.1101,[y]补=0.1011

补码一位乘法手算模拟

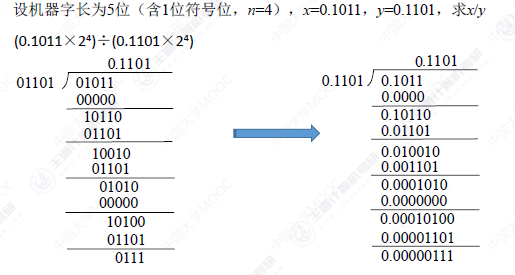

原码的除法运算

手算除法(二进制)

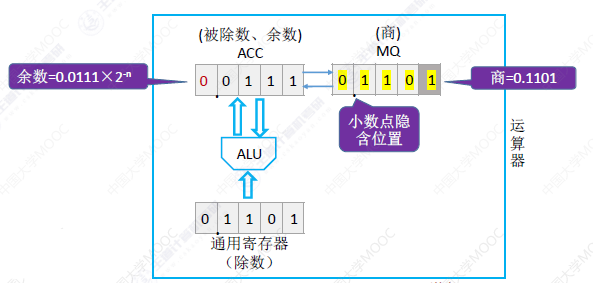

规律:忽略小数点,每确定一位商,进行一次减法,得到4位余数,在余数末尾补0,再确定下一位商。确定5位商即可停止(机器字长为5位),得x/y结果为0.1101,余数为0.00000111

原码除法:恢复余数法

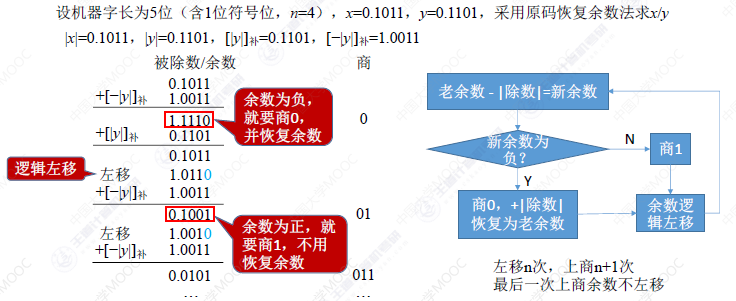

例:设机器字长为5位(含1位符号位,n=4),x=0.1011,y=0.1101,采用原码恢复余数法求x/y。|x|=0.1011,|y|=0.1101,[|y|]补=0.1101,[−|y|]补=1.0011

实现方法:上商0/1,得到余数,余数末尾补0

- 计算机默认先商1,如果ACC中求余数,即(ACC)+ [−|y|]补,如果得到一个负数结果,则将当前商1变成商0,恢复余数。

- 将ACC、MQ整体逻辑左移,ACC高位丢弃,MQ低位补0

经过n+1次上商,n次左移操作,最终状态如下:

原码除法:恢复余数法手算

符号位与数值位分开处理

若余数为负,恢复余数时,则可直接商0,并让余数左移1位再加上|除数|

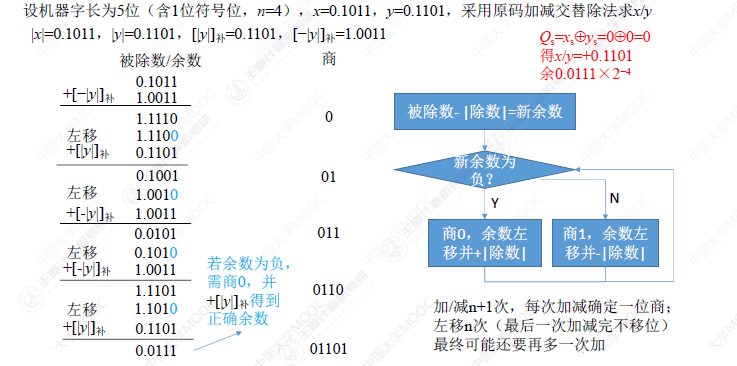

原码除法:加减交替法

符号位与数值位分开处理

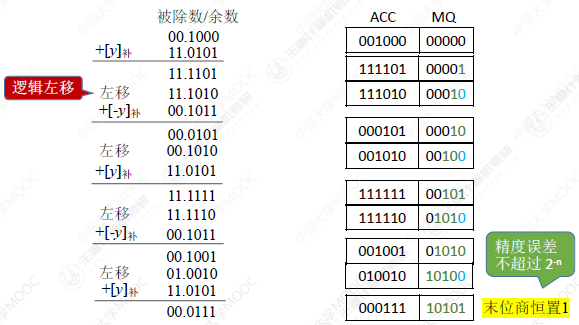

补码除法的运算

补码除法:加减交替法

设机器字长为5位(含1位符号位,n=4),x=+0.1000,y=-0.1011,采用补码加减交替除法求x/y。[x]补=00.1000,[y]补=11.0101,[−y]补=00.1011

注:

- 符号位参与运算

- 被除数/余数、除数采用双符号位

被除数和除数同号,则被除数减去除数;异号则被除数加上除数。

余数和除数同号,商1,余数左移一位减去除数;余数和除数异号,商0,余数左移一位加上除数,重复n次。

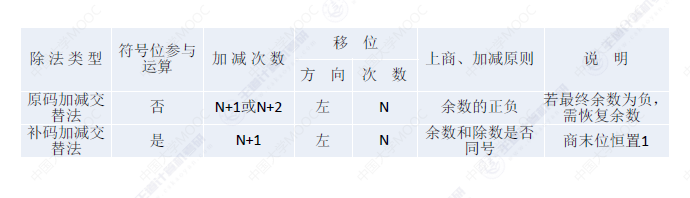

除法运算总结

浮点数的表示和运算

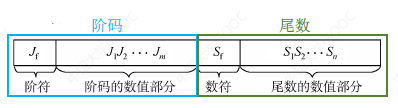

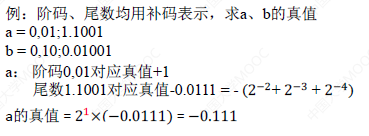

浮点数的表示

阶码E:常用补码或移码表示的定点整数,反映浮点数的表示范围及小数点的实际位置。

尾数M:常用原码或补码表示的定点小数,数值部分的位数n反映浮点数的精度。

浮点数的真值 N = r E ∗ M N=r^E*M N=rE∗M

r r r是浮点数的进制,决定了阶码的权重,基数越大,范围越大,但在浮点数的总位数不变的情况下比低基数的精度低。

尾数给出一个小数,阶码指明了小数点要向前/向后移动几位。

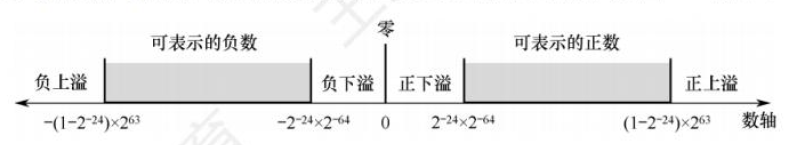

浮点数的溢出

运算结果大于最大正数时称为正上溢,小于绝对值最大负数时称为负上溢,正上溢和负上溢统称上溢。数据一旦产生上溢,计算机必须中断运算操作,进行溢出处理。

当运算结果在0至最小正数之间时称为正下溢,在0至绝对值最小负数之间时称为负下溢,正下溢和负下溢统称下溢。数据下溢时,浮点数值趋于零,计算机将其当作机器零处理。

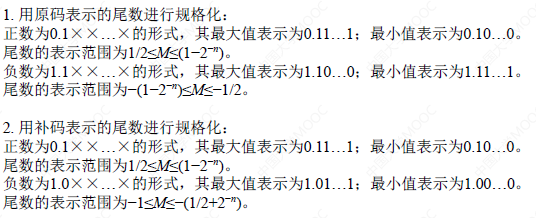

浮点数尾数的规格化

规格化浮点数:规定尾数的最高数值位必须时一个有效值(tips:做题时注意尾数是原码还是补码)。

规格化的目的:主要是为了增加数据的表示精度。

左规:当运算结果的尾数最高数位不是有效位,需要进行左规,尾数左移一位,阶码减1(左规可能要进行多次)。

右规:当运算结果的尾数有效位进到小数点前面时,需要进行右规,右规只需要进行一次,将尾数右移一位,阶码加1(可能会导致溢出)。

注:采用双符号位,发生溢出时,更高的符号位是正确的符号位。

特点:规格化的原码尾数,最高数值位一定是1;规格化的补码尾数,符号位与最高数值位一定相反。

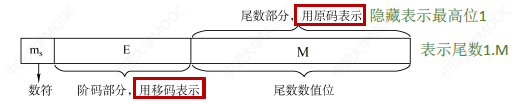

IEEE754标准

IEEE754标准规定用移码表示阶码,用原码表示尾数。

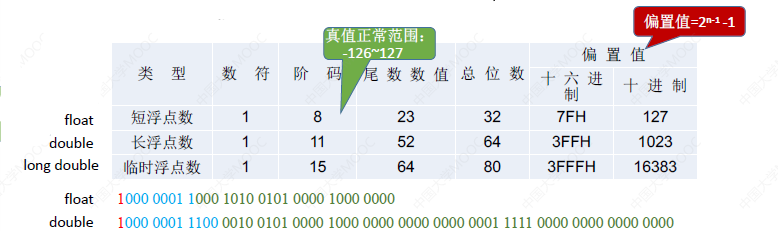

不同的数据类型有不同的位数,具体如下:

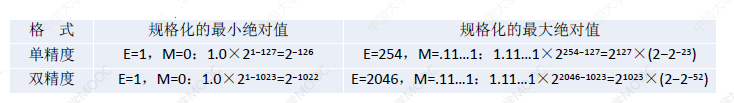

注:阶码全1、全0用做特殊用途。

阶码真值=移码-偏移量

-

规格化的短浮点数的真值为: ( − 1 ) s ∗ 1. M ∗ 2 E − 127 (-1)^s*1.M*2^{E-127} (−1)s∗1.M∗2E−127

-

规格化的长浮点数的真值为: ( − 1 ) s ∗ 1. M ∗ 2 E − 1023 (-1)^s*1.M*2^{E-1023} (−1)s∗1.M∗2E−1023

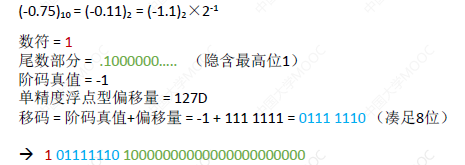

例:将十进制数-0.75转换为IEEE 754的单精度浮点数格式表示。

对于给定的小数,先转化成二进制数,确定符号位,对尾数进行规格化,确定阶码真值,规格化后的尾数即为浮点数格式的尾数(可能需要扩展),阶码真值加上偏移量即为浮点数格式的阶码(可能需要扩展),加上符号位,即可得出结果。

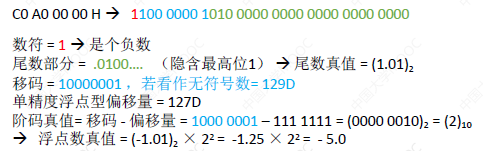

例:IEEE 754的单精度浮点数C0 A0 00 00 H的值时多少。

最小绝对值:尾数全为0,阶码真值最小-126,对应移码机器数0000 0001,此时整体的真值为

(

1.0

)

2

∗

2

−

126

(1.0)_2*2^{-126}

(1.0)2∗2−126

最大绝对值:尾数全为1,阶码真值最大127,对应移码机器数1111 1110,此时整体的真值为

(

1.111

…

11

)

2

×

2

127

(1.111…11)_2×2^{127}

(1.111…11)2×2127

注:

- 当阶码E全为0,尾数M不全为0时,表示非规格化小数 ± ( 0. x x . . . x ) 2 ∗ 2 − 126 \pm (0.xx...x)_2*2^{-126} ±(0.xx...x)2∗2−126,此时隐含最高位变为0,阶码真值固定视为-126。

- 当阶码E全为0,尾数M全为0时,表示真值±0

- 当阶码E全为1,尾数M全为0时,表示无穷大±∞

- 当阶码E全为1,尾数M不全为0时,表示非数值“NaN” (Not a Number),非法运算

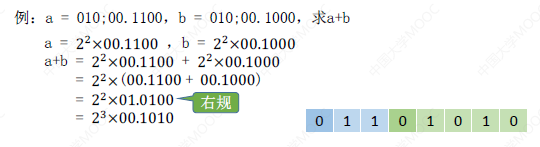

浮点数加减运算

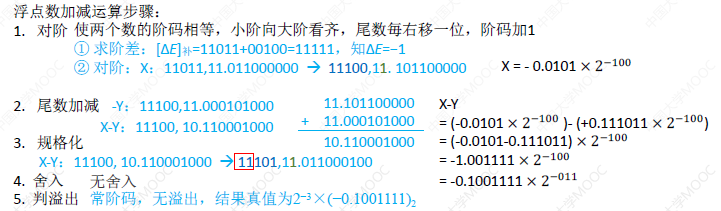

浮点数加减运算步骤:

- 对阶

- 尾数加减

- 规格化

- 舍入

- 判溢出

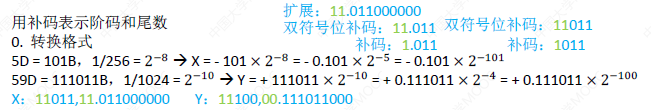

例:已知十进制数X=−5/256、Y=+59/1024,按机器补码浮点运算规则计算X−Y,结果用二进制表示,浮点数格式如下:阶符取2位,阶码取3位,数符取2位,尾数取9位。

具体步骤如下:

舍入问题

舍入是浮点数的概念,定点数没有舍入的概念。浮点数舍入的情况有两种,对阶和右规格化。舍入不一定产生误差。

- 就近舍入法:类似于十进制数运算中的“四舍五入”法,即在尾数右移时,被移去的最高数值位为0,则舍去;被移去的最高数值位为1,则在尾数的末位加1。这样做可能会使尾数又溢出,此时需再做一次右规。

- 恒置“1”法:尾数右移时,不论丢掉的最高数值位是“1”还是“0”,都使右移后的尾数末位恒置“1”。这种方法同样有使尾数变大和变小的两种可能。

- 正向舍入:朝数轴正无穷大方向舍入,如果是正数,不全为0时进1,全为0时截断;如果是负数,直接截断。

- 负向舍入:朝数轴负无穷大方向舍入,如果是正数,直接截断;如果是负数,不全为0时进1,全为0时截断。

- 截断法:截取所需位数,丢弃后面所有位。

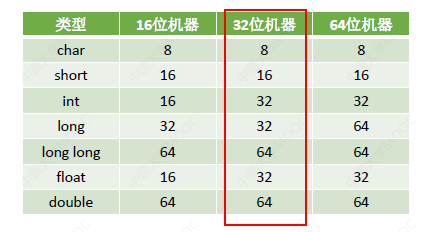

C语言中浮点数类型

c h a r → i n t → l o n g → d o u l e 和 f l o a t → d o u l e char \rightarrow int \rightarrow long \rightarrow doule 和 float \rightarrow doule char→int→long→doule和float→doule,范围、从小到大,转换过程没有损失。

$int \rightarrow float ,可能会损失精度, ,可能会损失精度, ,可能会损失精度,flaot \rightarrow int $,可能会溢出及损失精度

注:当高类型和低类型一起运算时,需将较低类型转化为高类型。

数据的存储和排列

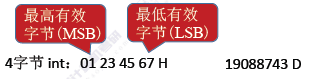

大小端模式

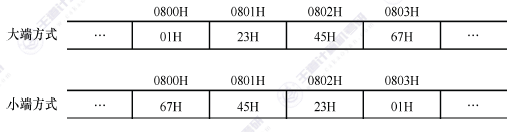

多个字节数据在内存里一定是占连续的几个字节。

大端方式是高字节存放到内存的低地址,便于人类阅读;小端方式是低字节存放到内存的低地址,便于机器处理。

边界对齐

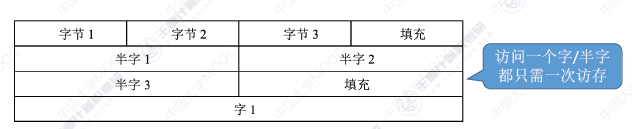

现代计算机通常是按字节编址,即每个字节对应1个地址。

通常也支持按字、按半字、按字节寻址。

假设存储字长为32位,则1个字=32bit,半字=16bit。每次访存只能读/写1个字。

不同的寻址方式:

- 按Word:那必然就是0、4、8…

- 按1/2Word:那必然是0,2, 4, 6, 8…

- 按1Byte:那必然是0、1、2、3、4、5…

- 按双字:那就是0、8、6…

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?