cache基本原理cache的功能如图3.28所示,cache是介于CPU和主存M2之间的小容量存储器,但存取速度比主存快,容量远小于主存。cache能高速地向CPU提供指令和数据,从而加快了程序的执行速度。从功能上看,它是主存的缓冲存储器,由高速的SRAM组成。为追求高速,包括管理在内的全部功能由硬件实现,因而对程序员是透明cache中。CPU与cache之间的数据交换是以字为单位,而cache与主存之间的数据交换是以块为单位。一个块由若干字组成,是定长的。当CPU读取内存中一个字时,便发出此字的内存地址到cache和主存。此时cache控制逻辑依据地址判断此字当前是否在cache中若是,则cache命中,此字立即传送给CPU;若非,则cache缺失(未命中),用主存读周期把此字从主存读出送到CPU,与此同时,把含有这个字的整个数据块从主存读出送到的。cache是一种高速缓冲存储器,是为了解决CPU和主存之间速度不匹配而采用的一项重要技术。其原理基于程序运行中具有的空间局部性和时间局部性特征

cache基本原理

cache除包含SRAM外,还要有控制逻辑。若cache在CPU芯片外,它的控制逻辑一般与主存控制逻辑合成在一起,称为主存/chace控制器若cache在CPU内,则由CPU提供它的控制逻辑。

太大。能的。命中率h与程序的行为、cache的容量、组织方式、块的大小有关。由式(3.6)看出,为提高访问效率,命中率h越接近1越好。值以5~10为宜,不宜我们追求的目标是,以较小的硬件代价使cache/主存系统的平均访问时间t。越接近t。越好。设/=tm/1.表示主存与cache的访问时间之比,e表示访问效率,则有若表示命中时的cache访问时间,tm表示未命中时的主存访问时间,1-h表示未命中率(缺失率),则cache/主存系统的平均访问时间ta为在一个程序执行期间,设N。表示cache完成存取的总次数,Nm表示主存完成存取的总次数,h定义为命中率,则有从CPU来看,增加cache的目的,就是在性能上使主存的平均读出时间尽可能接近cache的读出时间。为了达到这个目的,在所有的存储器访问中由cache满足CPU需要的部分应占很高的比例,即cache的命中率应接近于1。由于程序访问的局部性,实现这个目标是可3 cache的命中率e=C L hte+(1-h)r h+(1-h)r r+(1-r)h U ta=hte+(1-h)tm h=N N+Nm(3 4)(3.5)(3.6)

在设计cache结构时,必须解决几个问题①主存的内容调入cache时如何存放?②访存时如何找到cache中的信息?③当cache空间不足时如何替换cache中已有的内容?④需要写操作时如何改写cache的内容?其中,前两个问题是相互关联的,即如何将主存信息定位在cache中,如何将主存地址变换为cache地址。与主存容量相比,cache的容量很小,它保存的内容只是主存内容的一个子集,且cache与主存的数据交换是以块为单位。为了把主存块放到cache中,必须应用某种方法把主存地址定位到cache中,称为地址映射。“映射”一词的物理含义是确定位置的对应关系,并用硬件来实现。这样当CPU访问存储器时,它所给出的一个字的内存地址会自动变换成cache的地址,即cache地址变换。从cache的基本工作原理可以看出,cache的设计需要遵循两个原则一是希望cache的命中率尽可能高,实际应接近于1二是希望cache对CPU而言是透明的,即不论是否有cache,CPU访存的方法都是一样的,软件不需增加任何指令就可以访问cache。解决了命中率和透明性问题,就CPU访存的角度而言,内存将具有主存的容量和接近cache的速度为此,必须增加一定的硬件电路完成控制功能,即cache控制器。4 cache结构设计必须解决的问题。

3.6.2主存与cache的地址映射

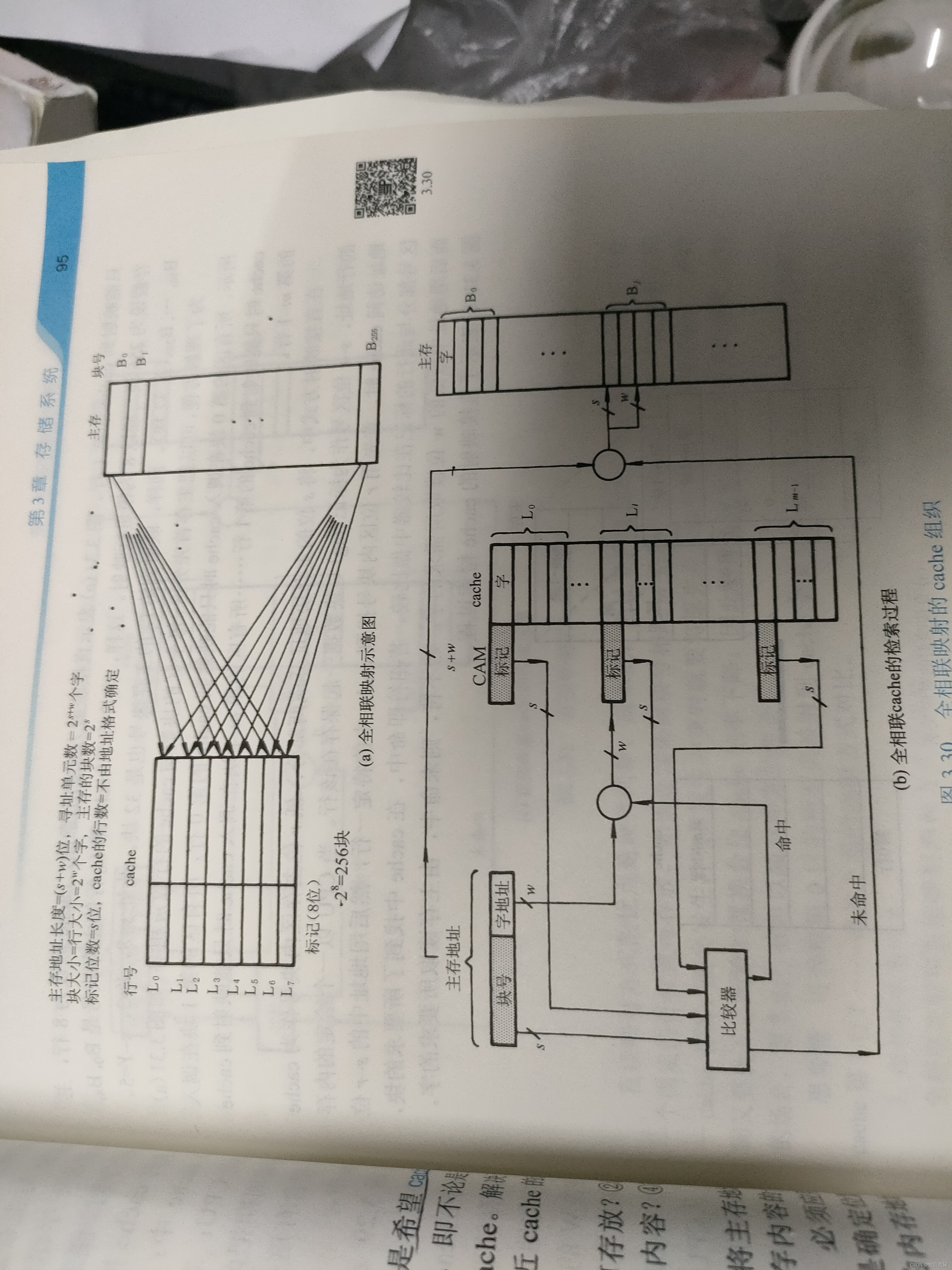

在全相联映射中,将主存中一个块的地址(块号)与块的内容(字)一起存于cache的行中,其中块地址存于cache行的标记(tag)部分中。这种带全部块地址一起保存的方法,可使主存的一个块直接复制到cache中的任意一行上,非常灵活。图3.30(a)是全相联映射的多对一示意图,其中cache为8行,主存为256块,每块(行)中有同样多的字cache的数据块大小称为行,用L表示,其中i0,1,2,,m-1,共有m=2行。主存的数据块大小称为块,用B,表示,其中」=0,1,2,-1,共有=2块。行与块是等长的,每个块(行)由2“个连续的字组成,字是CPU每次访问存储器时可存取的最小单位。地址映射方式有全相联方式、直接方式和组相联方式三种,下面分别介绍。cache采用。图3.30(b)表示全相联映射方式的检索过程。CPU访存指令指定了一个主存地址,为了快速检索,指令中的块号与cache中所有行的标记同时在比较器中进行比较。如果块号命中,则按字地址从cache中读取一个字如果块号未命中,则按主存地址从主存中读取这个字。在全相联cache中,全部标记用一个相联存储器来实现,全部数据存储用一个普通RAM来实现。全相联方式的主要缺点是高速比较器电路难于设计和实现,因此只适合于小容量

2249

2249

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?