Verilog-FPGA模型机课设:报告+视频,男生重新配音也可以直接使用~

压缩包包含:基本20条整数指令+扩展12条整数指令+中断异常相关6条指令

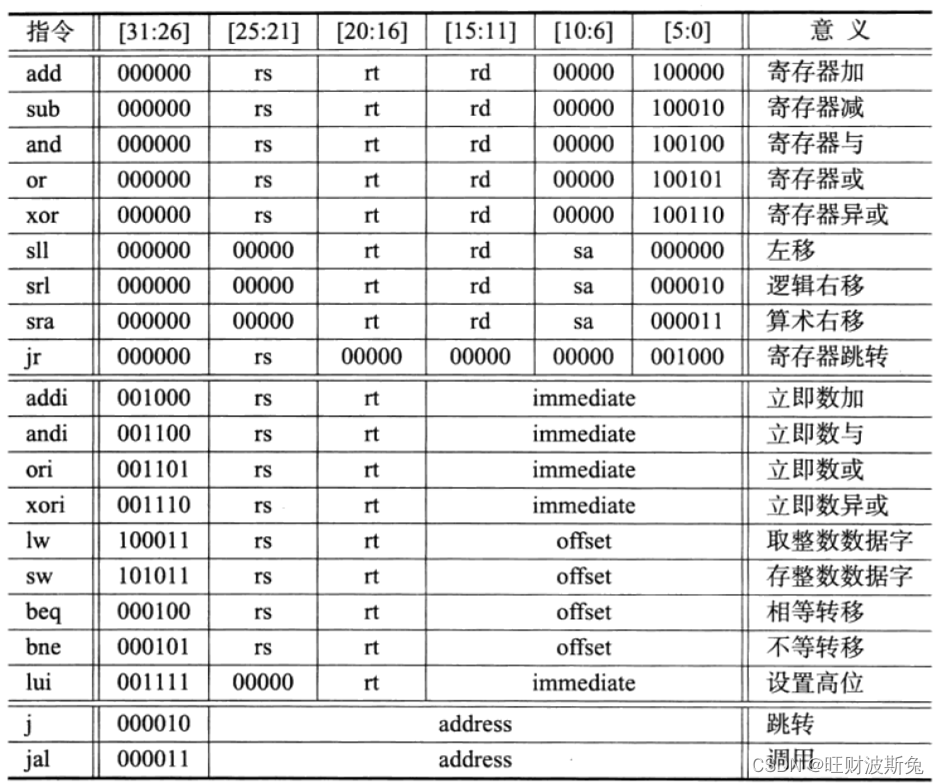

基本20条整数指令:

R型指令:用于寄存器之间的操作,如加减乘除。

I型指令:rs寄存器中存储的值和立即数的值之间的操作存放在rt寄存器中。

J型指令:进行无条件跳转的指令。

存储器指令:MIPS指令集中用于读取和写入存储器中的数据的指令。

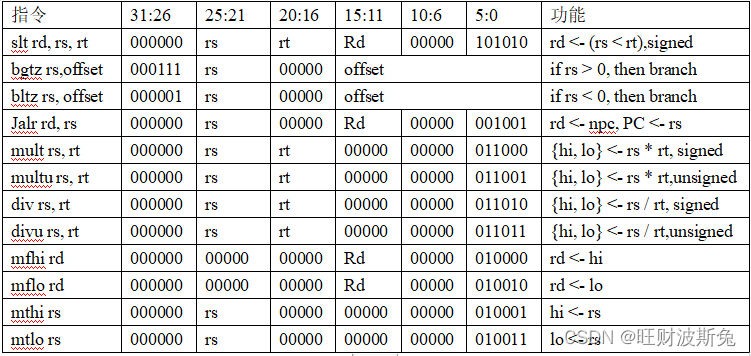

扩展12条整数指令:

slt指令:比较两个操作数寄存器t0和t1。

bgtz:判断r[1] > 0时跳转。

bltz:判断r[1] < 0时跳转。

jalr:跳转到一个地址并将下一条指令的地址存储到寄存器中。

mult:实现两个32位有符号数乘法运算,低32位有符号扩展到64位后存入寄存器LO,高32位有符号扩展到64位后存入寄存器HI。

multu:实现两个32位有符号数乘法运算,a0和a1按32位无符号数运算。

div:有符号数除法。

Divu:无符号除法。

mfhi:HI寄存器值拷贝到t0。

mflo:LO寄存器值拷贝到t0。

mthi:t0拷贝到HI寄存器。

mtlo:t0拷贝到LO寄存器。

中断异常相关6条指令:

| 指令 | 31:26 | 25:21 | 20:16 | 15:11 | 10:6 | 5:0 | 功能 |

| ll rt,offset(rs) | 110000 | rs | rt | offset | load; LLbit=1 | ||

| sc rt,offset(rs) | 111000 | rs | rt | offset | if(LLbit) store ;rt=1 else rt= 0 | ||

| mfc0 rt, rd | 010000 | 00000 | rt | rd | 00000 | 000000 | rt <- cp0[rd] |

| mtc0 rt, rd | 010000 | 00100 | rt | rd | 00000 | 000000 | cp0[rd] <- rt |

| eret | 010000 | 10000 | 00000 | 00000 | 00000 | 011000 | PC <- epc, LLbit <-0 |

| syscall | 00000 | 0 | 001100 | SysInt, LLbit <- 0 | |||

ll指令:从内存中读取一个字实现RMW操作。

sc指令:向内存中写入一个字完成RMW操作。

mfc0指令:将协处理器寄存器中的数据加载到通用寄存器中。

mtc0指令:将通用寄存器中的数据存储到协处理器寄存器中。

eret:在中断、异常或错误处理完成时返回中断指令。

syscall:发生断点异常,立即无条件地将控制权转到异常处理程序。

本文详细介绍了VerilogFPGA模型机中的整数指令集,包括基本20条(如加减乘除)和扩展12条(如比较、乘法、除法等)指令,以及与中断异常相关的6条指令,如读写内存、协处理器数据交换和异常处理流程。

本文详细介绍了VerilogFPGA模型机中的整数指令集,包括基本20条(如加减乘除)和扩展12条(如比较、乘法、除法等)指令,以及与中断异常相关的6条指令,如读写内存、协处理器数据交换和异常处理流程。

936

936

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?