备战软考这个系列的理论部分就结束了,当然了,有很多内容我没有介绍到,第一点是因为软考考的比较杂但是普遍不深,这就导致了知识点比较零散穿不起来。

第二是因为涉及到硬件、编程什么的,所以需要有计算机方面的基础,直接写出结论的话一些小白朋友可能会一头雾水,就像参考答案中的“显然”之类的。

第三是因为我本身水平有限,自己理解就很费劲了更别说是写出来试图教会大家了。

最后就是有些内容的权重没那么高,可能知识点不少,但是到了考场上就考一两题,因此我们直接刷题,在刷题的过程中去理解记忆。

不过说是说刷题,但是最终呈现给大家的还是经过我的筛选的,我会尽量选出一些比较有代表性的题目。

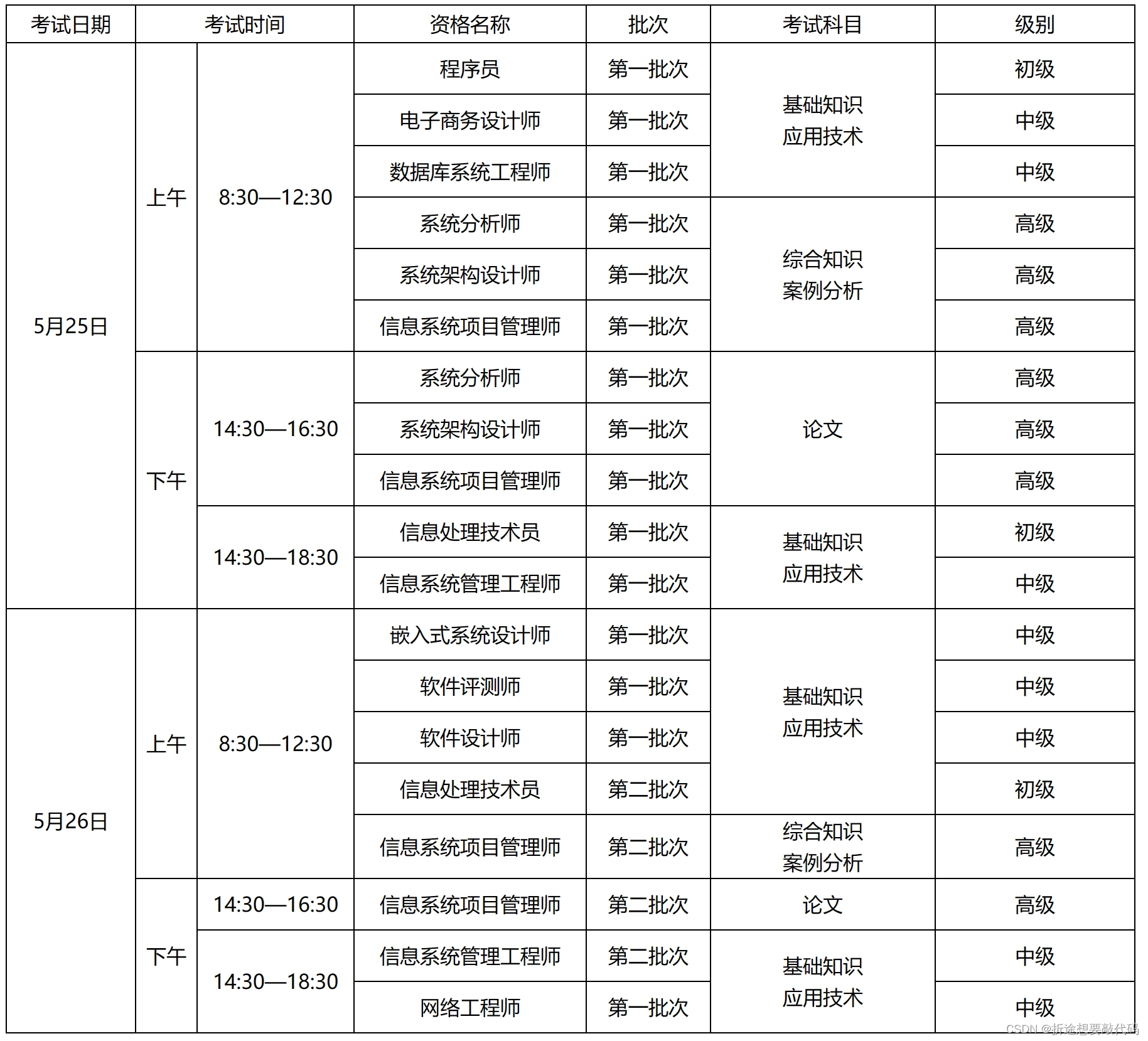

另外考试安排出来了(实际上五一刚过就出来了,但我才看到),大家提前安排好时间,祝大家(也祝我)考试顺利。

中国计算机技术职业资格网 (ruankao.org.cn)![]() https://www.ruankao.org.cn/article/content/2405061801407126412471514

https://www.ruankao.org.cn/article/content/2405061801407126412471514

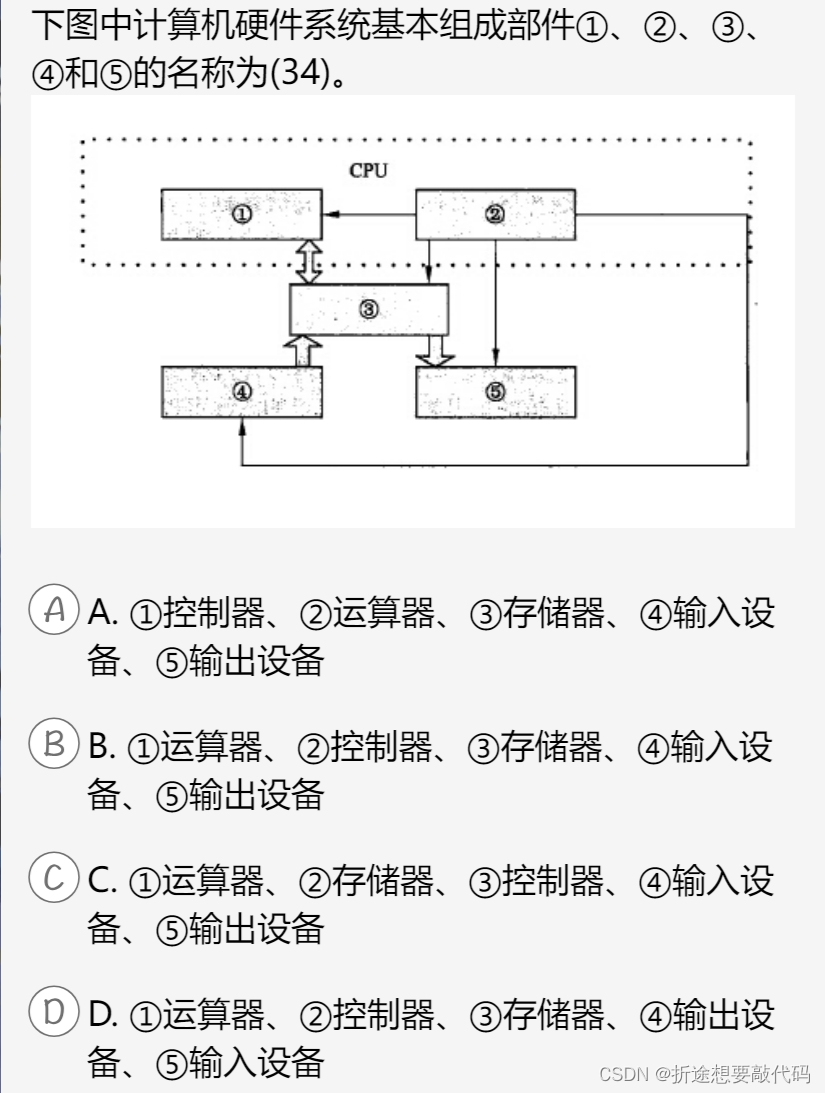

我们先看第一题。

这题考察的是基础的计算机硬件组成,这题可以参考之前的文章。

首先我们看题目中的1和2,被虚线框框起来了,标注的是CPU,那么我们知道CPU中的重要组成就是运算器和控制器。并且2单方面指向1,也对应上了控制器控制运算器,因此1是运算器,而2是控制器。

再看上图,只有存储器的落单的,对应到题目里是3号,因此3号是存储器。并且存储器和运算器是双向箭头,也进一步确定了3号就是存储器。

剩下4和5,4的箭头都是指出去的,而5的箭头都是指进来的,所以4号是输入设备,4号将外界的输入传输给计算器内部。5号是输出设备,计算机内部的信息传给5号再输出出外界(输出到外界的箭头没标)

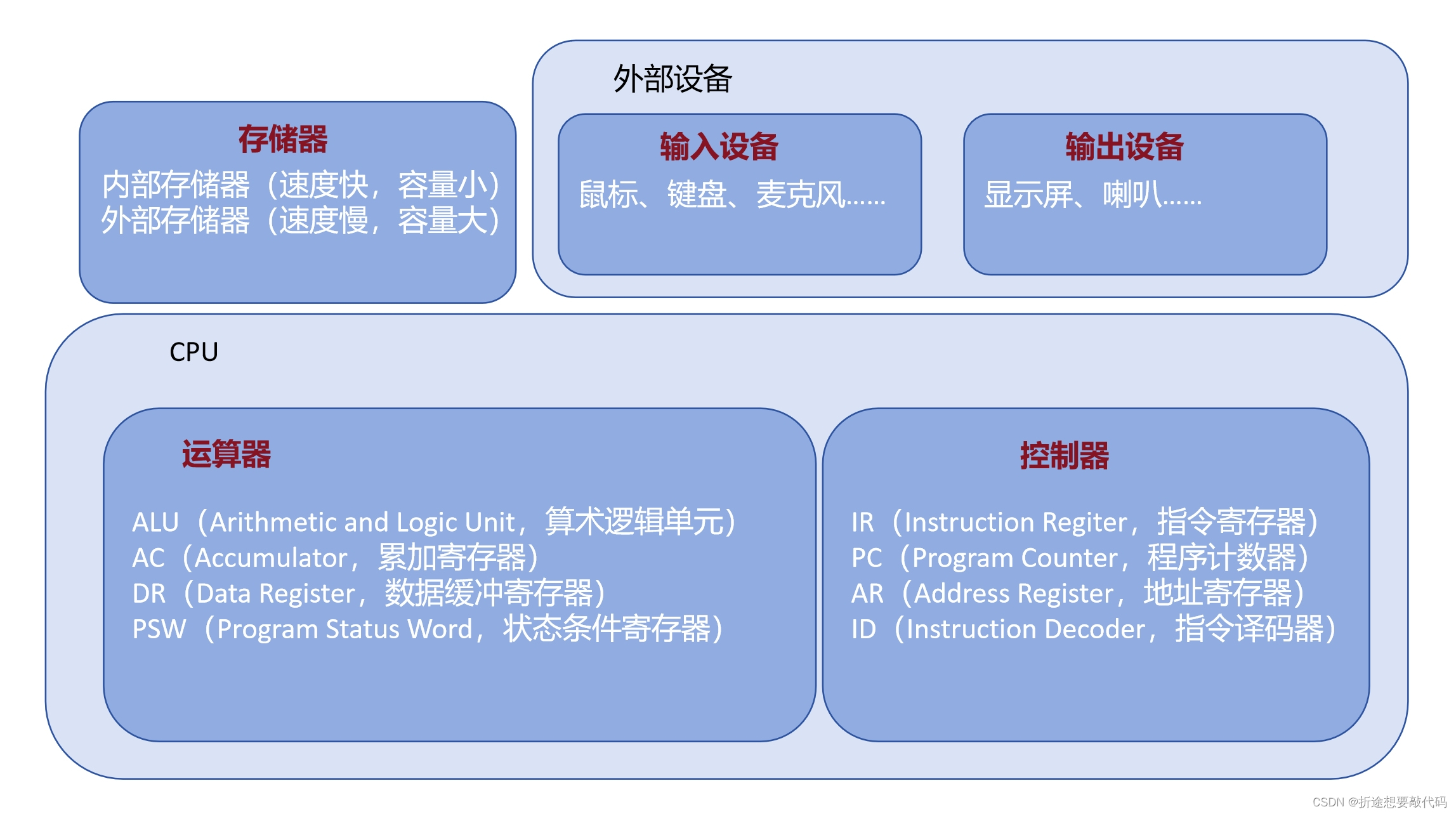

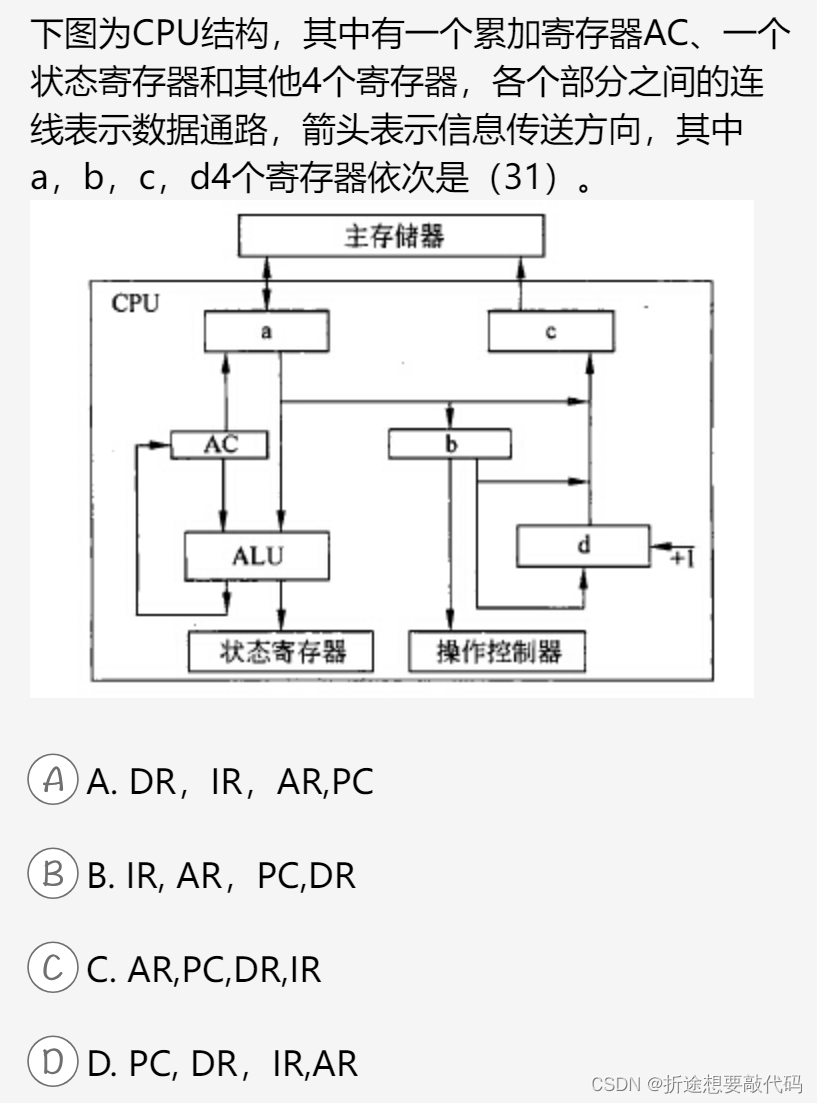

本题考察CPU的具体组成。

我们还是结合着上面的图(我自己用PPT画的蓝色的那个框图)再回顾一下CPU的组成。

CPU的功能是程序控制、操作控制、时间控制、数据处理等。

CPU中运算器又是由ALU(Arithmetic and Logic Unit,算术逻辑单元),AC(Accumulator,累加寄存器),DR(Data Register,数据缓冲寄存器),PSW(Program Status Word,状态条件寄存器)等组成的。

ALU实现对数据的算术和逻辑运算。

AC是运算结果或者源操作数的存放区。

DR暂存内存的指令或数据。

PSW保存指令运行结果的条件码。

控制器由IR(Instruction Regiter,指令寄存器),PC(Program Counter,程序计数器),AR(Address Register,地址寄存器),ID(Instruction Decoder,指令译码器)等组成。

IR存放的是CPU当前正在执行的指令。

PC存放的是下一条指令执行的地址,执行完指令后自动+1。

AR存放CPU当前正在访问的内存地址。

ID人如其名,就是分析指令操作码的。

再回到题目里,咋一看挺乱的,但我们可以逐个击破,比如说d,被一个箭头指着+1,而我们知道PC(程序计数器)它的特性就是指向下一条指令的地址,会自动+1,因此我们可以直接断定d就是PC,而答案里就一个d是PC的,我们直接选A。

考试的时候可以这样,但是我们刷题可不能这样,我们得把别的也搞懂。

我们顺着d看,d指向c,而我们知道d是PC,PC存放的是下一条要执行的指令的地址,CPU执行完一个命令就需要从PC中拿出当前需要执行的指令,然后PC再自动+1,因此c存放的是当前要执行的指令的地址,对应到寄存器中就是AR(地址寄存器),所以我们又得知了c就是AR。

再看b,b指向了操作控制器,指向了PC,还指向了PC指向AR的过程中。那就是跟控制相关的,而可以指向这么多地方的就是指令了,所以b是IR(指令寄存器),存放的是当前正在执行的指令。

最后剩个a,首先a和主存双箭头,指向ALU(算术逻辑单元),被AC(累加寄存器)指着,因此可以做出判断,a和数据相关,再加上a也指向了IR,因此a和指令相关。

综合判断,a就是DR(数据缓冲寄存器)。

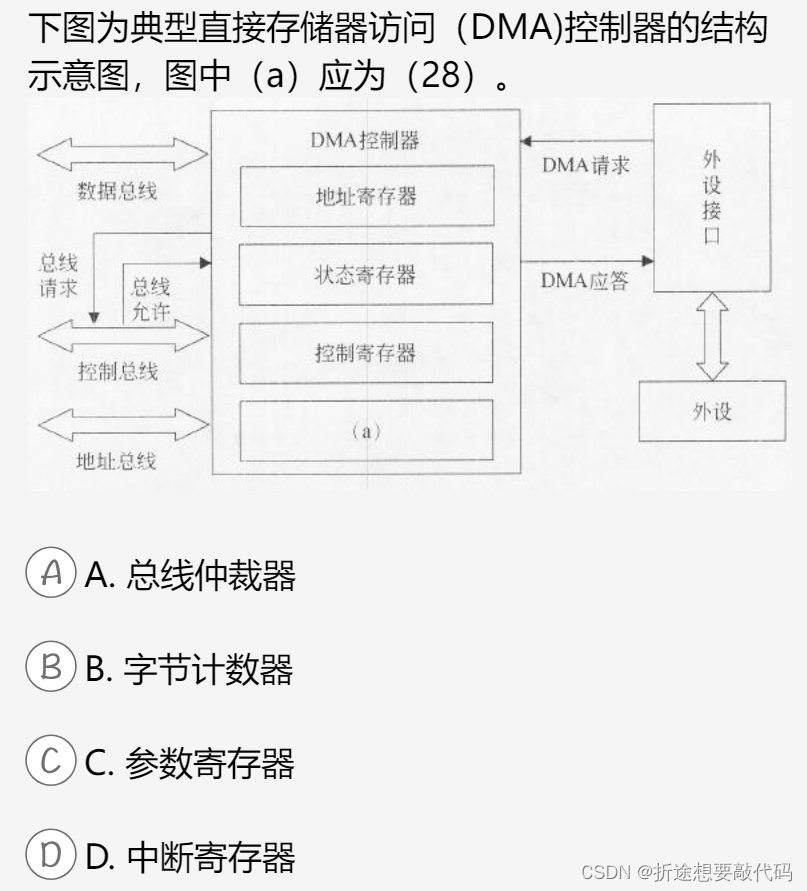

我们之前学习DMA的时候是没怎么关注DMA的控制器结构的,但是没关系,我们趁着做题的时候把这个空补起来。

我们虽然不清楚硬件结构,但是我们清楚DMA的运作流程,可以通过我们已有的知识去筛选出正确答案。

首先A和D是可以先排除的,总线仲裁器是在总线边上的,中断寄存器不会在DMA的控制器里。

剩下B和C。我们先想想使用DMA是什么流程,CPU只需要告诉DMA要搬运数据的起始地址和目标地址即可,然后DMA就会以数据块为单位去搬运数据,以数据块为单位是因为我们可以指定DMA具体搬运多少东西,因此DMA需要有个东西去记录搬运了多少,这个东西就是字节计数器。

再详细介绍一下DMA,DMA控制器可以像CPU那样获得总线的控制权,完成外设与存储器之间的数据高速交换。DMA控制器不但要与外设连接,以接受外设发出的DMA操作请求和在DMA期间对外设进行控制,还要与CPU连接,以请求总线的控制权;同时,它还需要与三大总线连接,以便进行总线的控制。DMA控制器里面包含地址寄存器、状态寄存器、控制寄存器、字节计数器。地址寄存器包括源地址和目的地址寄存器;状态寄存器用于寄存DMA传送前后的状态:控制寄存器用于选择DMA控制器的操作类型、工作方式、传送方向和有关参数;字节计数器用于控制传送数据块的长度。

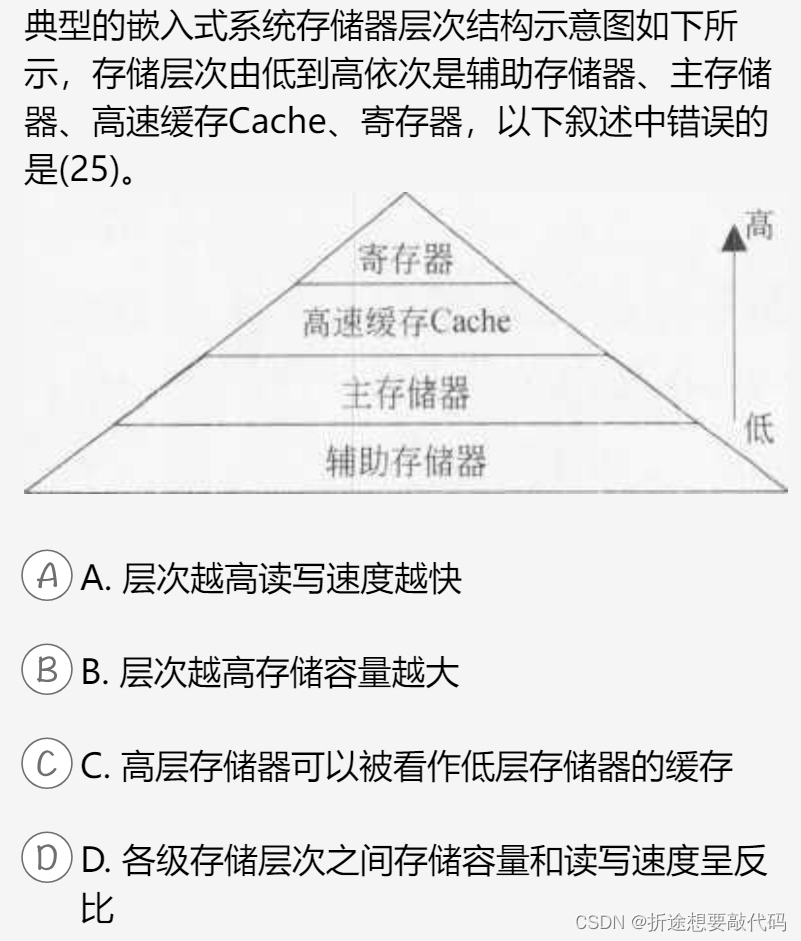

这题不难,错误的选项就是B。我们要记着的就是各类存储器的速度是寄存器>cache>主存>辅存。剩下还有一些存储器在图中没有体现出来,比如网盘之类的。

这题选C,就是一知识点,没有为什么,我第一次做选的D所以觉得有必要拿出来再聊聊。

因为冯诺依曼结构中的指令和数据是放在一起的,因此需要区分拿到的是指令还是数据,冯诺依曼机种是根据指令周期的不同阶段来区分从存储器取出的是指令还是数据的。在取指令期间取出的就是指令,在执行周期取出的就是数据。

190

190

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?