一,模仿 STM32 寄存器定义

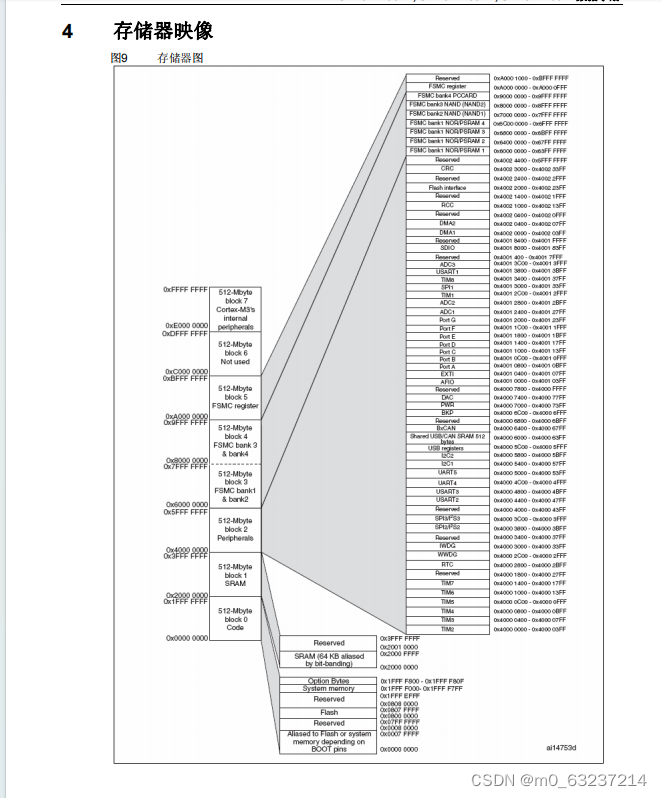

在STM32中,程序存储器、数据存储器、寄存器和输入输出端口被组织在同一个4GB的线性地址空间内。 数据字节以小端格式存放在存储器中。一个字里的最低地址字节被认为是该字的最低有效字 节,而最高地址字节是最高有效字节。

可访问的存储器空间被分成8个主要块,每个块为

512MB。

其他所有没有分配给片上存储器和外设的存储器空间都是保留的地址空间,请参考相应器件的数据手册中的存储器映像图。

以其中的GPIOE这部分为例

#define GPIOE_BASE (APB2PERIPH_BASE + 0x1800)

#define APB2PERIPH_BASE (PERIPH_BASE + 0x10000)

#define PERIPH_BASE ((uint32_t)0x40000000)

定义了GPIOE_BASE的基本地址 就是 GPIOE 的基地址为 0x40011800。

#define GPIOE ((GPIO_TypeDef *) GPIOE_BASE)

可以看出“

GPIOE

”是个宏定义,是一个指向地址

GPIOE_BASE

的结构体指针,结构体为

GPIO_TypeDef

,

GPIO_TypeDef

和

GPIOE_BASE

的定义如下:

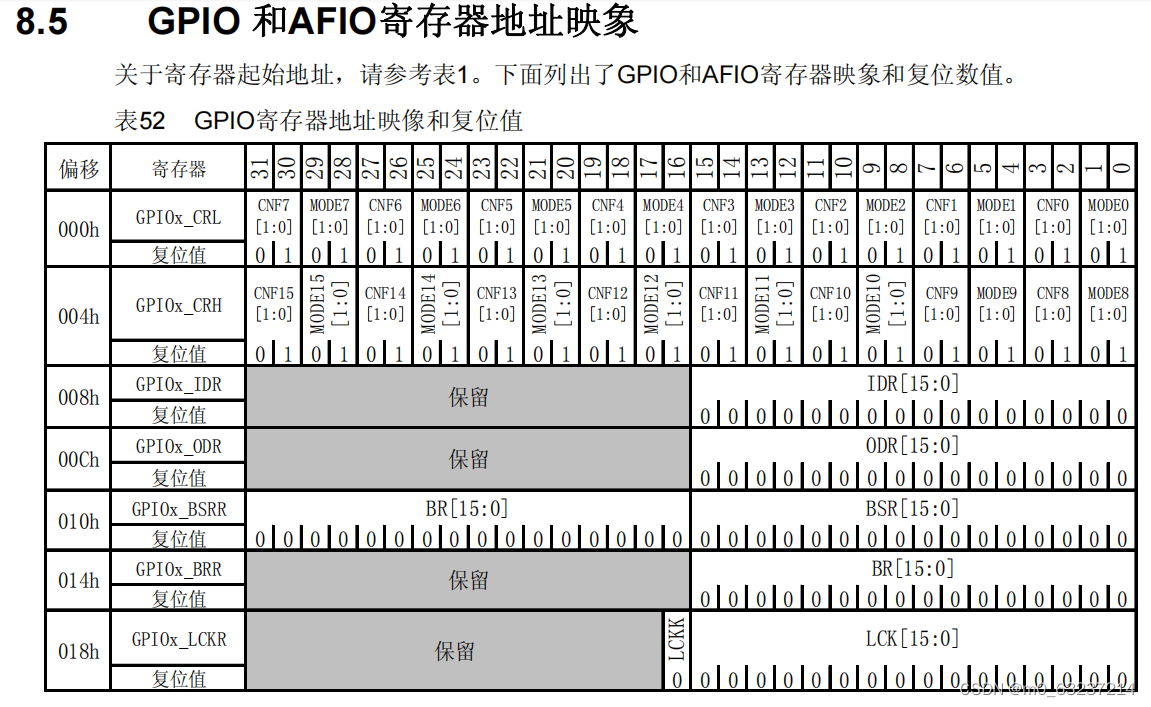

typedef struct

{

__IO uint32_t CRL;

__IO uint32_t CRH;

__IO uint32_t IDR;

__IO uint32_t ODR;

__IO uint32_t BSRR;

__IO uint32_t BRR;

__IO uint32_t LCKR;

} GPIO_TypeDef;

GPIO_TypeDef

是个结构体,结构体里面的成员变量有

CRL

、

CRH

、IDR、

ODR

、 BSRR、

BRR

和

LCKR

,这些都是

GPIO

的寄存器,每个成员变量都是

32

位

(4

字节

)

,这些寄存 器在结构体中的位置都是按照其地址值从小到大排序的。

二,

I.MX6U

寄存器定义

1

、编写外设结构体

示例代码 11.1.2.1 寄存器 IOMUX_SW_MUX_Type

/*

* IOMUX 寄存器组

*/

1 typedef struct

2 {

3 volatile unsigned int BOOT_MODE0;

4 volatile unsigned int BOOT_MODE1;

5 volatile unsigned int SNVS_TAMPER0;

6 volatile unsigned int SNVS_TAMPER1;

………

107 volatile unsigned int CSI_DATA00;

108 volatile unsigned int CSI_DATA01;

109 volatile unsigned int CSI_DATA02;

110 volatile unsigned int CSI_DATA03;

111 volatile unsigned int CSI_DATA04;

112 volatile unsigned int CSI_DATA05;

113 volatile unsigned int CSI_DATA06;

114 volatile unsigned int CSI_DATA07;

/* 为了缩短代码,其余 IO 复用寄存器省略 */

115}IOMUX_SW_MUX_Tpye;

2

、定义

IO

复用寄存器组的基地址

#define IOMUX_SW_MUX_BASE (0X020E0014)

3

、定义访问指针

#define IOMUX_SW_MUX ((IOMUX_SW_MUX_Type *)IOMUX_SW_MUX_BASE)

三,

实验程序编写

需要编写三个文件:

start.S、main.c 和 imx6ul.h。

start.S:

/*************************************

Copyright © zuozhongkai Co., Ltd. 1998-2019. All rights reserved.

文件名 : start.s

作者 : 左忠凯

版本 : V1.0

描述 : ZERO-I.MX6UL/I.MX6ULL开发板启动文件,完成C环境初始化,

C环境初始化完成以后跳转到C代码。

其他 : 无

日志 : 初版 2019/1/3 左忠凯修改

*************************************/

.global _start /* 全局标号 */

.global __bss_start

_bss_start:

.word __bss_start

.global __bss_end

_bss_end:

.word __bss_end

/*

* 描述: _start函数,程序从此函数开始执行,此函数主要功能是设置C

* 运行环境。

*/

_start:

/* 进入SVC模式 */

mrs r0, cpsr

bic r0, r0, #0x1f /* 将r0寄存器中的低5位清零,也就是cpsr的M0~M4 */

orr r0, r0, #0x13 /* r0或上0x13,表示使用SVC模式 */

msr cpsr, r0 /* 将r0 的数据写入到cpsr_c中 */

/* 清BSS段 */

ldr r0, _bss_start

ldr r1, _bss_end

mov r2, #0

bss_loop:

stmia r0!, {r2} /* 向r0的地址写入0,然后r0寄存器保存的地址值加1 */

cmp r0, r1 /* 比较r0和r1,也就是__bss_start和__bss_end的值*/

ble bss_loop /* 如果小于等于的话就跳转到bss_loop继续清bss段*/

/* 设置sp指针 */

ldr sp,=0X80200000 /* 设置栈指针 */

b main /* 跳转到main函数 */

imx6ul.h:

/***************************************************************

Copyright © zuozhongkai Co., Ltd. 1998-2019. All rights reserved.

文件名 : imx6ul.h

作者 : 左忠凯

版本 : V1.0

描述 : IMX6UL相关寄存器定义,参考STM32寄存器定义方法

其他 : 无

日志 : 初版V1.0 2019/1/3 左忠凯创建

**************************************************************/

/*

* 外设寄存器组的基地址

*/

#define CCM_BASE (0X020C4000)

#define CCM_ANALOG_BASE (0X020C8000)

#define IOMUX_SW_MUX_BASE (0X020E0014)

#define IOMUX_SW_PAD_BASE (0X020E0204)

#define GPIO1_BASE (0x0209C000)

#define GPIO2_BASE (0x020A0000)

#define GPIO3_BASE (0x020A4000)

#define GPIO4_BASE (0x020A8000)

#define GPIO5_BASE (0x020AC000)

/*

* CCM寄存器结构体定义,分为CCM和CCM_ANALOG

*/

typedef struct

{

volatile unsigned int CCR;

volatile unsigned int CCDR;

volatile unsigned int CSR;

volatile unsigned int CCSR;

volatile unsigned int CACRR;

volatile unsigned int CBCDR;

volatile unsigned int CBCMR;

volatile unsigned int CSCMR1;

volatile unsigned int CSCMR2;

volatile unsigned int CSCDR1;

volatile unsigned int CS1CDR;

volatile unsigned int CS2CDR;

volatile unsigned int CDCDR;

volatile unsigned int CHSCCDR;

volatile unsigned int CSCDR2;

volatile unsigned int CSCDR3;

volatile unsigned int RESERVED_1[2];

volatile unsigned int CDHIPR;

volatile unsigned int RESERVED_2[2];

volatile unsigned int CLPCR;

volatile unsigned int CISR;

volatile unsigned int CIMR;

volatile unsigned int CCOSR;

volatile unsigned int CGPR;

volatile unsigned int CCGR0;

volatile unsigned int CCGR1;

volatile unsigned int CCGR2;

volatile unsigned int CCGR3;

volatile unsigned int CCGR4;

volatile unsigned int CCGR5;

volatile unsigned int CCGR6;

volatile unsigned int RESERVED_3[1];

volatile unsigned int CMEOR;

} CCM_Type;

typedef struct

{

volatile unsigned int PLL_ARM;

volatile unsigned int PLL_ARM_SET;

volatile unsigned int PLL_ARM_CLR;

volatile unsigned int PLL_ARM_TOG;

volatile unsigned int PLL_USB1;

volatile unsigned int PLL_USB1_SET;

volatile unsigned int PLL_USB1_CLR;

volatile unsigned int PLL_USB1_TOG;

volatile unsigned int PLL_USB2;

volatile unsigned int PLL_USB2_SET;

volatile unsigned int PLL_USB2_CLR;

volatile unsigned int PLL_USB2_TOG;

volatile unsigned int PLL_SYS;

volatile unsigned int PLL_SYS_SET;

volatile unsigned int PLL_SYS_CLR;

volatile unsigned int PLL_SYS_TOG;

volatile unsigned int PLL_SYS_SS;

volatile unsigned int RESERVED_1[3];

volatile unsigned int PLL_SYS_NUM;

volatile unsigned int RESERVED_2[3];

volatile unsigned int PLL_SYS_DENOM;

volatile unsigned int RESERVED_3[3];

volatile unsigned int PLL_AUDIO;

volatile unsigned int PLL_AUDIO_SET;

volatile unsigned int PLL_AUDIO_CLR;

volatile unsigned int PLL_AUDIO_TOG;

volatile unsigned int PLL_AUDIO_DENOM;

volatile unsigned int RESERVED_4[3];

volatile unsigned int PLL_VIDEO;

volatile unsigned int PLL_VIDEO_SET;

volatile unsigned int PLL_VIDEO_CLR;

volatile unsigned int PLL_VIDEO_TOG;

volatile unsigned int PLL_VIDEO_NUM;

volatile unsigned int RESERVED_5[3];

volatile unsigned int PLL_VIDEO_DENOM;

volatile unsigned int RESERVED_6[7];

volatile unsigned int PLL_ENET;

volatile unsigned int PLL_ENET_SET;

volatile unsigned int PLL_ENET_CLR;

volatile unsigned int PLL_ENET_TOG;

volatile unsigned int PFD_480;

volatile unsigned int PFD_480_SET;

volatile unsigned int PFD_480_CLR;

volatile unsigned int PFD_480_TOG;

volatile unsigned int PFD_528;

volatile unsigned int PFD_528_SET;

volatile unsigned int PFD_528_CLR;

volatile unsigned int PFD_528_TOG;

volatile unsigned int RESERVED_7[16];

volatile unsigned int MISC0;

volatile unsigned int MISC0_SET;

volatile unsigned int MISC0_CLR;

volatile unsigned int MISC0_TOG;

volatile unsigned int MISC1;

volatile unsigned int MISC1_SET;

volatile unsigned int MISC1_CLR;

volatile unsigned int MISC1_TOG;

volatile unsigned int MISC2;

volatile unsigned int MISC2_SET;

volatile unsigned int MISC2_CLR;

volatile unsigned int MISC2_TOG;

} CCM_ANALOG_Type;

/*

* IOMUX寄存器组

*/

typedef struct

{

volatile unsigned int BOOT_MODE0;

volatile unsigned int BOOT_MODE1;

volatile unsigned int SNVS_TAMPER0;

volatile unsigned int SNVS_TAMPER1;

volatile unsigned int SNVS_TAMPER2;

volatile unsigned int SNVS_TAMPER3;

volatile unsigned int SNVS_TAMPER4;

volatile unsigned int SNVS_TAMPER5;

volatile unsigned int SNVS_TAMPER6;

volatile unsigned int SNVS_TAMPER7;

volatile unsigned int SNVS_TAMPER8;

volatile unsigned int SNVS_TAMPER9;

volatile unsigned int JTAG_MOD;

volatile unsigned int JTAG_TMS;

volatile unsigned int JTAG_TDO;

volatile unsigned int JTAG_TDI;

volatile unsigned int JTAG_TCK;

volatile unsigned int JTAG_TRST_B;

volatile unsigned int GPIO1_IO00;

volatile unsigned int GPIO1_IO01;

volatile unsigned int GPIO1_IO02;

volatile unsigned int GPIO1_IO03;

volatile unsigned int GPIO1_IO04;

volatile unsigned int GPIO1_IO05;

volatile unsigned int GPIO1_IO06;

volatile unsigned int GPIO1_IO07;

volatile unsigned int GPIO1_IO08;

volatile unsigned int GPIO1_IO09;

volatile unsigned int UART1_TX_DATA;

volatile unsigned int UART1_RX_DATA;

volatile unsigned int UART1_CTS_B;

volatile unsigned int UART1_RTS_B;

volatile unsigned int UART2_TX_DATA;

volatile unsigned int UART2_RX_DATA;

volatile unsigned int UART2_CTS_B;

volatile unsigned int UART2_RTS_B;

volatile unsigned int UART3_TX_DATA;

volatile unsigned int UART3_RX_DATA;

volatile unsigned int UART3_CTS_B;

volatile unsigned int UART3_RTS_B;

volatile unsigned int UART4_TX_DATA;

volatile unsigned int UART4_RX_DATA;

volatile unsigned int UART5_TX_DATA;

volatile unsigned int UART5_RX_DATA;

volatile unsigned int ENET1_RX_DATA0;

volatile unsigned int ENET1_RX_DATA1;

volatile unsigned int ENET1_RX_EN;

volatile unsigned int ENET1_TX_DATA0;

volatile unsigned int ENET1_TX_DATA1;

volatile unsigned int ENET1_TX_EN;

volatile unsigned int ENET1_TX_CLK;

volatile unsigned int ENET1_RX_ER;

volatile unsigned int ENET2_RX_DATA0;

volatile unsigned int ENET2_RX_DATA1;

volatile unsigned int ENET2_RX_EN;

volatile unsigned int ENET2_TX_DATA0;

volatile unsigned int ENET2_TX_DATA1;

volatile unsigned int ENET2_TX_EN;

volatile unsigned int ENET2_TX_CLK;

volatile unsigned int ENET2_RX_ER;

volatile unsigned int LCD_CLK;

volatile unsigned int LCD_ENABLE;

volatile unsigned int LCD_HSYNC;

volatile unsigned int LCD_VSYNC;

volatile unsigned int LCD_RESET;

volatile unsigned int LCD_DATA00;

volatile unsigned int LCD_DATA01;

volatile unsigned int LCD_DATA02;

volatile unsigned int LCD_DATA03;

volatile unsigned int LCD_DATA04;

volatile unsigned int LCD_DATA05;

volatile unsigned int LCD_DATA06;

volatile unsigned int LCD_DATA07;

volatile unsigned int LCD_DATA08;

volatile unsigned int LCD_DATA09;

volatile unsigned int LCD_DATA10;

volatile unsigned int LCD_DATA11;

volatile unsigned int LCD_DATA12;

volatile unsigned int LCD_DATA13;

volatile unsigned int LCD_DATA14;

volatile unsigned int LCD_DATA15;

volatile unsigned int LCD_DATA16;

volatile unsigned int LCD_DATA17;

volatile unsigned int LCD_DATA18;

volatile unsigned int LCD_DATA19;

volatile unsigned int LCD_DATA20;

volatile unsigned int LCD_DATA21;

volatile unsigned int LCD_DATA22;

volatile unsigned int LCD_DATA23;

volatile unsigned int NAND_RE_B;

volatile unsigned int NAND_WE_B;

volatile unsigned int NAND_DATA00;

volatile unsigned int NAND_DATA01;

volatile unsigned int NAND_DATA02;

volatile unsigned int NAND_DATA03;

volatile unsigned int NAND_DATA04;

volatile unsigned int NAND_DATA05;

volatile unsigned int NAND_DATA06;

volatile unsigned int NAND_DATA07;

volatile unsigned int NAND_ALE;

volatile unsigned int NAND_WP_B;

volatile unsigned int NAND_READY_B;

volatile unsigned int NAND_CE0_B;

volatile unsigned int NAND_CE1_B;

volatile unsigned int NAND_CLE;

volatile unsigned int NAND_DQS;

volatile unsigned int SD1_CMD;

volatile unsigned int SD1_CLK;

volatile unsigned int SD1_DATA0;

volatile unsigned int SD1_DATA1;

volatile unsigned int SD1_DATA2;

volatile unsigned int SD1_DATA3;

volatile unsigned int CSI_MCLK;

volatile unsigned int CSI_PIXCLK;

volatile unsigned int CSI_VSYNC;

volatile unsigned int CSI_HSYNC;

volatile unsigned int CSI_DATA00;

volatile unsigned int CSI_DATA01;

volatile unsigned int CSI_DATA02;

volatile unsigned int CSI_DATA03;

volatile unsigned int CSI_DATA04;

volatile unsigned int CSI_DATA05;

volatile unsigned int CSI_DATA06;

volatile unsigned int CSI_DATA07;

}IOMUX_SW_MUX_Type;

typedef struct

{

volatile unsigned int DRAM_ADDR00;

volatile unsigned int DRAM_ADDR01;

volatile unsigned int DRAM_ADDR02;

volatile unsigned int DRAM_ADDR03;

volatile unsigned int DRAM_ADDR04;

volatile unsigned int DRAM_ADDR05;

volatile unsigned int DRAM_ADDR06;

volatile unsigned int DRAM_ADDR07;

volatile unsigned int DRAM_ADDR08;

volatile unsigned int DRAM_ADDR09;

volatile unsigned int DRAM_ADDR10;

volatile unsigned int DRAM_ADDR11;

volatile unsigned int DRAM_ADDR12;

volatile unsigned int DRAM_ADDR13;

volatile unsigned int DRAM_ADDR14;

volatile unsigned int DRAM_ADDR15;

volatile unsigned int DRAM_DQM0;

volatile unsigned int DRAM_DQM1;

volatile unsigned int DRAM_RAS_B;

volatile unsigned int DRAM_CAS_B;

volatile unsigned int DRAM_CS0_B;

volatile unsigned int DRAM_CS1_B;

volatile unsigned int DRAM_SDWE_B;

volatile unsigned int DRAM_ODT0;

volatile unsigned int DRAM_ODT1;

volatile unsigned int DRAM_SDBA0;

volatile unsigned int DRAM_SDBA1;

volatile unsigned int DRAM_SDBA2;

volatile unsigned int DRAM_SDCKE0;

volatile unsigned int DRAM_SDCKE1;

volatile unsigned int DRAM_SDCLK0_P;

volatile unsigned int DRAM_SDQS0_P;

volatile unsigned int DRAM_SDQS1_P;

volatile unsigned int DRAM_RESET;

volatile unsigned int TEST_MODE;

volatile unsigned int POR_B;

volatile unsigned int ONOFF;

volatile unsigned int SNVS_PMIC_ON_REQ;

volatile unsigned int CCM_PMIC_STBY_REQ;

volatile unsigned int BOOT_MODE0;

volatile unsigned int BOOT_MODE1;

volatile unsigned int SNVS_TAMPER0;

volatile unsigned int SNVS_TAMPER1;

volatile unsigned int SNVS_TAMPER2;

volatile unsigned int SNVS_TAMPER3;

volatile unsigned int SNVS_TAMPER4;

volatile unsigned int SNVS_TAMPER5;

volatile unsigned int SNVS_TAMPER6;

volatile unsigned int SNVS_TAMPER7;

volatile unsigned int SNVS_TAMPER8;

volatile unsigned int SNVS_TAMPER9;

volatile unsigned int JTAG_MOD;

volatile unsigned int JTAG_TMS;

volatile unsigned int JTAG_TDO;

volatile unsigned int JTAG_TDI;

volatile unsigned int JTAG_TCK;

volatile unsigned int JTAG_TRST_B;

volatile unsigned int GPIO1_IO00;

volatile unsigned int GPIO1_IO01;

volatile unsigned int GPIO1_IO02;

volatile unsigned int GPIO1_IO03;

volatile unsigned int GPIO1_IO04;

volatile unsigned int GPIO1_IO05;

volatile unsigned int GPIO1_IO06;

volatile unsigned int GPIO1_IO07;

volatile unsigned int GPIO1_IO08;

volatile unsigned int GPIO1_IO09;

volatile unsigned int UART1_TX_DATA;

volatile unsigned int UART1_RX_DATA;

volatile unsigned int UART1_CTS_B;

volatile unsigned int UART1_RTS_B;

volatile unsigned int UART2_TX_DATA;

volatile unsigned int UART2_RX_DATA;

volatile unsigned int UART2_CTS_B;

volatile unsigned int UART2_RTS_B;

volatile unsigned int UART3_TX_DATA;

volatile unsigned int UART3_RX_DATA;

volatile unsigned int UART3_CTS_B;

volatile unsigned int UART3_RTS_B;

volatile unsigned int UART4_TX_DATA;

volatile unsigned int UART4_RX_DATA;

volatile unsigned int UART5_TX_DATA;

volatile unsigned int UART5_RX_DATA;

volatile unsigned int ENET1_RX_DATA0;

volatile unsigned int ENET1_RX_DATA1;

volatile unsigned int ENET1_RX_EN;

volatile unsigned int ENET1_TX_DATA0;

volatile unsigned int ENET1_TX_DATA1;

volatile unsigned int ENET1_TX_EN;

volatile unsigned int ENET1_TX_CLK;

volatile unsigned int ENET1_RX_ER;

volatile unsigned int ENET2_RX_DATA0;

volatile unsigned int ENET2_RX_DATA1;

volatile unsigned int ENET2_RX_EN;

volatile unsigned int ENET2_TX_DATA0;

volatile unsigned int ENET2_TX_DATA1;

volatile unsigned int ENET2_TX_EN;

volatile unsigned int ENET2_TX_CLK;

volatile unsigned int ENET2_RX_ER;

volatile unsigned int LCD_CLK;

volatile unsigned int LCD_ENABLE;

volatile unsigned int LCD_HSYNC;

volatile unsigned int LCD_VSYNC;

volatile unsigned int LCD_RESET;

volatile unsigned int LCD_DATA00;

volatile unsigned int LCD_DATA01;

volatile unsigned int LCD_DATA02;

volatile unsigned int LCD_DATA03;

volatile unsigned int LCD_DATA04;

volatile unsigned int LCD_DATA05;

volatile unsigned int LCD_DATA06;

volatile unsigned int LCD_DATA07;

volatile unsigned int LCD_DATA08;

volatile unsigned int LCD_DATA09;

volatile unsigned int LCD_DATA10;

volatile unsigned int LCD_DATA11;

volatile unsigned int LCD_DATA12;

volatile unsigned int LCD_DATA13;

volatile unsigned int LCD_DATA14;

volatile unsigned int LCD_DATA15;

volatile unsigned int LCD_DATA16;

volatile unsigned int LCD_DATA17;

volatile unsigned int LCD_DATA18;

volatile unsigned int LCD_DATA19;

volatile unsigned int LCD_DATA20;

volatile unsigned int LCD_DATA21;

volatile unsigned int LCD_DATA22;

volatile unsigned int LCD_DATA23;

volatile unsigned int NAND_RE_B;

volatile unsigned int NAND_WE_B;

volatile unsigned int NAND_DATA00;

volatile unsigned int NAND_DATA01;

volatile unsigned int NAND_DATA02;

volatile unsigned int NAND_DATA03;

volatile unsigned int NAND_DATA04;

volatile unsigned int NAND_DATA05;

volatile unsigned int NAND_DATA06;

volatile unsigned int NAND_DATA07;

volatile unsigned int NAND_ALE;

volatile unsigned int NAND_WP_B;

volatile unsigned int NAND_READY_B;

volatile unsigned int NAND_CE0_B;

volatile unsigned int NAND_CE1_B;

volatile unsigned int NAND_CLE;

volatile unsigned int NAND_DQS;

volatile unsigned int SD1_CMD;

volatile unsigned int SD1_CLK;

volatile unsigned int SD1_DATA0;

volatile unsigned int SD1_DATA1;

volatile unsigned int SD1_DATA2;

volatile unsigned int SD1_DATA3;

volatile unsigned int CSI_MCLK;

volatile unsigned int CSI_PIXCLK;

volatile unsigned int CSI_VSYNC;

volatile unsigned int CSI_HSYNC;

volatile unsigned int CSI_DATA00;

volatile unsigned int CSI_DATA01;

volatile unsigned int CSI_DATA02;

volatile unsigned int CSI_DATA03;

volatile unsigned int CSI_DATA04;

volatile unsigned int CSI_DATA05;

volatile unsigned int CSI_DATA06;

volatile unsigned int CSI_DATA07;

volatile unsigned int GRP_ADDDS;

volatile unsigned int GRP_DDRMODE_CTL;

volatile unsigned int GRP_B0DS;

volatile unsigned int GRP_DDRPK;

volatile unsigned int GRP_CTLDS;

volatile unsigned int GRP_B1DS;

volatile unsigned int GRP_DDRHYS;

volatile unsigned int GRP_DDRPKE;

volatile unsigned int GRP_DDRMODE;

volatile unsigned int GRP_DDR_TYPE;

}IOMUX_SW_PAD_Type;

/*

* GPIO寄存器结构体

*/

typedef struct

{

volatile unsigned int DR;

volatile unsigned int GDIR;

volatile unsigned int PSR;

volatile unsigned int ICR1;

volatile unsigned int ICR2;

volatile unsigned int IMR;

volatile unsigned int ISR;

volatile unsigned int EDGE_SEL;

}GPIO_Type;

/*

* 外设指针

*/

#define CCM ((CCM_Type *)CCM_BASE)

#define CCM_ANALOG ((CCM_ANALOG_Type *)CCM_ANALOG_BASE)

#define IOMUX_SW_MUX ((IOMUX_SW_MUX_Type *)IOMUX_SW_MUX_BASE)

#define IOMUX_SW_PAD ((IOMUX_SW_PAD_Type *)IOMUX_SW_PAD_BASE)

#define GPIO1 ((GPIO_Type *)GPIO1_BASE)

#define GPIO2 ((GPIO_Type *)GPIO2_BASE)

#define GPIO3 ((GPIO_Type *)GPIO3_BASE)

#define GPIO4 ((GPIO_Type *)GPIO4_BASE)

#define GPIO5 ((GPIO_Type *)GPIO5_BASE)

main.c :

/**************************************************************

Copyright © zuozhongkai Co., Ltd. 1998-2019. All rights reserved.

文件名 : mian.c

作者 : 左忠凯

版本 : V1.0

描述 : I.MX6U开发板裸机实验2 C语言点灯

使用C语言来点亮开发板上的LED灯,学习和掌握如何用C语言来

完成对I.MX6U处理器的GPIO初始化和控制。

其他 : 无

日志 : 初版V1.0 2019/1/3 左忠凯创建

**************************************************************/

#include "main.h"

/*

* @description : 使能I.MX6U所有外设时钟

* @param : 无

* @return : 无

*/

void clk_enable(void)

{

CCM_CCGR0 = 0xffffffff;

CCM_CCGR1 = 0xffffffff;

CCM_CCGR2 = 0xffffffff;

CCM_CCGR3 = 0xffffffff;

CCM_CCGR4 = 0xffffffff;

CCM_CCGR5 = 0xffffffff;

CCM_CCGR6 = 0xffffffff;

}

/*

* @description : 初始化LED对应的GPIO

* @param : 无

* @return : 无

*/

void led_init(void)

{

/* 1、初始化IO复用 */

SW_MUX_GPIO1_IO03 = 0x5; /* 复用为GPIO1_IO03 */

/* 2、、配置GPIO1_IO03的IO属性

*bit 16:0 HYS关闭

*bit [15:14]: 00 默认下拉

*bit [13]: 0 kepper功能

*bit [12]: 1 pull/keeper使能

*bit [11]: 0 关闭开路输出

*bit [7:6]: 10 速度100Mhz

*bit [5:3]: 110 R0/6驱动能力

*bit [0]: 0 低转换率

*/

SW_PAD_GPIO1_IO03 = 0X10B0;

/* 3、初始化GPIO */

GPIO1_GDIR = 0X0000008; /* GPIO1_IO03设置为输出 */

/* 4、设置GPIO1_IO03输出低电平,打开LED0 */

GPIO1_DR = 0X0;

}

/*

* @description : 打开LED灯

* @param : 无

* @return : 无

*/

void led_on(void)

{

/*

* 将GPIO1_DR的bit3清零

*/

GPIO1_DR &= ~(1<<3);

}

/*

* @description : 关闭LED灯

* @param : 无

* @return : 无

*/

void led_off(void)

{

/*

* 将GPIO1_DR的bit3置1

*/

GPIO1_DR |= (1<<3);

}

/*

* @description : 短时间延时函数

* @param - n : 要延时循环次数(空操作循环次数,模式延时)

* @return : 无

*/

void delay_short(volatile unsigned int n)

{

while(n--){}

}

/*

* @description : 延时函数,在396Mhz的主频下

* 延时时间大约为1ms

* @param - n : 要延时的ms数

* @return : 无

*/

void delay(volatile unsigned int n)

{

while(n--)

{

delay_short(0x7ff);

}

}

/*

* @description : mian函数

* @param : 无

* @return : 无

*/

int main(void)

{

clk_enable(); /* 使能所有的时钟 */

led_init(); /* 初始化led */

while(1) /* 死循环 */

{

led_off(); /* 关闭LED */

delay(500); /* 延时大约500ms */

led_on(); /* 打开LED */

delay(500); /* 延时大约500ms */

}

return 0;

}

四,编译下载验证

博客围绕STM32展开,介绍了在STM32里程序存储器、数据存储器、寄存器和输入输出端口被组织在同一4GB线性地址空间,数据字节以小端格式存放。还以GPIOE为例进行说明,最后提及编译下载验证。

博客围绕STM32展开,介绍了在STM32里程序存储器、数据存储器、寄存器和输入输出端口被组织在同一4GB线性地址空间,数据字节以小端格式存放。还以GPIOE为例进行说明,最后提及编译下载验证。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?