这篇题目为"A Practical Parallel CRC Generation Method"的论文是由Evgeni Stavinov在2011年发表在IEEE Transactions on Computers上的一篇文章。该论文提出了一种实用的并行CRC生成方法,主要针对高速网络和存储系统中需要处理大量数据的情况。该方法通过使用多项式因子化和位重排序技术,将CRC生成过程拆分成多个部分,并利用现代计算机的多核架构来加速计算。作者还通过实验验证了该方法的高效性和可扩展性,并与其他常见的CRC生成算法进行了比较。

论文的第一部分介绍了CRC算法的基本原理和应用场景,并讨论了串行CRC生成算法的局限性和不足之处。然后,作者提出了一种基于并行计算的CRC生成方法,可以有效地减少生成CRC所需的时间和资源消耗。

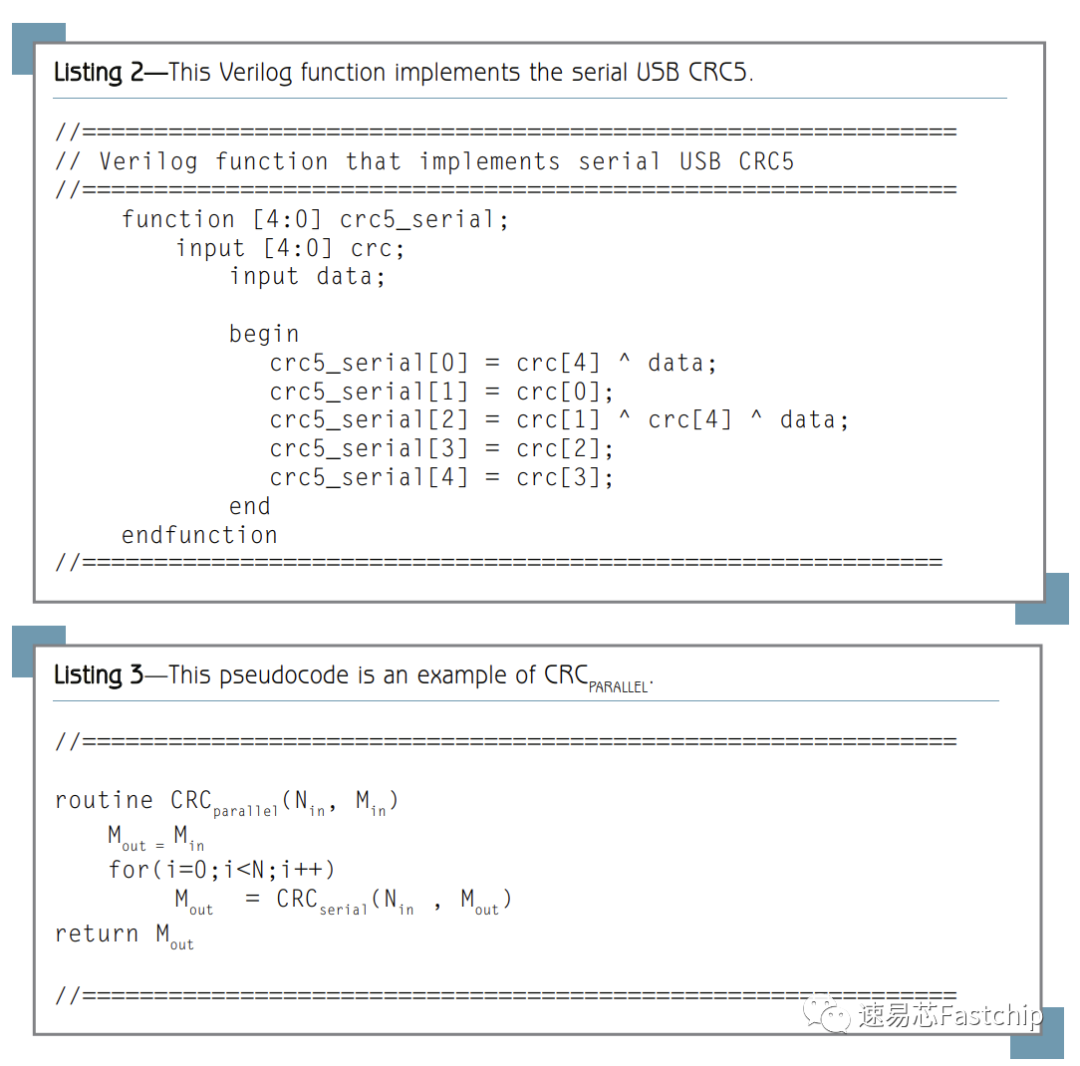

图表1 传统串行crc和并行crc的生成伪代码

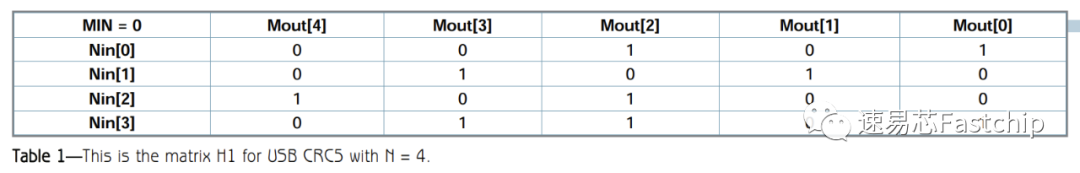

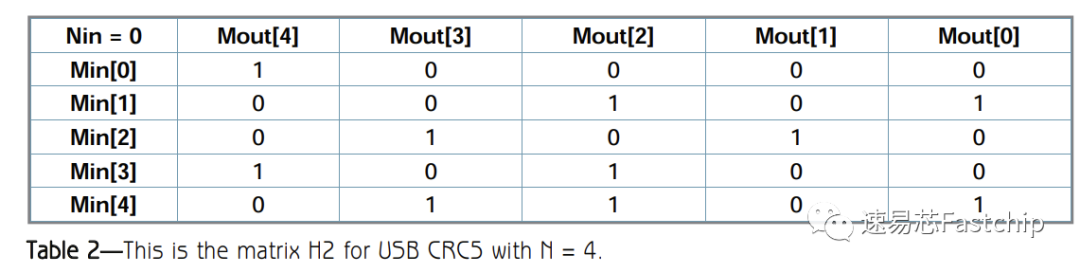

接下来,论文详细介绍了这种方法的实现过程和技术细节。作者使用了多线程和SIMD指令等技术,实现了一个高效的并行CRC生成算法。根据生成的两个矩阵便可以推导出并行crc算法。

图表2 并行crc生成算法的矩阵1

图表3 并行生成算法的矩阵2

最后,论文总结了这种实用的并行CRC生成方法的优点和适用范围,并探讨了未来研究的方向和可能的改进之处。并对其进行了性能测试和评估。结果表明,采用该方法可以在保持数据完整性的同时,大幅提高CRC生成的速度和效率。

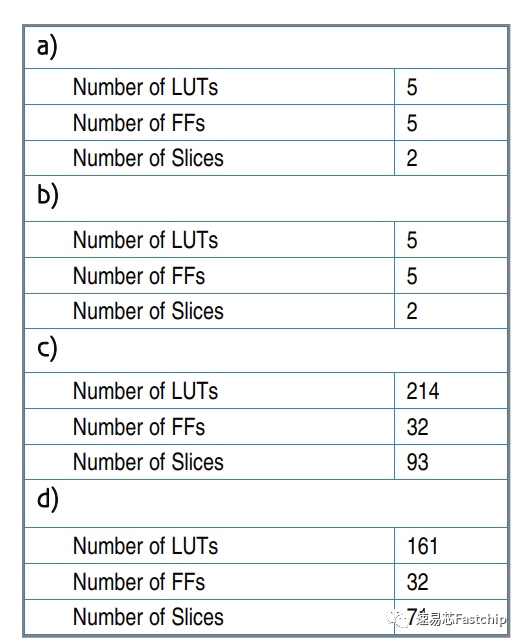

图表4 a)使用“for loop”方法的USB CRC5,4位数据的逻辑利用率。

b) 使用“XOR”方法的USB CRC5,4位数据的逻辑利用率。

c)使用“for loop”方法对 CRC32,32 位数据的逻辑利用率。

d)使用“XOR”方法对 CRC32,32 位数据的逻辑利用率。

综合来说,该论文提出了一种创新的、高效的并行CRC生成算法,通过采用多线程和SIMD指令等技术,极大地提高了CRC生成的速度和效率。这一方法具有广泛的应用前景,可以为数据通信、存储等领域带来更加可靠和高效的CRC。除此之外,作者开发了一个网站(http://outputlogic.com/)可以根据参数直接生成想要的并行crc算法代码。

文章作者:速易芯张浩哲

8472

8472

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?