目录

如何使用存储芯片组成一个存储器?

-

确定设计容量:多大设计容量

-

芯片的选用:多大容量,位数,多少片,如何分组

-

地址分配:将 CPU 提供的全部地址空间的哪些地址空间分配给所设计的存储器,确定各芯片组的片内地址

-

片选逻辑:高位地址产生芯片组所需的片选信号

-

信号线的连接:所有信号线如何连接

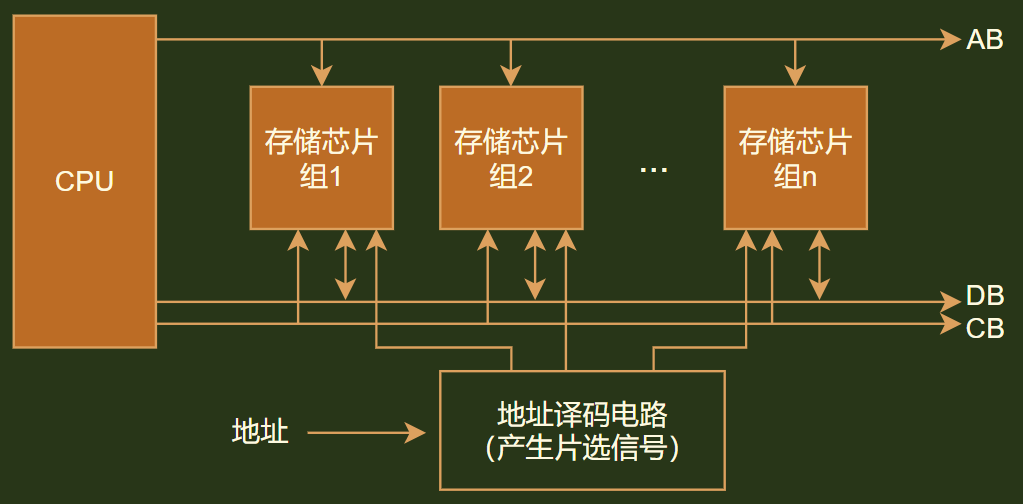

示意图

涉及地址分配、译码选片和译码选单元等。

一、主存容量的扩展

主存容量 = 字数 × 位数

字数是指可编址的存储单元个数,位数是指每个编址存储单元的位数。

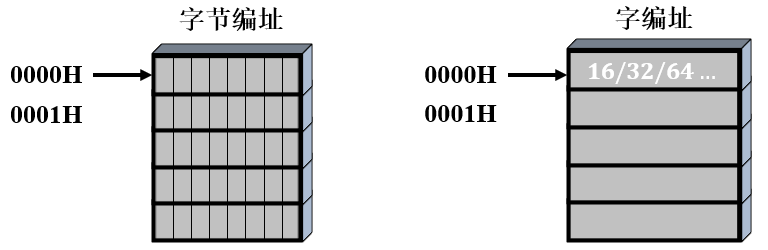

1. 位扩展

位扩展是指在位数方向扩展。

位扩展的连接方式是将各存储芯片的 地址线、片选线和读/写线 相应地 并联 起来,而将各芯片的 数据线单独列出。

例如:用 64K×1 的 SRAM 存储芯片组成 64K×8 的存储器,需要 8 块芯片。

当 CPU 访问该存储器时,其发出的地址和控制信号同时传给 8 个芯片,选中每个芯片的同一单元,其单元的内容被同时读至数据总线的相应位,或将数据总线上的内容分别同时写入相应单元。

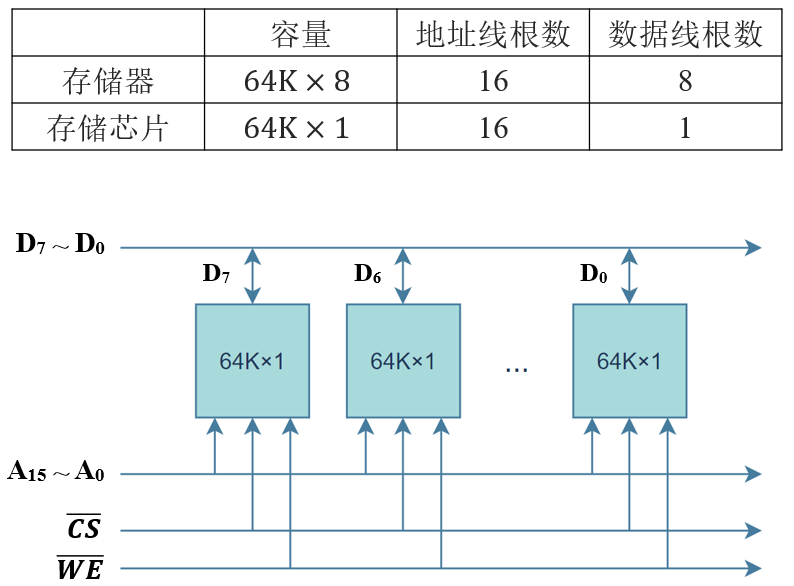

2. 字扩展(编址空间扩展)

字扩展是指在字数方向扩展。

字扩展的连接方式是将芯片的 数据线、读/写线并联,由片选信号(高位地址线译码)选定存储芯片,低位地址线直接连接各芯片。

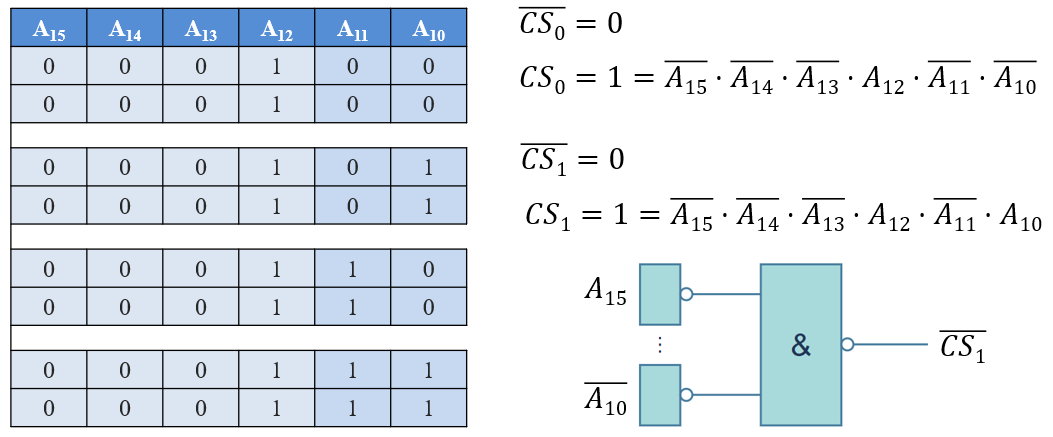

例如:用 16K×8 的 SRAM 组成 64K×8 的存储器,需要 4 块芯片。

3. 字和位同时扩展

当构成一个容量较大的存储器时,往往需要在字数方向和位数方向上同时扩展,这将是前两种扩展的组合。

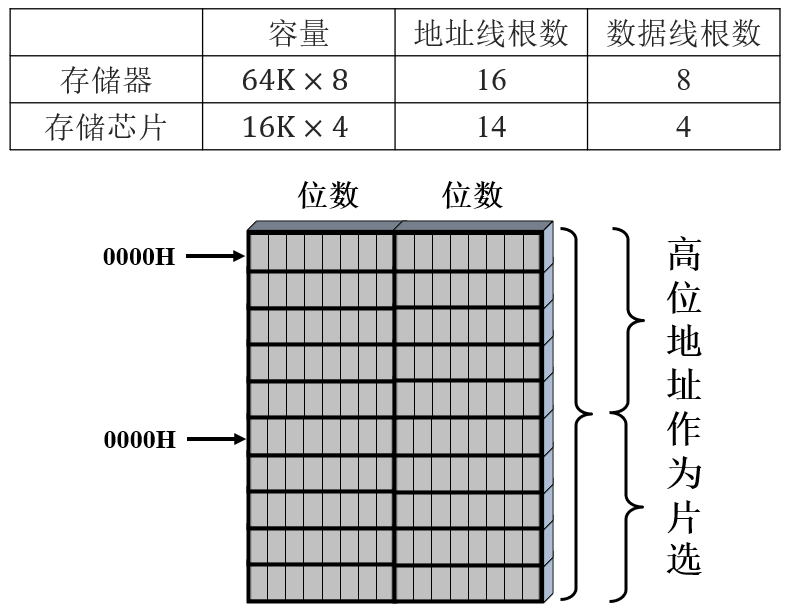

例如:用 16K×4 的 SRAM 组成 64K×8 的存储器,需要 8 个芯片。

- 第一题

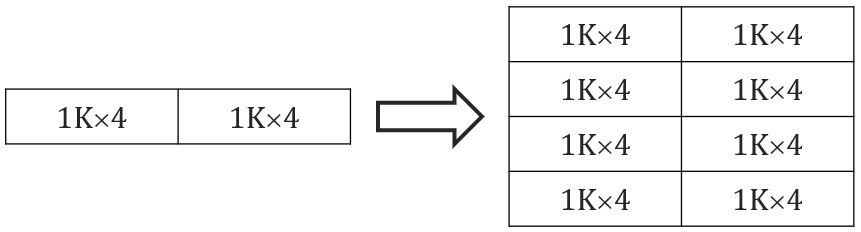

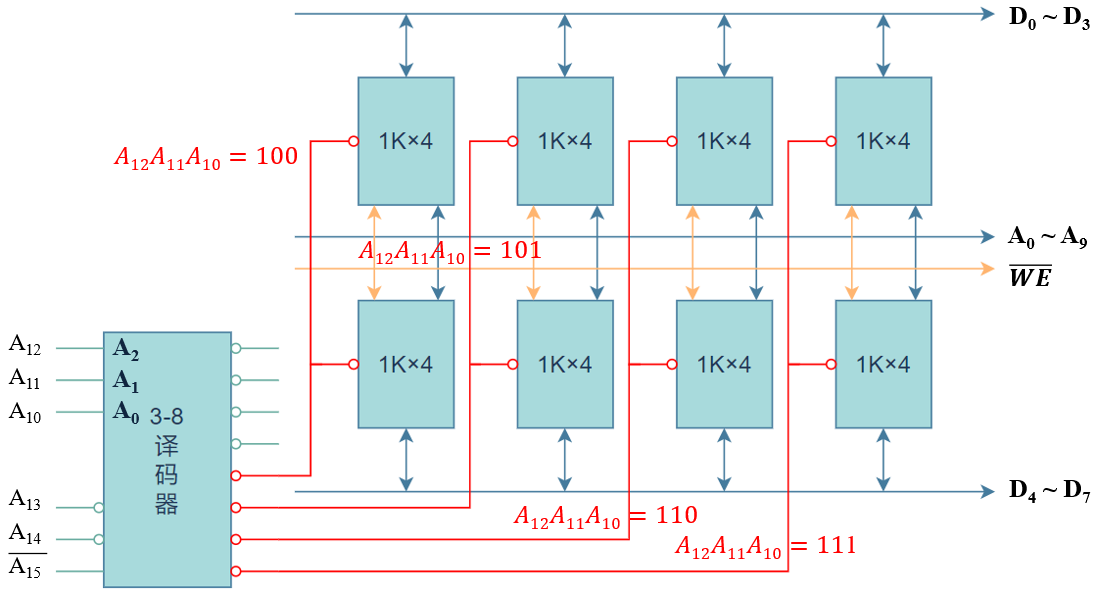

用 2114(1K×4)SRAM 芯片组成容量为 4K×8 的存储器,存储器的起始地址为 1000H 。

假设 CPU 地址总线 A15~A0,数据总线 D7~D0,读/写信号线 R/W。

设计步骤:

1、计算容量和芯片数

先位扩展,再字扩展

2、地址分配与片选逻辑

地址总线 A15~A0,片内寻址需要 10 根,因此片外寻址/片选信号使用 A15~A10 。

由于存储器起始地址为 1000H,因此第一组起始地址为 1000H 。

因为我们这里是 16 根(4 的整数倍),所以从左往右或从右往左数都可。但如果地址线根数为奇数,那么只能从右往左数。

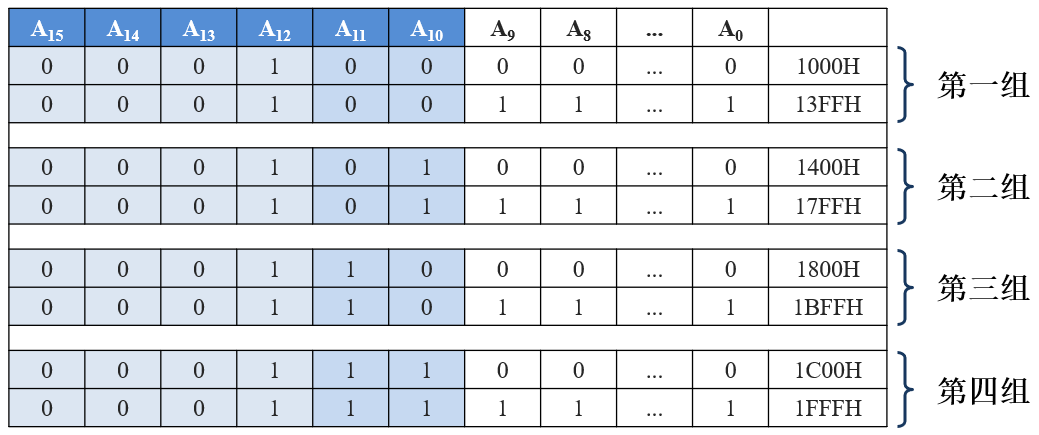

片选逻辑表达式:

片选信号低电平有效

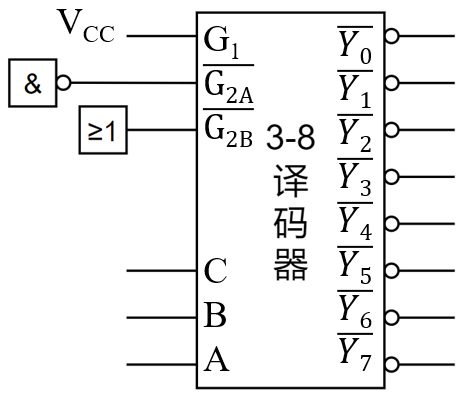

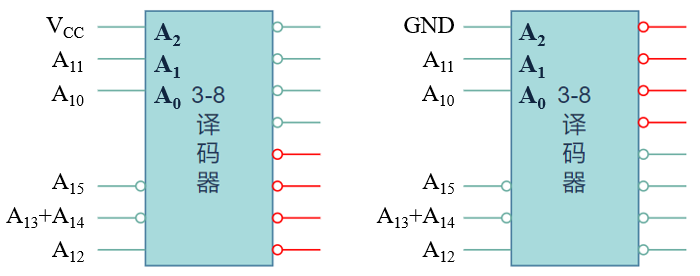

如果使用 3-8译码器 产生片选信号,可将上述状态看作:

![]()

3、连接方式

将除了与芯片连接的地址以外的所有高位地址用于译码产生片选信号,称为 全译码方式 。

其它连接方式:

- 第二题

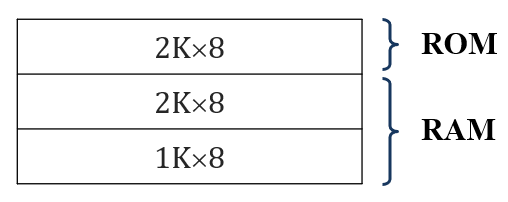

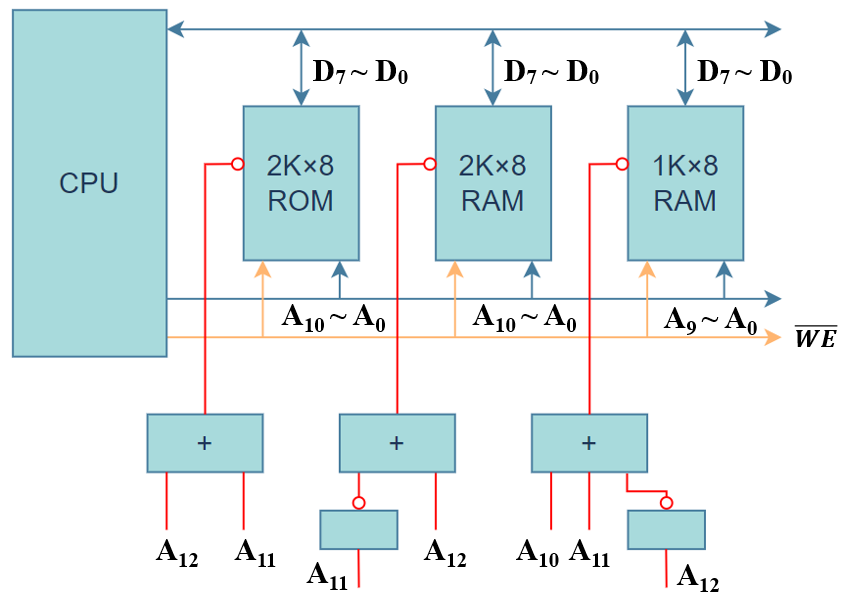

某存储器按字节编址。

其中,0000H~07FFH 为 ROM 区,选用 EPROM 芯片(2KB/片);

0800H~13FFH 为 RAM 区,选用 RAM 芯片(2KB/片和1KB/片);

地址总线 A15~A0 。给出地址分配和片选逻辑。

1、计算容量和芯片数

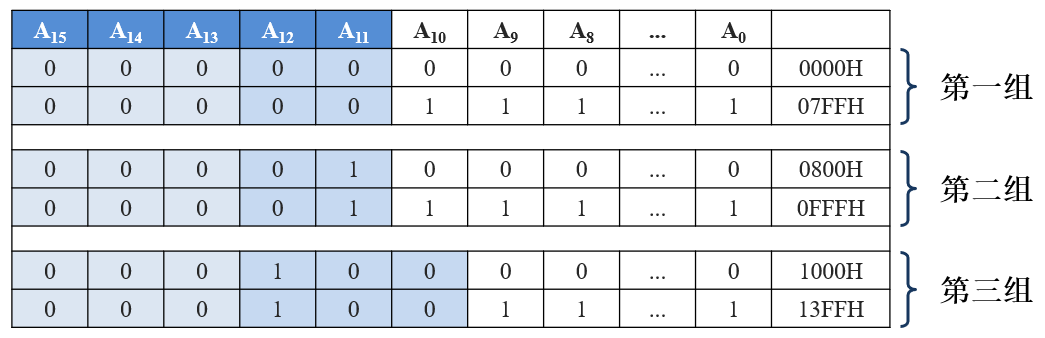

2、地址分配与片选逻辑

片选逻辑表达式:

片选信号低电平有效

部分译码 —— 相同的高位地址不参与译码

3、连接方式

将除了与芯片连接的地址外的部分高位地址用于译码产生片选信号,称为 部分译码方式 。

采用部分译码方式可以节省器件,但存在地址重叠问题。

- 第三题

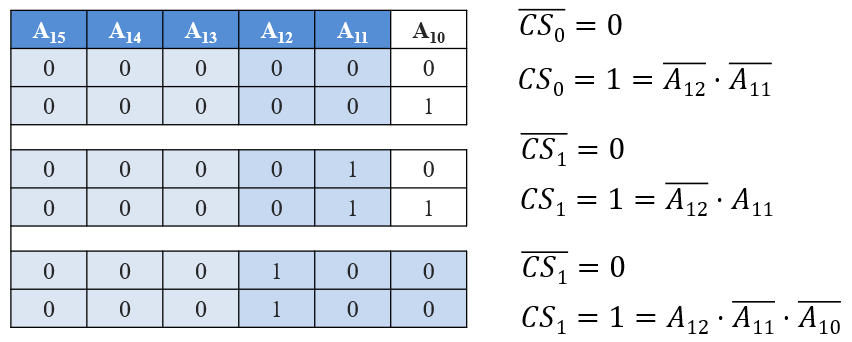

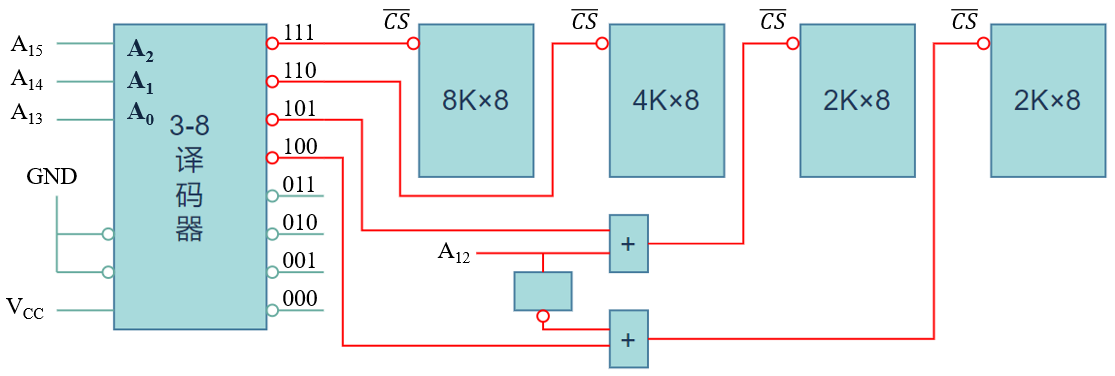

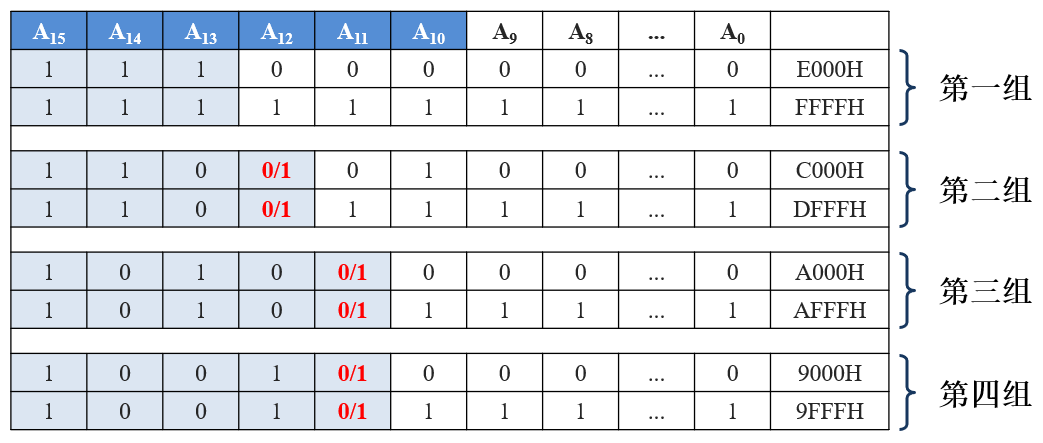

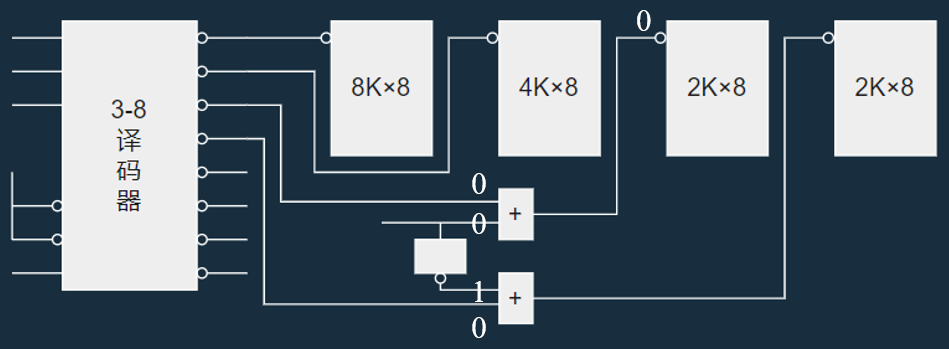

CPU 地址总线 16 条,数据总线 8 条,有以下存储器连接电路:

(1)写出每片芯片的地址范围

(2)分析芯片地址的重叠情况

第(1)问:

- 计算每组芯片所需地址线根数和用于片选的线的根数

- 根据图示3-8译码器的输出确定用于片选的高位地址

- 确定每一组的地址范围

第二组未连接 A12,第三、第四组未连接 A11,因此对应位可为 1 也可为 0 。

对于第三、第四组,根据3-8译码器采用负逻辑和片选信号低电平有效,得出 A12 的值:

第(2)问:

- 第四题

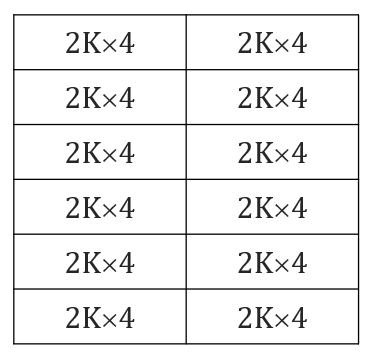

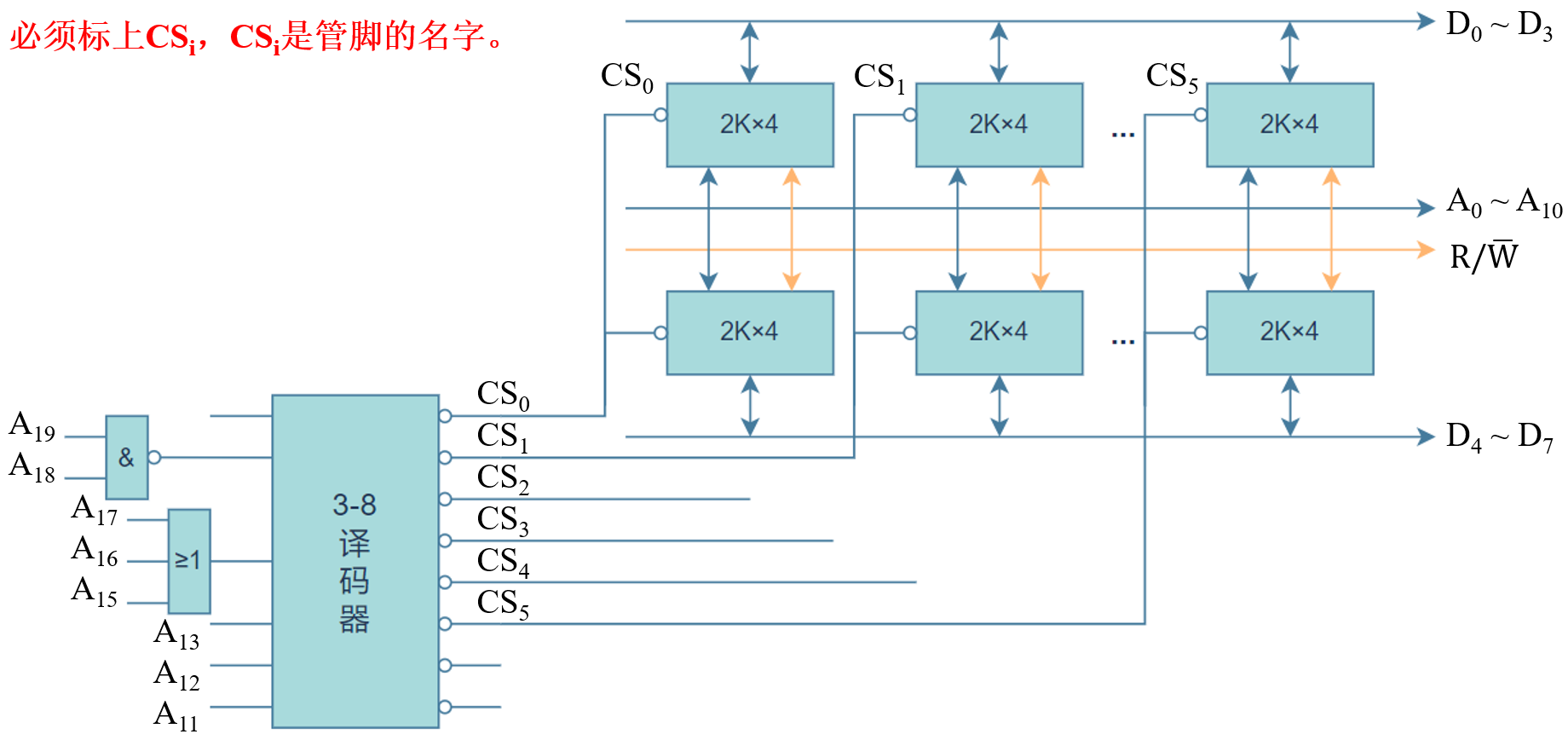

用 2K×4b 的芯片(若干片)构成一个 12KB 的存储器,其地址范围在 C0000~C2FFFH 以及C4000~C6FFF 之间。数据总线为 D0~D7,地址总线为 A0~A19(高地址)。对芯片读写采用R/W控制,且片选要求采用3-8译码器的输出,如下图所示。

(1)需要 2K×4b 的芯片多少片构成 12KB 的存储器?

(2)每组芯片地址线如何分配?

(3)选择哪些地址线作为译码器的使能端?

(4)选择哪些地址线作为译码器的输入端?

(5)在不增加其他器件的条件下,画出存储器逻辑电路图。

第(1)问:需要 12 片

第(2)问:由于每组 2KB,所以需要 11 根地址线用于片内单元译码,即 A0 ~ A10 。

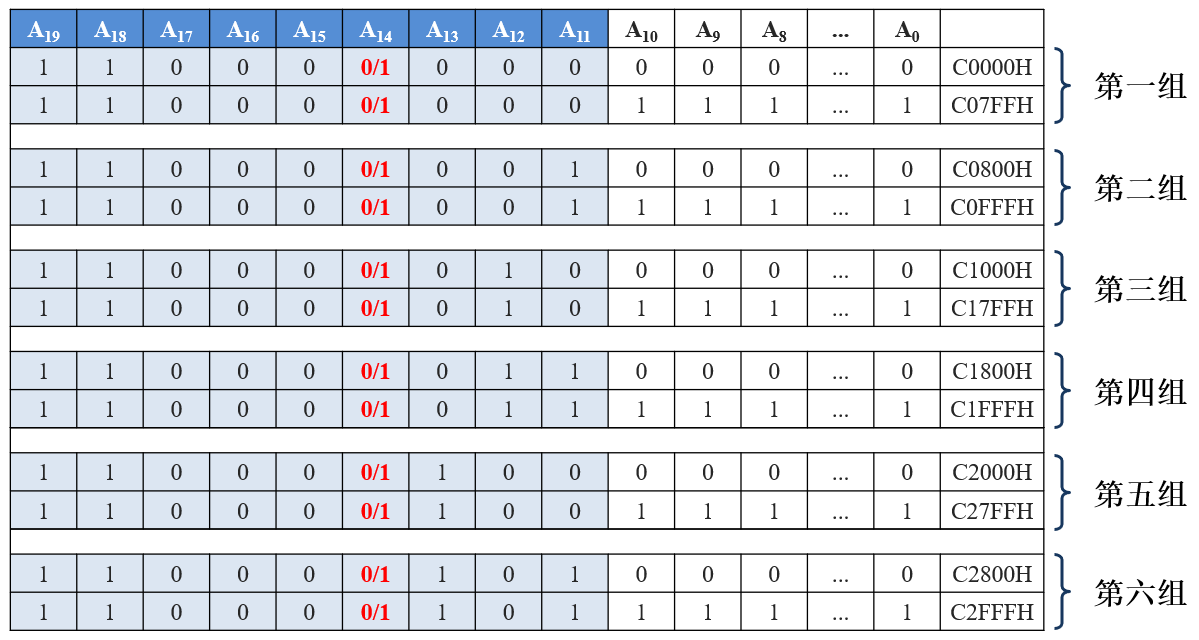

第(3)(4)问:

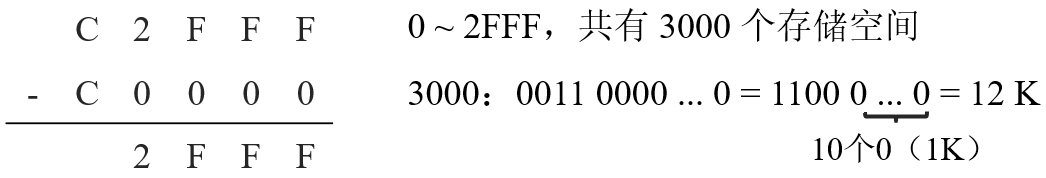

地址范围在 C0000~C2FFFH 以及 C4000~C6FFF 之间,共需 24K 存储空间。

(技术点)快速计算存储器容量:

但是题目要求的存储器只有 12K 存储空间,因此存储器的容量不足,存在地址重叠问题。

若存在地址重叠问题,那么至少有一根地址线不参与译码。根据所给地址范围,我们易得 A14 不参与译码。因此,能够参加片选译码的只有 A11~A13 和 A15~A19 。

由上表可得,A15~A19 不变,适合作为使能端;A11~A13 改变,适合作为输入端。

第(5)问:

二、数据校验 —— 奇偶校验

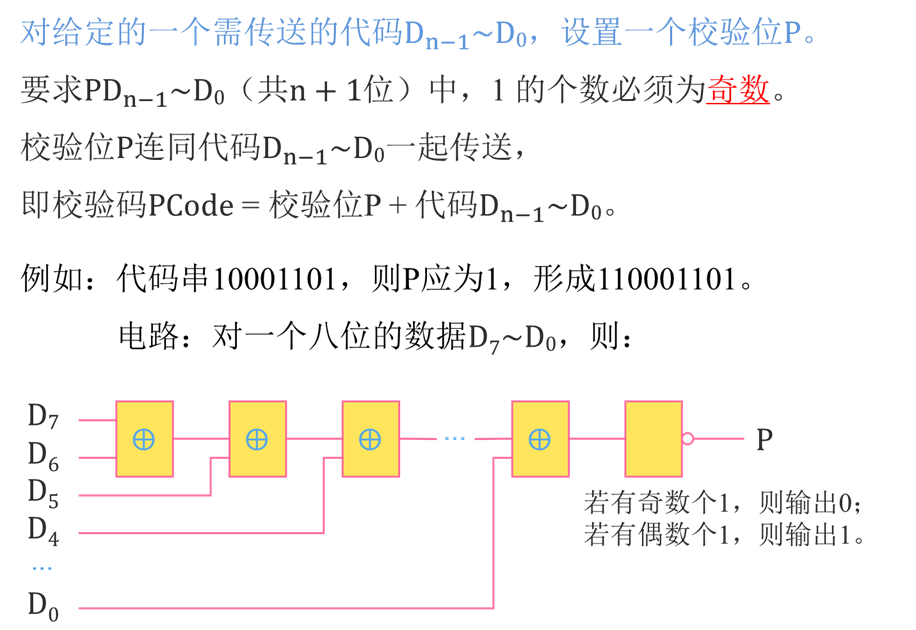

1. 奇校验

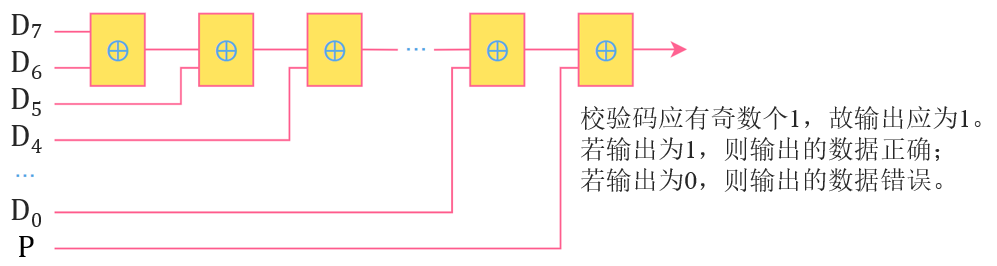

代码接受方的检验电路:

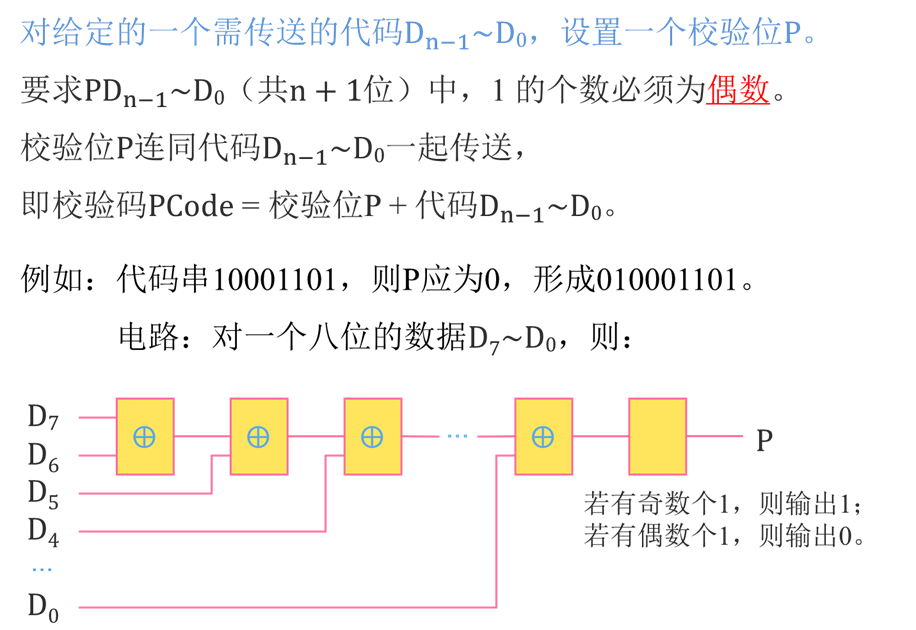

2. 偶校验

优缺点:奇偶校验操作简单,但是只能检验一位错误,并且不能指出错误位置。

博客主要介绍了主存容量的扩展和数据校验中的奇偶校验。主存容量扩展包括位扩展、字扩展和字位同时扩展,并通过多道例题讲解设计步骤、地址分配、片选逻辑和连接方式。奇偶校验分为奇校验和偶校验,操作简单但只能检验一位错误且无法指出位置。

博客主要介绍了主存容量的扩展和数据校验中的奇偶校验。主存容量扩展包括位扩展、字扩展和字位同时扩展,并通过多道例题讲解设计步骤、地址分配、片选逻辑和连接方式。奇偶校验分为奇校验和偶校验,操作简单但只能检验一位错误且无法指出位置。

2224

2224

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?