一、前言

这段时间正好在学习一些开源RISC-V项目,Ibex作为一款优秀的RISC-V core自然成为首选目标。Ibex最早从PULP平台下的zero-riscy发展而来,目前由非盈利组织LowRISC发展和维护,该组织还开发维护了OpenTitan平台。Ibex有官方文档,并且有simple system例程的仿真流程,但是过程中仍有许多需要注意的地方,否则会碰上各种报错导致流程无法走完,因此基于当前版本梳理一份更细致的流程供参考。

二、系统环境

本人尝试过CentOS Stream 8, Ubuntu 22.04版本的Linux系统,都可以完成整个流程,体验上来说Ubuntu系统在很多插件的安装上更为便捷,可以节省大量时间精力。

- 若使用虚拟机,可以选择VMware Workstation 17 Player,官方的个人免费版,下载安装即可用;

- 若是Window11系统,可以使用WSL2,支持包括Ubuntu 22.04版本内的多种系统可选

个人认为, WSL2下操作比虚拟机更流畅,且迁移方便(默认Linux系统安装在系统盘下,强烈建议迁移到其他磁盘,具体操作可参考《WSL迁移到非系统盘》),不足之处是暂时不支持图像界面(没有桌面,但是软件GUI还是可以打开的)。

三、软件安装

Ibex仿真流程需要的工具有Verilator,Fusesoc以及riscv编译工具链。

首先保证apt以及pip均已是最新版本。

sudo apt update && sudo apt upgrade

sudo pip install -U pip3-1 Ibex项目下载

直接从Git上下载整个项目即可

git clone https://github.com/lowRISC/ibex.git3-2 Verilator安装

推荐从Git上下载安装Verilator,可以更加灵活的进行配置。官方文档上有安装指导,;根据提供的脚本(已摘抄到下图)一一执行下来即可。

注:目前Verilator的版本已更新到v5.x,在Ibex中直接运行最新版本会出现编译报错(也有解决办法),通过git checkout将版本切换到v4.x任一版本即可避免此问题,git tag查看可切换的具体版本号。

# Prerequisites:

#sudo apt-get install git help2man perl python3 make autoconf g++ flex bison ccache

#sudo apt-get install libgoogle-perftools-dev numactl perl-doc

#sudo apt-get install libfl2 # Ubuntu only (ignore if gives error)

#sudo apt-get install libfl-dev # Ubuntu only (ignore if gives error)

#sudo apt-get install zlibc zlib1g zlib1g-dev # Ubuntu only (ignore if gives error)

git clone https://github.com/verilator/verilator # Only first time

# Every time you need to build:

unsetenv VERILATOR_ROOT # For csh; ignore error if on bash

unset VERILATOR_ROOT # For bash

cd verilator

git pull # Make sure git repository is up-to-date

git tag # See what versions exist

#git checkout master # Use development branch (e.g. recent bug fixes)

#git checkout stable # Use most recent stable release

#git checkout v{version} # Switch to specified release version

autoconf # Create ./configure script

./configure # Configure and create Makefile

make -j `nproc` # Build Verilator itself (if error, try just 'make')

sudo make install3-3 Fusesoc安装

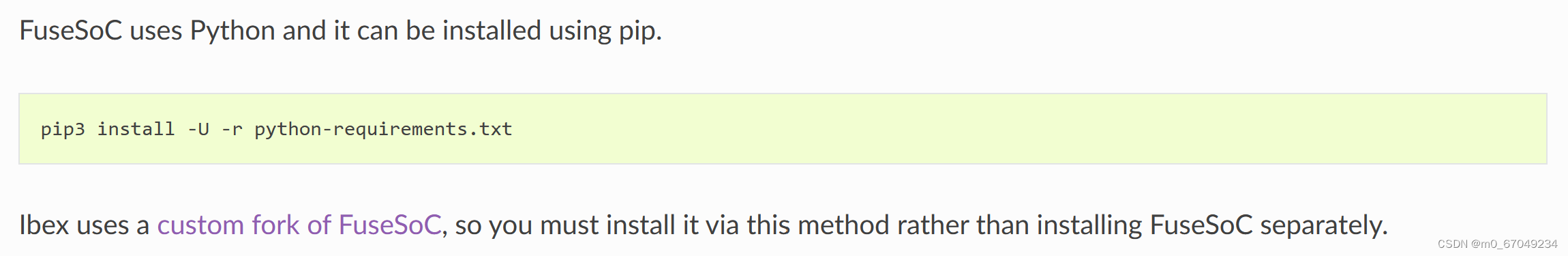

Fusesoc是一个数字硬件(Verilog或VHDL)的生成系统,并能够对硬件设计中可复用模块进行管理。Fusesoc也可通过Git来下载安装,但是Ibex却不推荐这种方法,文档中有如下说明:

在python-requiredments.txt中还包含了可以通过pip来安装的相关库依赖,查看该txt文档中fusesoc的git路径也可以发现并不是指向官方的github路径。在/path/to/ibex/路径下执行上述指令后,通过fusesoc --version发现版本为0.1,官方路径上已找不到该版本。

3-4 riscv-gnu-toolchain安装

在Ibex项目仿真都是基于C代码的仿真,因此需要将写有指令的C代码编译成可执行的二进制文件,这里就需要用到risc-v编译工具链。安装方式有两种,一种是通过Git从官方路径来下载安装riscv-gnu-toolchain,这种方式虽然提高了自由度但是非常耗时,且在后续仿真过程会存在兼容性问题需要对代码进行修改。因此这里推荐第二种方式,即直接使用lowRISC提供的已预生成好的编译器,下载路径:Releases · lowRISC/lowrisc-toolchains (github.com),不存在兼容性问题。

下载路径下每个文件夹都包含了四种版本的编译器,目前Ibex只需要其中32bits版本的即可。

# Download from latest folder

# For example

wget https://github.com/lowRISC/lowrisc-toolchains/releases/download/20230811-1/lowrisc-toolchain-gcc-rv32imcb-20230811-1.tar.xz

cd /path/to/lowrisc-toolchain-gcc-rv32imcb-20230811-1.tar.xz

xz -d lowrisc-toolchain-gcc-rv32imcb-20230811-1.tar.xz

tar -xvf lowrisc-toolchain-gcc-rv32imcb-20230811-1.tar

# Add path

export RISC_TOOLCHAIN=/path/to/lowrisc-toolchain-gcc-rv32imcb-20230811-1

export PATH=$PATH:$RISC_TOOLCHAIN/bin通过which查看路径是否添加正确。

which riscv32-unknown-elf-gcc3-5 GTKwave安装

GTKwave是一款开源工具,用于查看仿真波形,安装也很简单。

sudo apt-get install gtkwave四、Simple system例程

Simple system是官方提供的一个类似于hello world的测试案例,可以用于检查上述软件是否安装正确,也可以帮助大家熟悉Ibex的仿真流程。

4-1 插件安装

首先安装两个运行过程中用到的小插件:

sudo apt-get install libelf-dev

sudo apt-get install srecord4-2 仿真运行

仿真流程的脚本如下:

# Build simulation

fusesoc --cores-root=. run --target=sim --setup --build lowrisc:ibex:ibex_simple_system --RV32E=0 --RV32M=ibex_pkg::RV32MFast

# Build software

make -C examples/sw/simple_system/hello_test

# Run simulator

./build/lowrisc_ibex_ibex_simple_system_0/sim-verilator/Vibex_simple_system -t --meminit=ram,examples/sw/simple_system/hello_test/hello_test.elf- 第一步的主要工作是根据配置来生成对应的rtl代码和仿真环境,运行完成后会在ibex目录下生成一个build/lowrisc_ibex_ibex_simple_system_0文件夹,里面包含了rtl和sim-verilator两个文件夹。

- 第二步的主要工作是调用riscv32-unknown-elf-gcc对hello_test下的hello_test.c进行编译,会在该文件夹下生成hello_test.bin,hello_test.elf等文件,之前安装的srecord插件会将hello_test.elf文件转换成hello_tests.vmem。

- 第三步则是调起Verilator进行仿真并打印报告生成波形,-t用于生成波形,可使用GTKwave查看,elf文件也替换成vmem文件,运行结果相同。

4-3 仿真结果

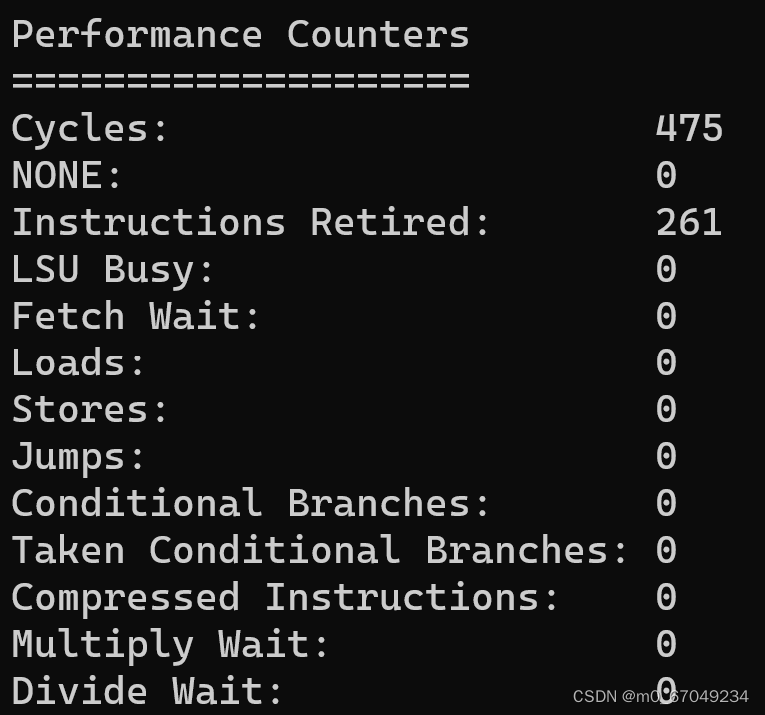

运行以上脚本得到结果如下:

这个结果和官方文档里给出的结果并不一致,但是也没有报错。不用担心,这是由于Performance Counters没有打开的原因,在第一步中加入--MHPMCounterNum=20(默认值为0)

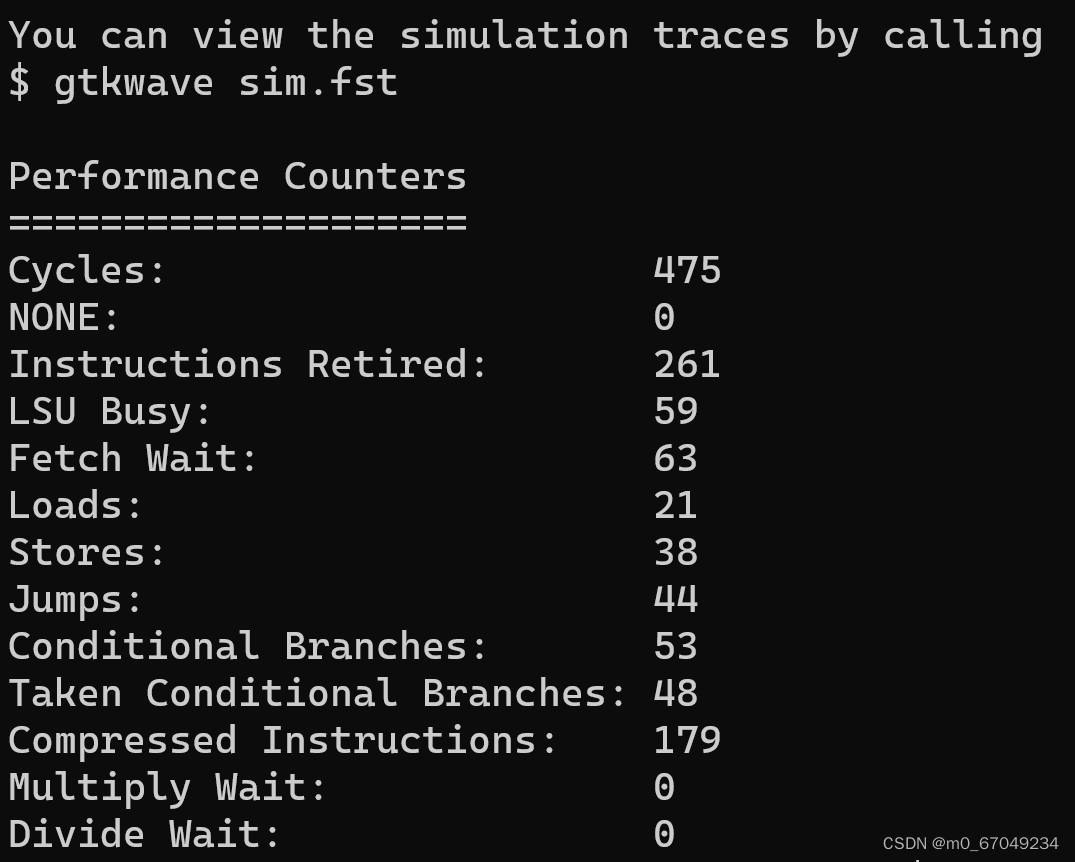

fusesoc --cores-root=. run --target=sim --setup --build lowrisc:ibex:ibex_simple_system --RV32E=0 --RV32M=ibex_pkg::RV32MFast --MHPMCounterNum=20重新运行整个流程,即可得到如下结果

根据提示运行以下指令即可条用GTKwave查看波形:

gtkwave sim.fst在ibex目录下ibex_simple_system.log可查看仿真打印的信息。

五、Coremark仿真

5-1 cosim仿真环境

Ibex可以与调用商用EDA工具进行UVM验证,以下是所需要的Spike插件的安装过程:

# Get the Ibex co-simulation spike branch

git clone -b ibex_cosim https://github.com/lowRISC/riscv-isa-sim.git riscv-isa-sim-cosim

# Setup build directory

cd riscv-isa-sim-cosim

mkdir build

cd build

# Configure and build spike

../configure --enable-commitlog --enable-misaligned --prefix=/opt/spike-cosim

sudo make -j8 install安装完成后需要配置以下环境变量,其中RISCV-TOOLCHAIN变量已经3-4中设置过。

export RISCV_GCC="$RISCV_TOOLCHAIN/bin/riscv32-unknown-elf-gcc"

export RISCV_OBJCOPY="$RISCV_TOOLCHAIN/bin/riscv32-unknown-elf-objcopy"

export SPIKE_PATH=/path/to/spike/bin

export PKG_CONFIG_PATH=$PKG_CONFIG_PATH:/path/to/spike/lib/pkgconfig5-2 仿真运行

根据之前的经验,在build simulator阶段加入--MHPMCounterNum=20,以下脚本在ibex目录下运行。

# Build simulator

fusesoc --cores-root=. run --target=sim --setup --build lowrisc:ibex:ibex_simple_system_cosim --RV32E=0 --RV32M=ibex_pkg::RV32MFast --MHPMCounterNum=20

# Build coremark test binary, with performance counter dump disabled. The

# co-simulator system doesn't produce matching performance counters in spike so

# any read of those CSRs results in a mismatch and a failure.

make -C ./examples/sw/benchmarks/coremark SUPPRESS_PCOUNT_DUMP=1

# Run coremark binary with co-simulation checking

build/lowrisc_ibex_ibex_simple_system_cosim_0/sim-verilator/Vibex_simple_system --meminit=ram,examples/sw/benchmarks/coremark/coremark.elf5-3 仿真结果

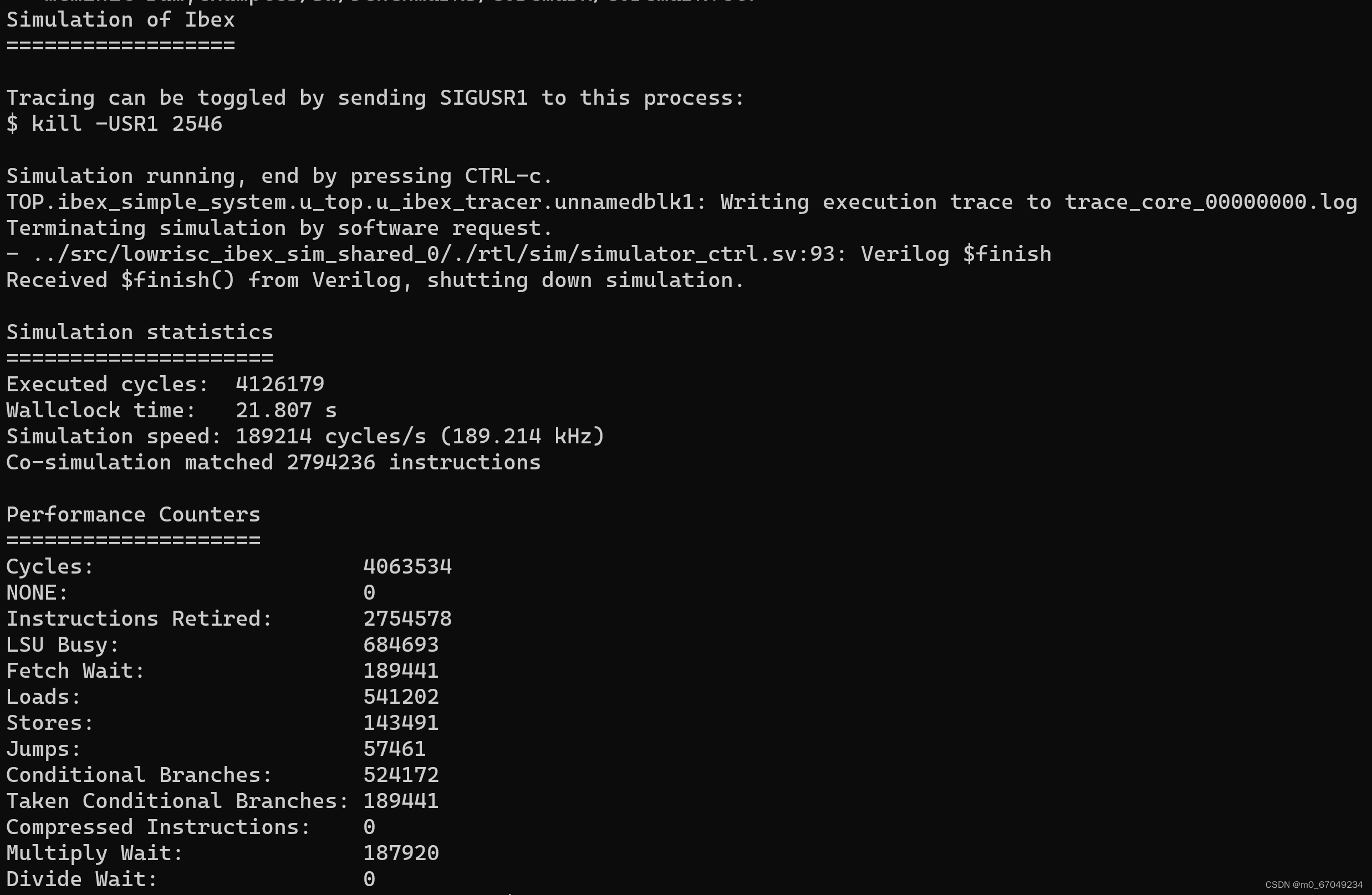

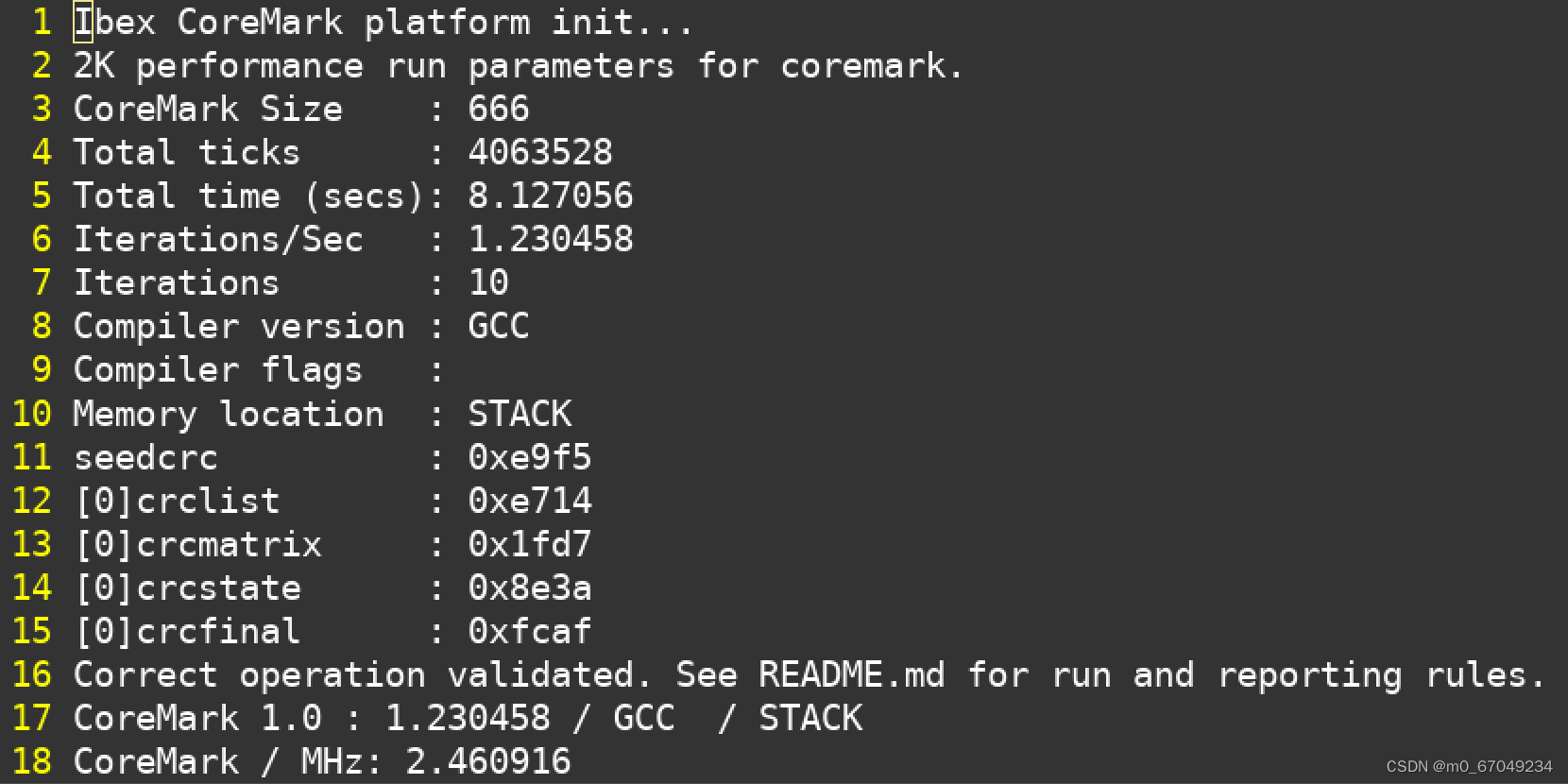

Terminal上将打印出以下报告:

查看ibex_simple_system.log,可以看到CoreMark数值为2.46CoreMark/MHz

有兴趣的读者也可以在仿真运行指令中加上-t查看波形。至此CoreMark测试完成,读者也可以更改ibex core的配置来验证各种参数对CoreMark的影响。

六、部分问题及解决方法

若按照上述流程进行安装配置,不会出现以下问题,可以跳过以下内容。

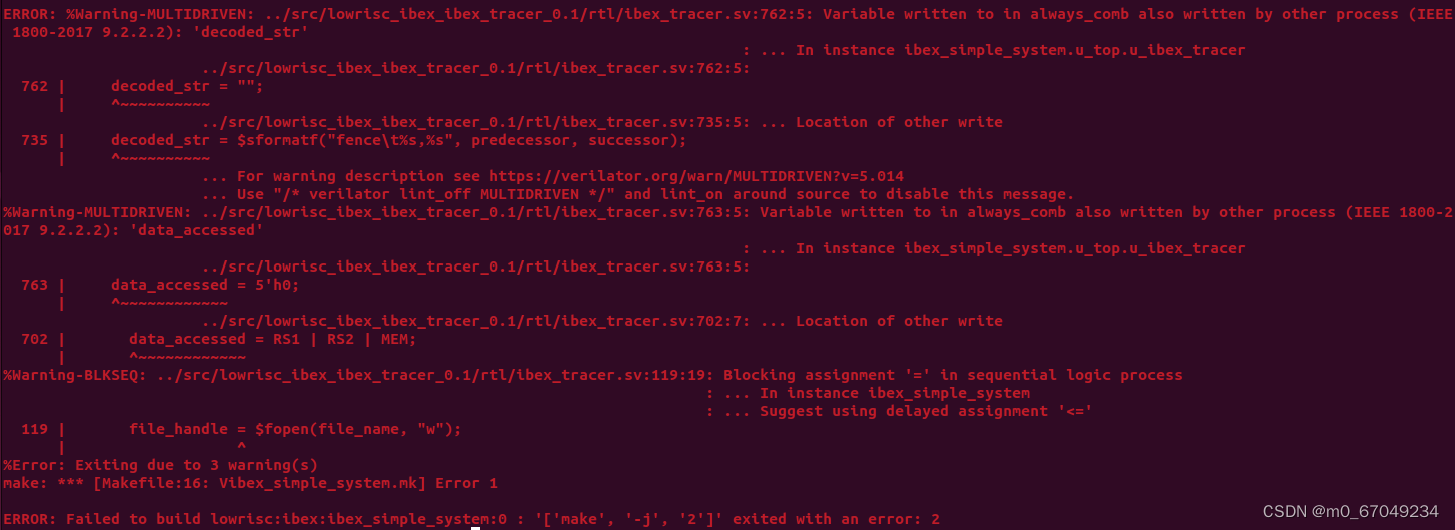

6-1 Verilator最新版本引起的编译报错

正如3-2中所述,当Verilator版本为v5.x时,运行Simple system仿真流程第一步时会出现以下编译问题:

可以看到一共有两种类型的warning,分别是MULTIDRIVEN和BLKSEQ,可以查看Verilator官方文档中的Errors and Warnings章节了解具体原因。在该章节开头也告知了如何关闭warning,因此我ch们可以在/path/to/ibex/vendor/lowrisc_ip/lint/tools/verilator/common.vlt文件加入以下内容:

# lint off MULTIDRIVEN and BLKSEQ warnings due to verilator v5.x version

lint_off -rule MULTIDRIVEN -file "*/ibex_tracer.sv"

lint_off -rule BLKSEQ -file "*/ibec_tracer.sv"重新执行仿真流程,编译通过。

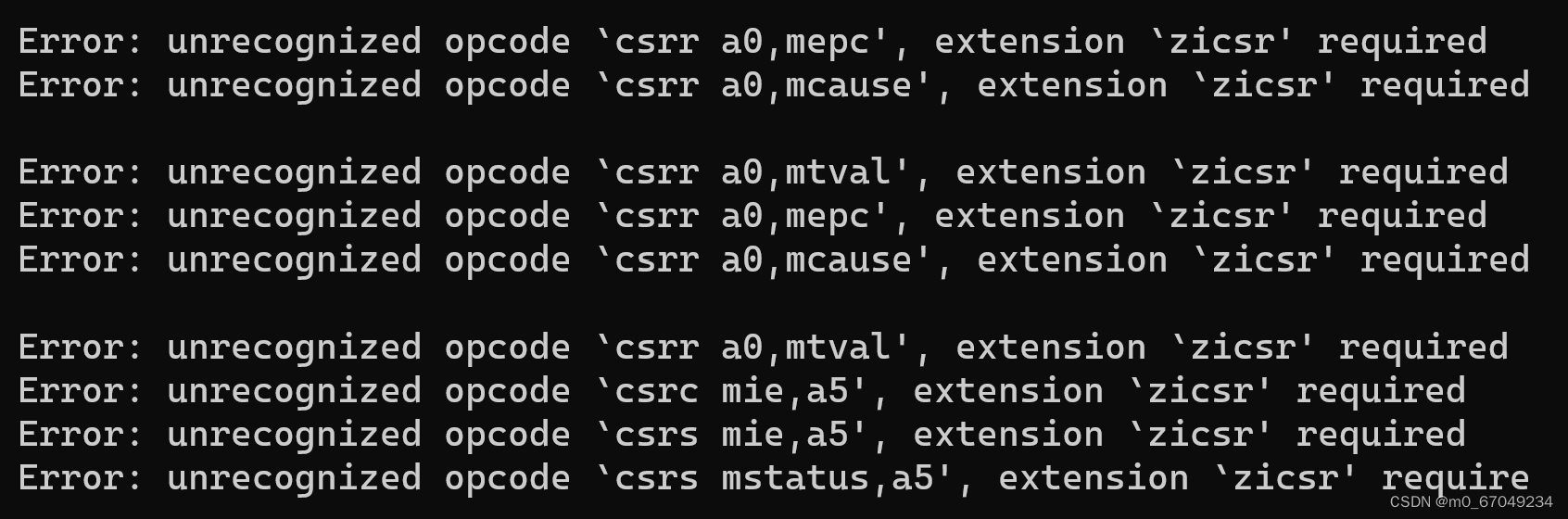

6-2 使用自编译的riscv-gnu-toolchain引起的编译报错

在将C代码编译成可执行的二进制时会调用risc-gnu-toolchain,若使用自己编译生成工具,可能会在该步骤出现问题。以下是我在编译生成工具时运行的指令:

git clone https://github.com/riscv-collab/riscv-gnu-toolchain.git

sudo ./configure --prefix=/opt/riscv --with-arch=rv32imac --with-abi=ilp32

sudo make

export PATH=$PATH:/opt/riscv/bin在使用上述工具对C代码编译时会出现以下报错:

报错提示缺少zicsr扩展指令集。对/path/to/ibex/examples/sw/simple_system/common/common.mk中的第11行进行替换,

ARCH ?=rv32gc替换后重新运行C代码编译,报错消失。

2595

2595

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?