声明:文章转载自微信公众号:模拟版图layout设计(转载请标明出处!)

1. 减少换层的数量

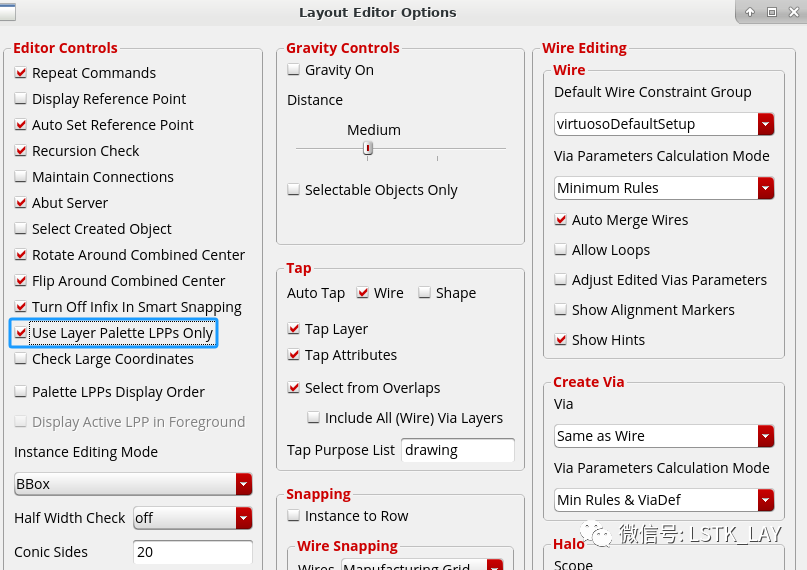

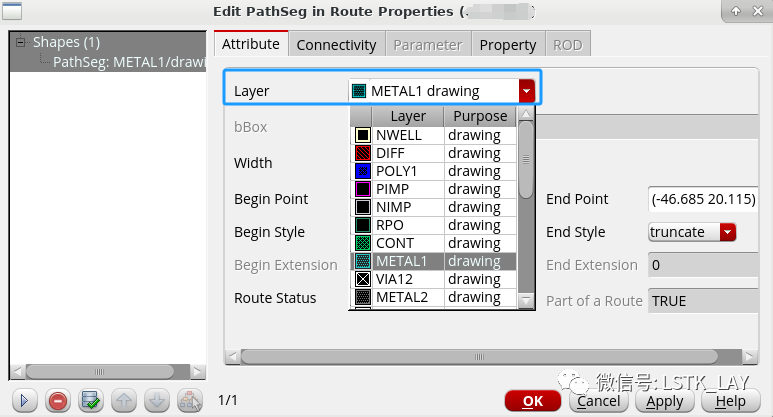

可以看到下图中的层数量只有使用的layer,其他的层将不显示。

2. 删除版图中空白区域

在CIW中运行以下命令即可:

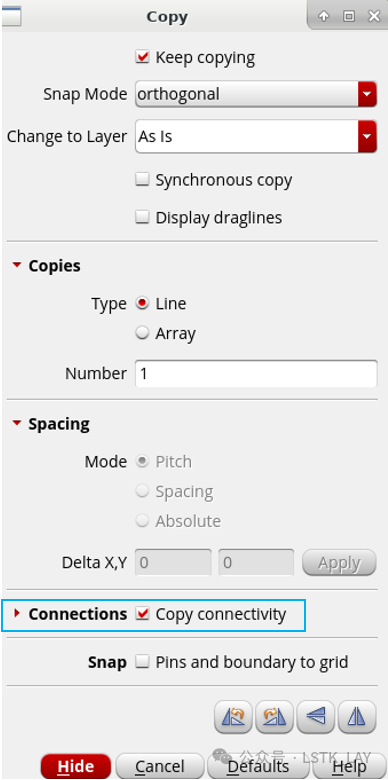

foreach(st geGetEditCellView()~>steiners dbDeleteObject(st))3. copy器件时,保持和原器件相同的连接关系

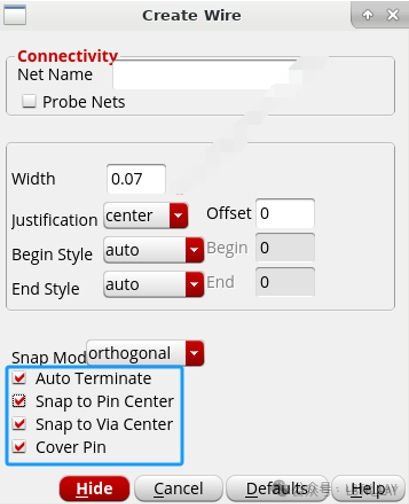

4. Creat Wire中开启自动吸附Pin、Via功能

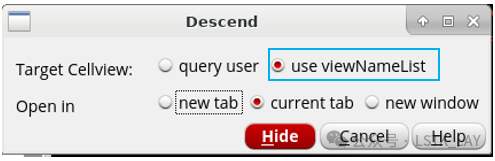

5. 查看层级schematic时直接进入下层,无对话框确认

快捷键e,然后按F3,选择use viewNameList项

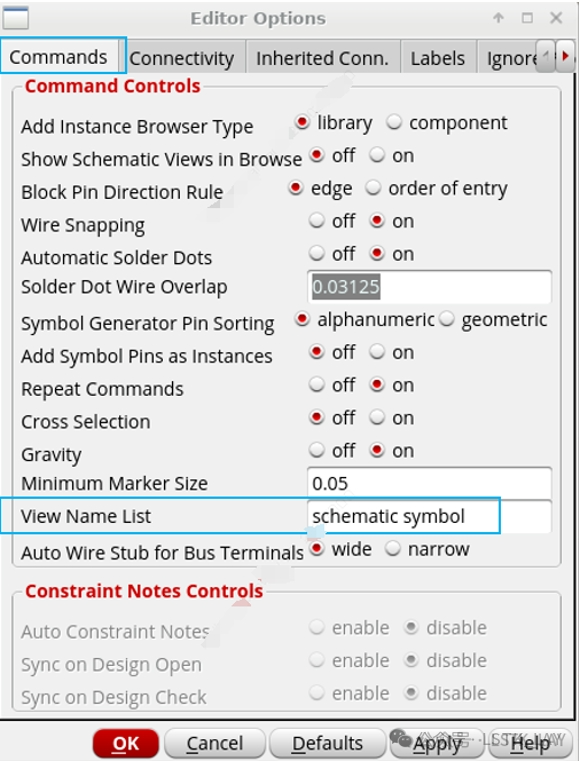

可在菜单栏Options—Editor,Commands栏View Name List指定view的顺序。

相关view类型 :

schematic symbol vhdl functional abstract layout synthesis也可在cdsenv中对应设置为默认项:

schematic descendTarget string "use viewNameList"*以上内容仅供个人学习,切勿用于商业!!!

5627

5627

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?