3.6 并行存储器结构技术

由于CPU和主存所使用的半导体器件工艺不同,两者速度上的差距导致快速的CPU等待慢速的主存储器,为此需要想办法提高主存的速度。

改善主存速度的方法可从3个方面考虑.

(1)提高DRAM芯片本身的速度,如各种基于SDRAM的技术(不在考纲内)。

(2)采用并行结构技术,本节介绍的双口存储器和多模块存储器就是利用时间并行和空间并行性在结构上进行优化的技术。

(3)在CPU和主存之间增加高速缓冲存储器。这是下一节介绍的内容。

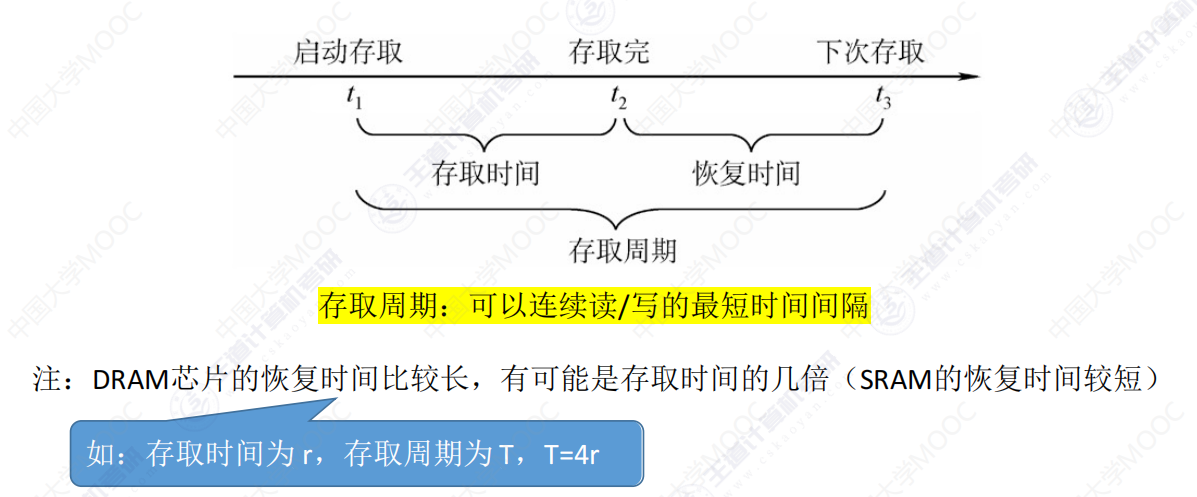

之前讲到了存取周期的概念:存取周期又称读写周期或访问周期,它是指存储器进行一次完整的读写操作所需的全部时间,即连续两次独立访问存储操作(读或写操作)之间所需的最小时间间隔。对于DRAM芯片,它的恢复时间是比较长的,有时有可能会到达存取周期的几倍,而现代计算机CPU通常都是多核的,那么这么多CPU核心究竟应该怎样访问主存才能解决恢复时间过长带来的问题呢?主要有两种思路

- 双端口RAM

- 多模块存储器

3.6.1 双端口RAM(不考)

双端口RAM:是指同一个存储器有左右两个独立的端口

订阅专栏 解锁全文

订阅专栏 解锁全文

3210

3210

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?