-

参考课程:【【第一期】手把手教你学领航者&启明星ZYNQ之FPGA开发篇【真人出镜】FPGA教学视频教程】 https://www.bilibili.com/video/BV1Ec411K791/?p=21&share_source=copy_web&vd_source=dd2f15e557b5c8639050a36f7ae04635

-

FPGA初体验——点亮LED灯

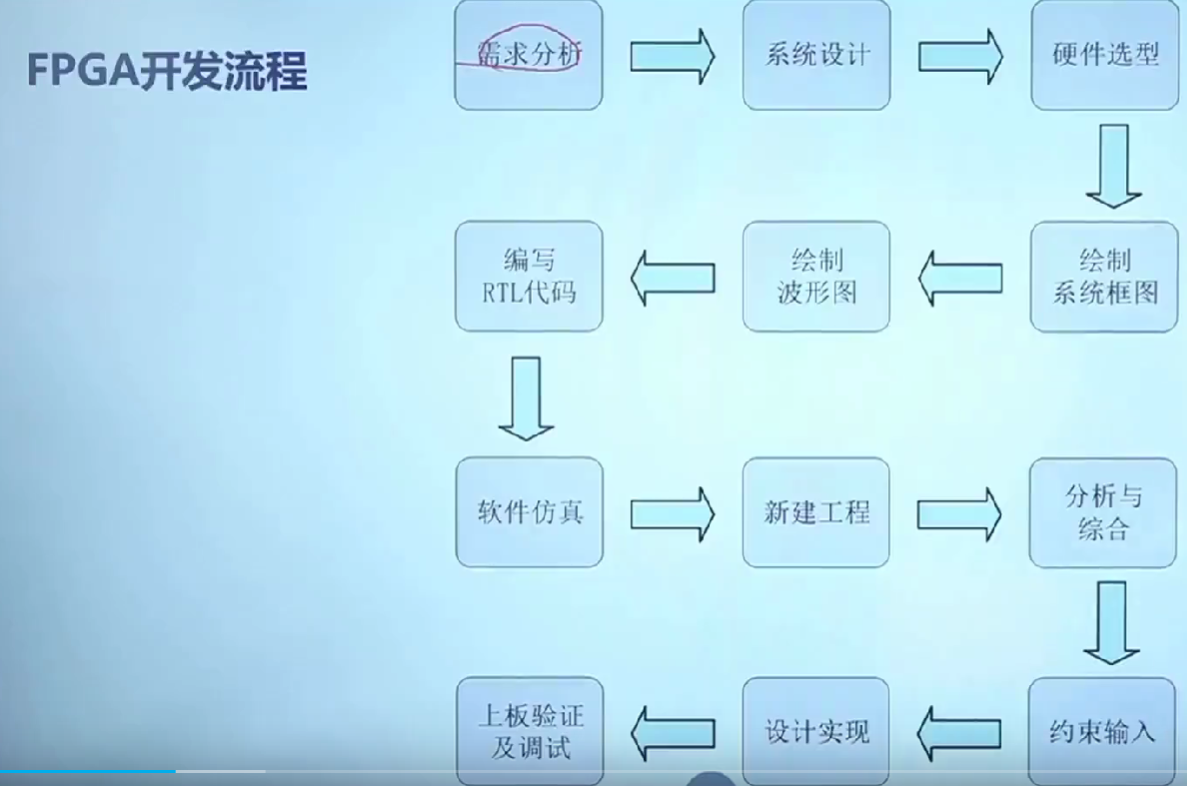

- 开发流程

-

第一步:需求分析

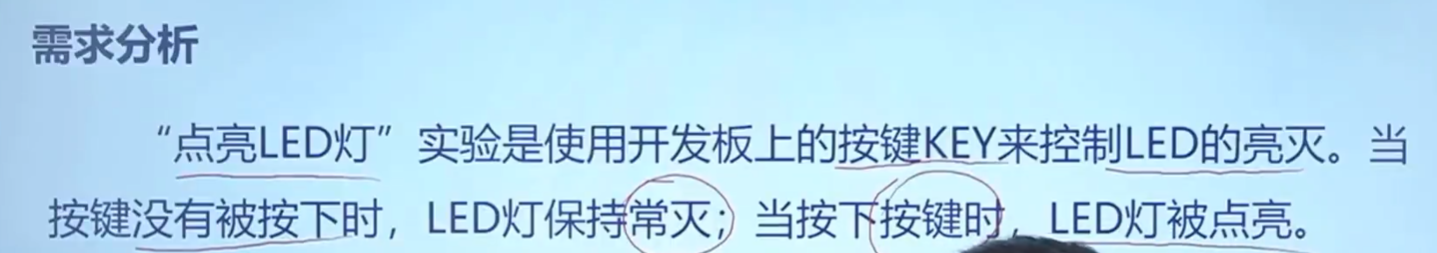

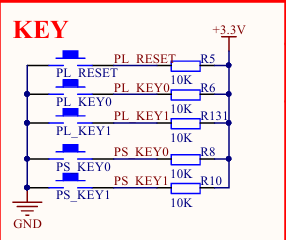

- 由KEY原理图可知,按键未按下时,为高电平;按下以后为低电平。

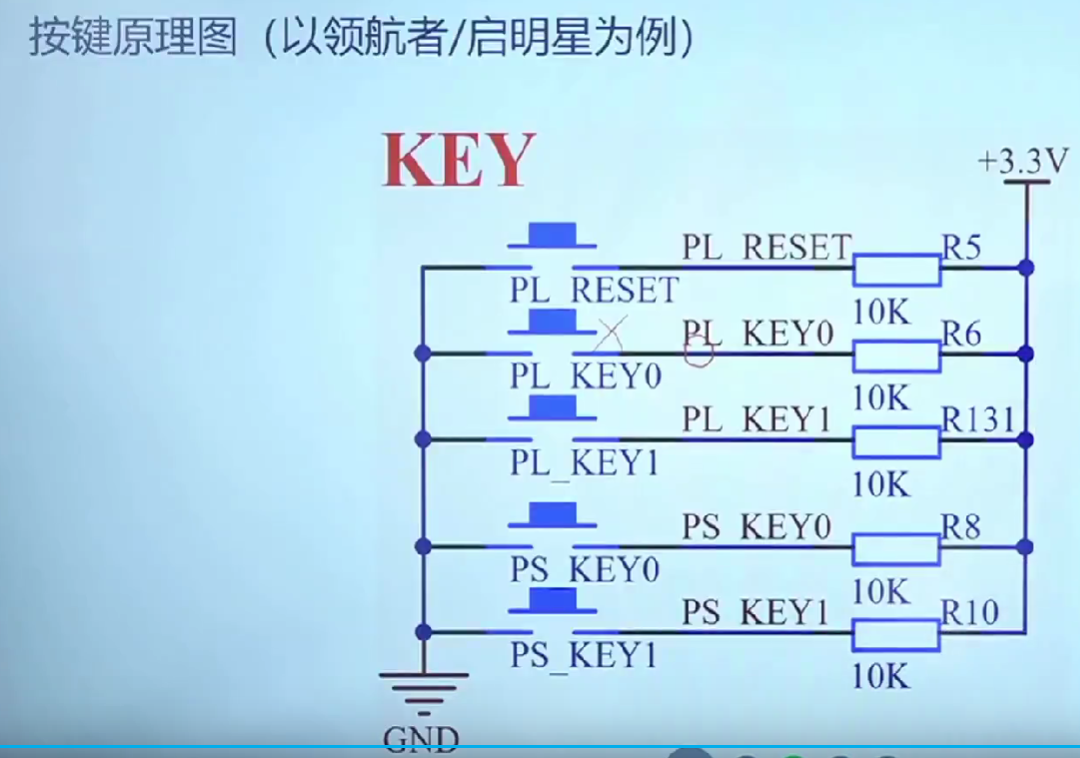

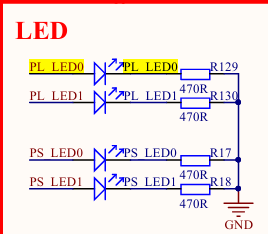

- 由LED原理图知,当PL连接处为高电平1时,led灯可以被点亮(因为高电平和GND构成了一条通路)

-

-

工程创建

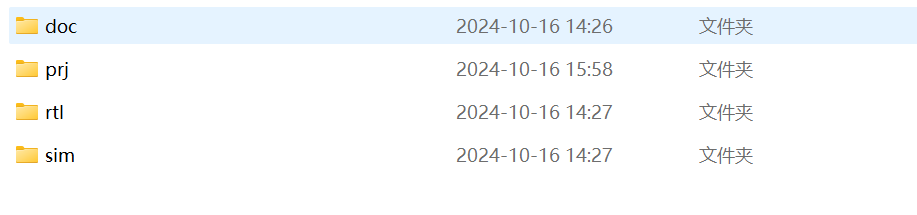

- ①可以先自己建好文件夹,然后在里面新建四个文件夹,这样时为了以后便于管理各种类型的文件。

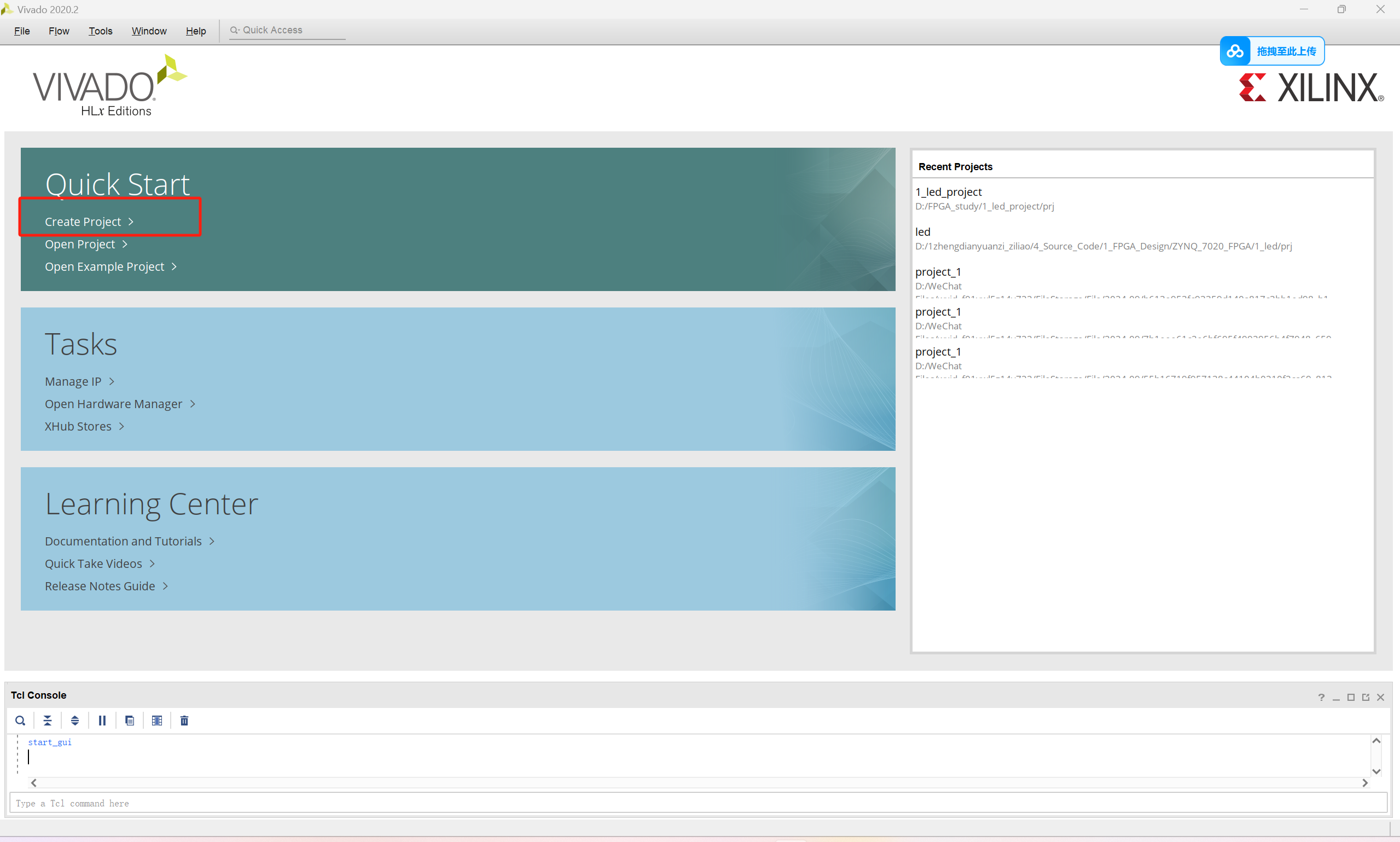

- ②打开vivado,新建工程,后续进行工程命名。

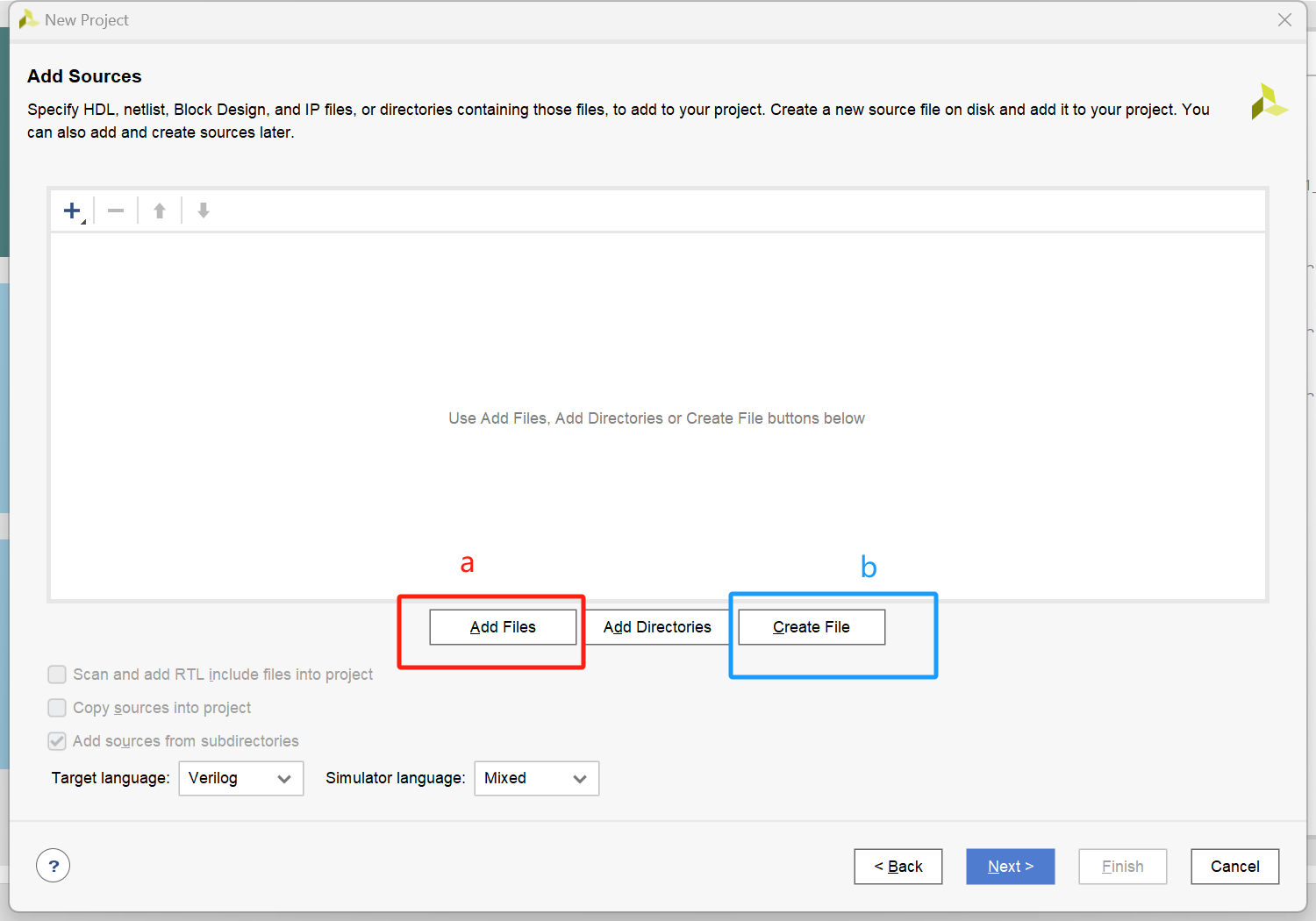

- ③在添加源文件这一步,如果有提前编写好的代码,则点a进行选择,需要一会编写的,则点b。

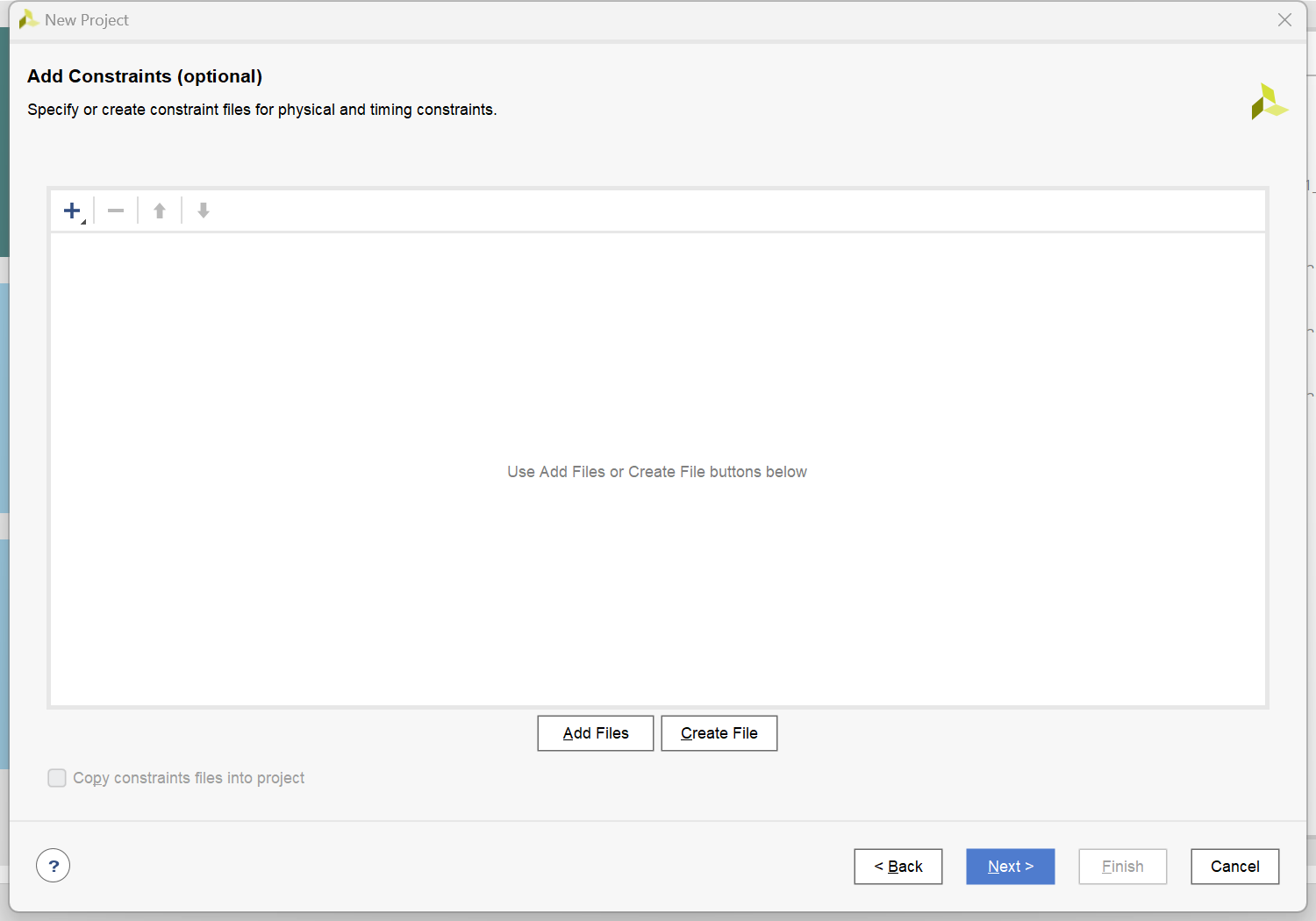

- ④添加约束:这一步同③

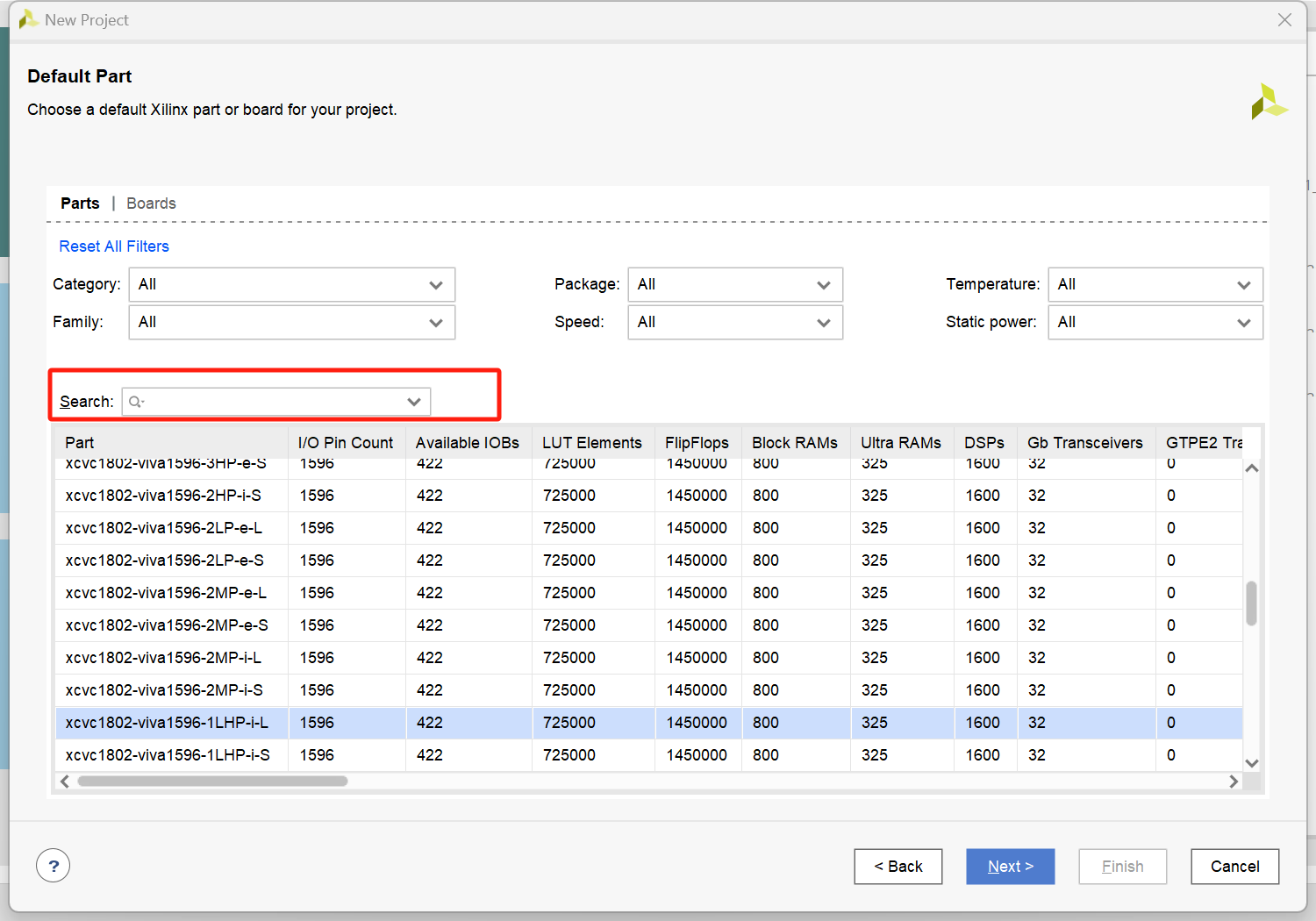

- ⑤添加器件类型:在红框处输入芯片型号,例如我使用的是XC7Z020CLG400-2.

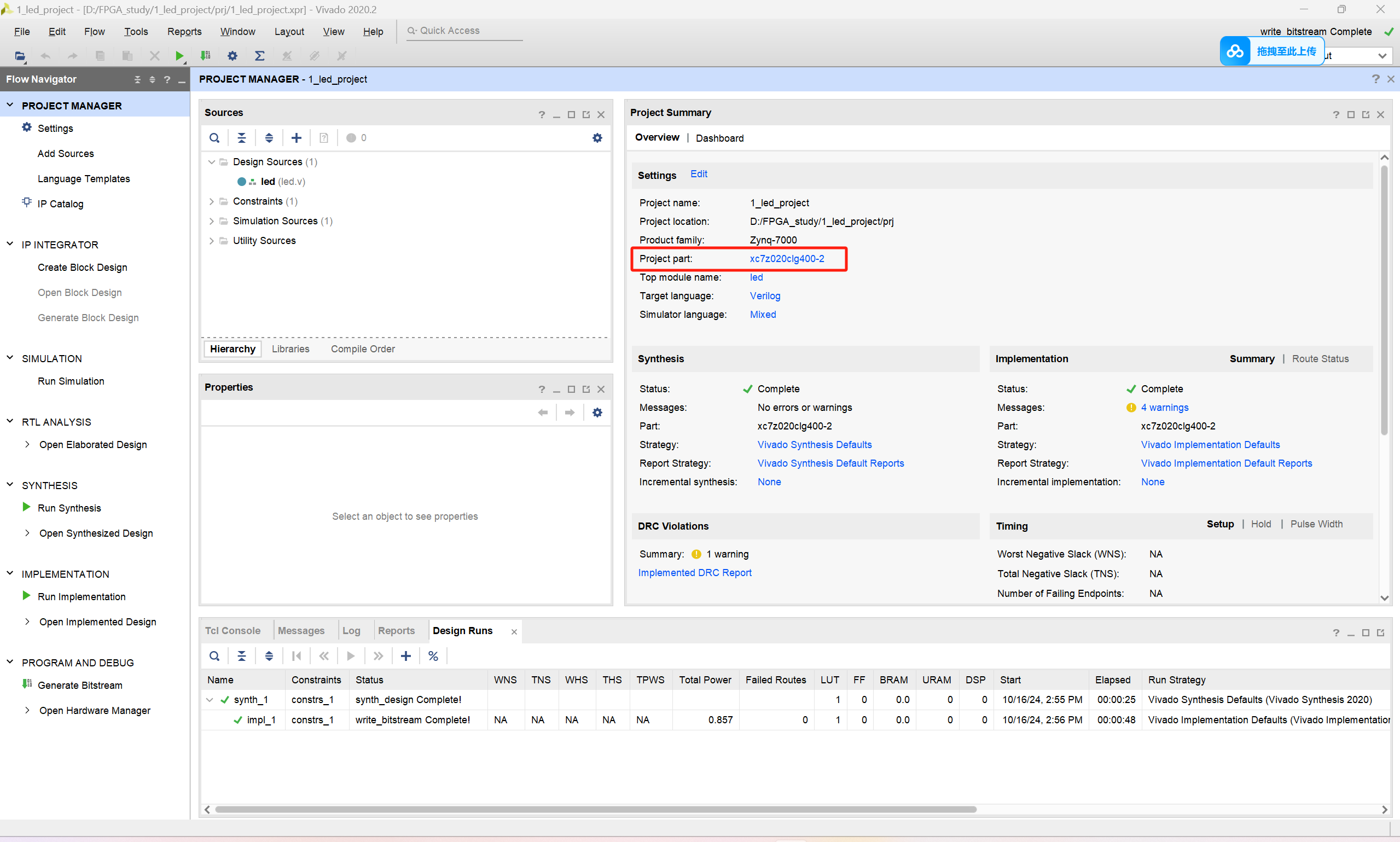

- ⑥确认界面:在该界面仔细检查所选的器件型号还有其他信息,确认无误后点finish。

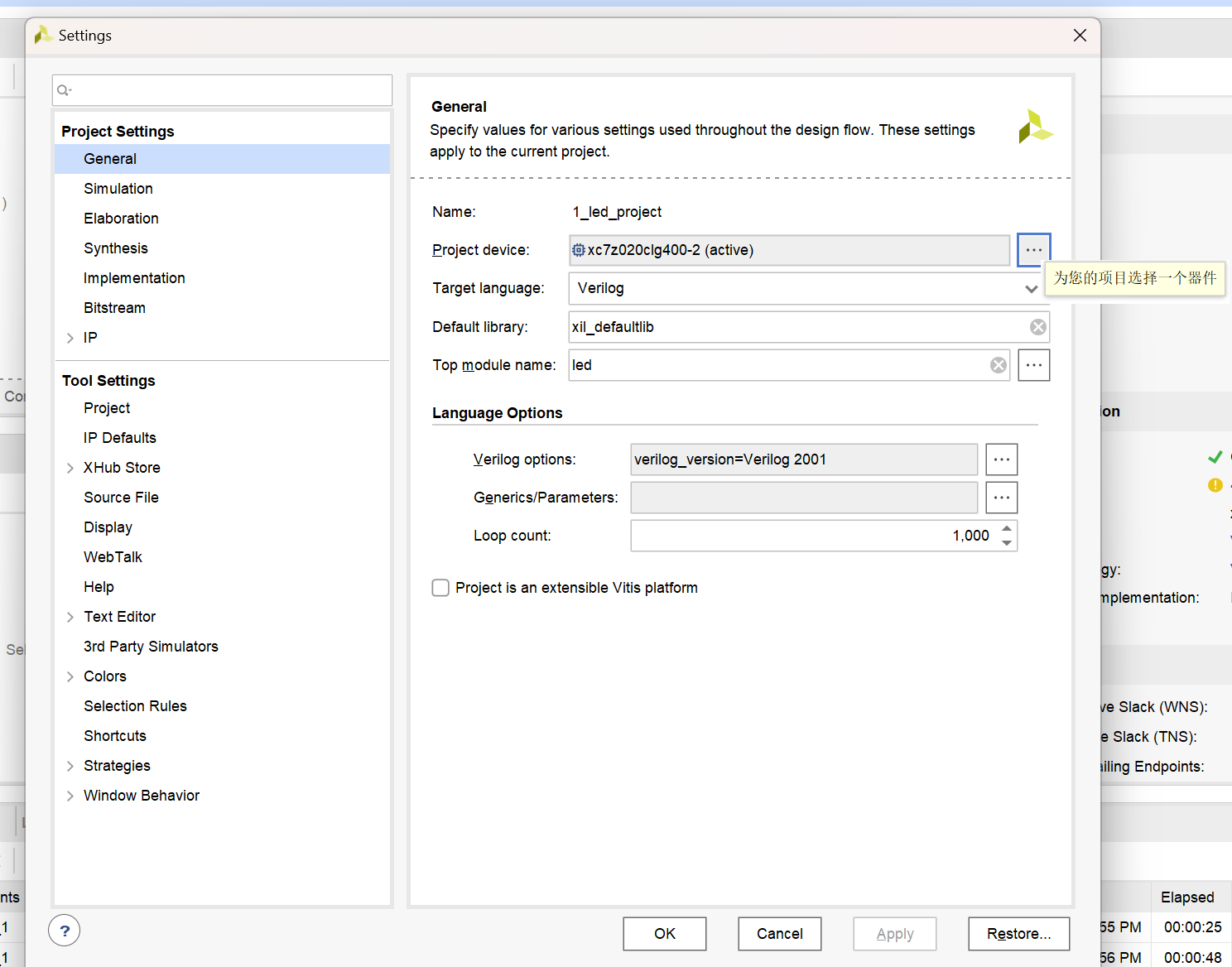

- ⑦工程创建好了以后,在主界面可以看到工程的相关信息,如果此时发现器件型号选错了,可以点击红框处器件型号,然后点击第二张图片的三个点处,进行器件更换。

- ①可以先自己建好文件夹,然后在里面新建四个文件夹,这样时为了以后便于管理各种类型的文件。

-

代码编写

- ①看原理图:查看led灯在什么情况下(高电平or低电平)可以被点亮。这里可以看到LED的一端接地,所以另一端是高电平1时可以将LED灯点亮。

- 从按键的原理图可以看出,当按键按下时,PL端为低电平,和3.3V的高电平可以构成一个通路,即:电路接通。

- 知道以上内容以后,就可以进行Verilog代码的编写。

- 从按键的原理图可以看出,当按键按下时,PL端为低电平,和3.3V的高电平可以构成一个通路,即:电路接通。

- ②写代码:

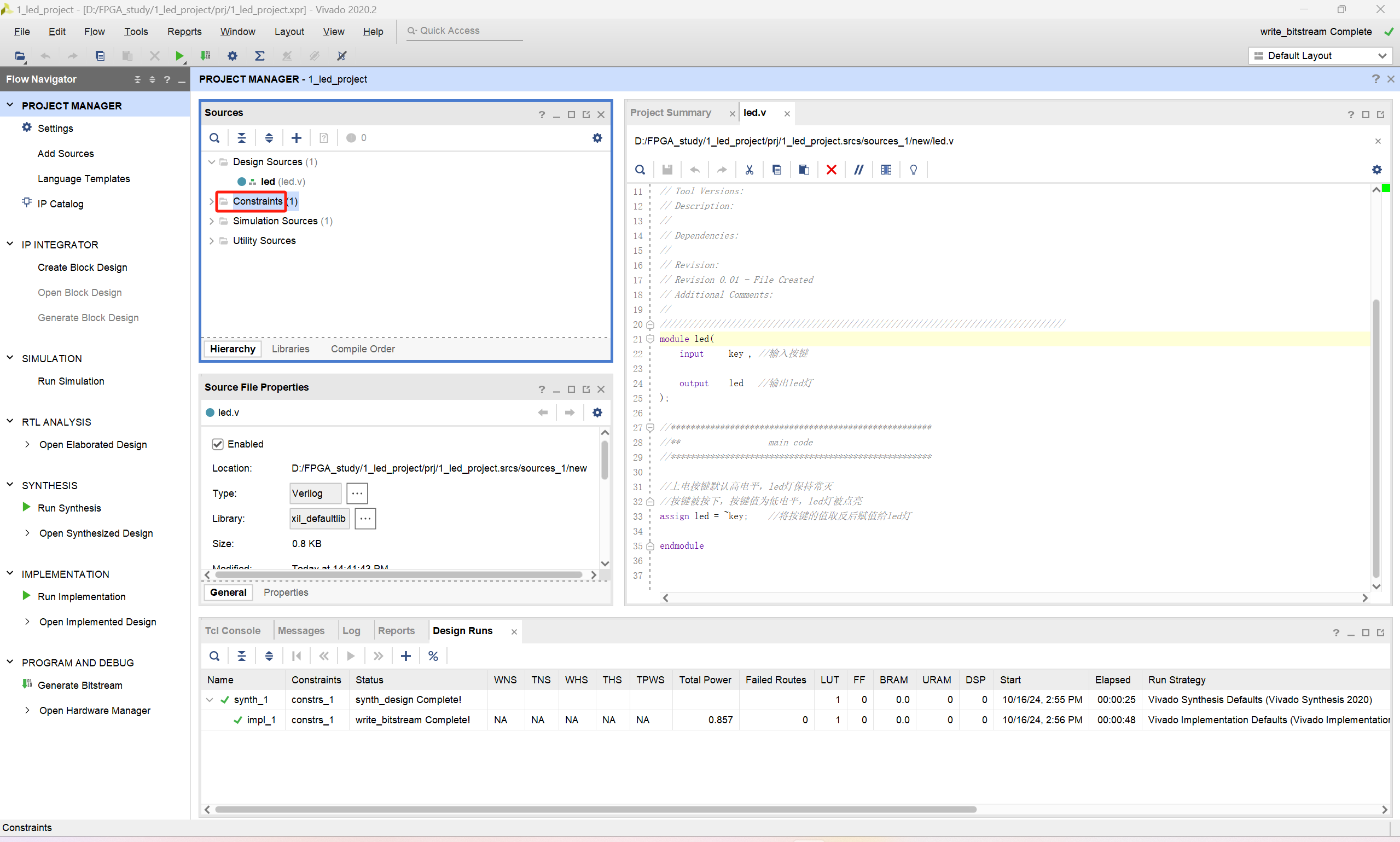

- led.v文件:确定输入输出,因为是按下按键,灯亮,所以按键是作为输入,灯是输出。由原理图的分析,可以看出按键是低电平、灯是高电平时,led被点亮,即:led和按键的高低电平在同一时刻刚好相反,所以将按键的值取反后赋值给led灯。

-

module led( input key , //输入按键 output led //输出led灯 ); //***************************************************** //** main code //***************************************************** //上电按键默认高电平,led灯保持常灭 //按键被按下,按键值为低电平,led灯被点亮 assign led = ~key; //将按键的值取反后赋值给led灯 endmodule

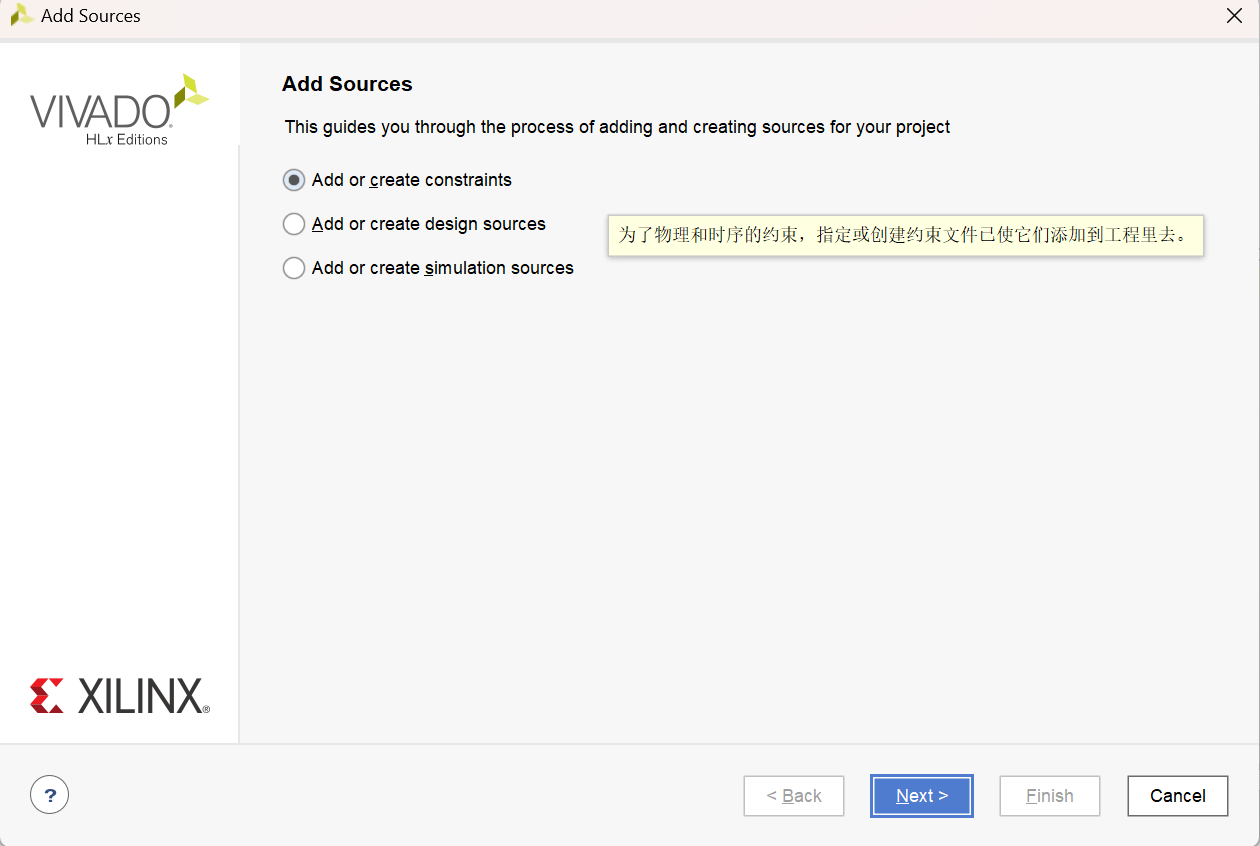

- 约束文件:下面要进行管脚约束,我们右击constraints,然后点add sources,再选择第一个add or create constraints,点next。

- 添加约束文件,有两种常用的方法,一是通过查看原理图,然后自己手动添加管脚约束,二是直接从正点原子(一般买开发板以后,商家给的资料包里有写好的约束代码)给的约束代码里copy。

- 第一种方法

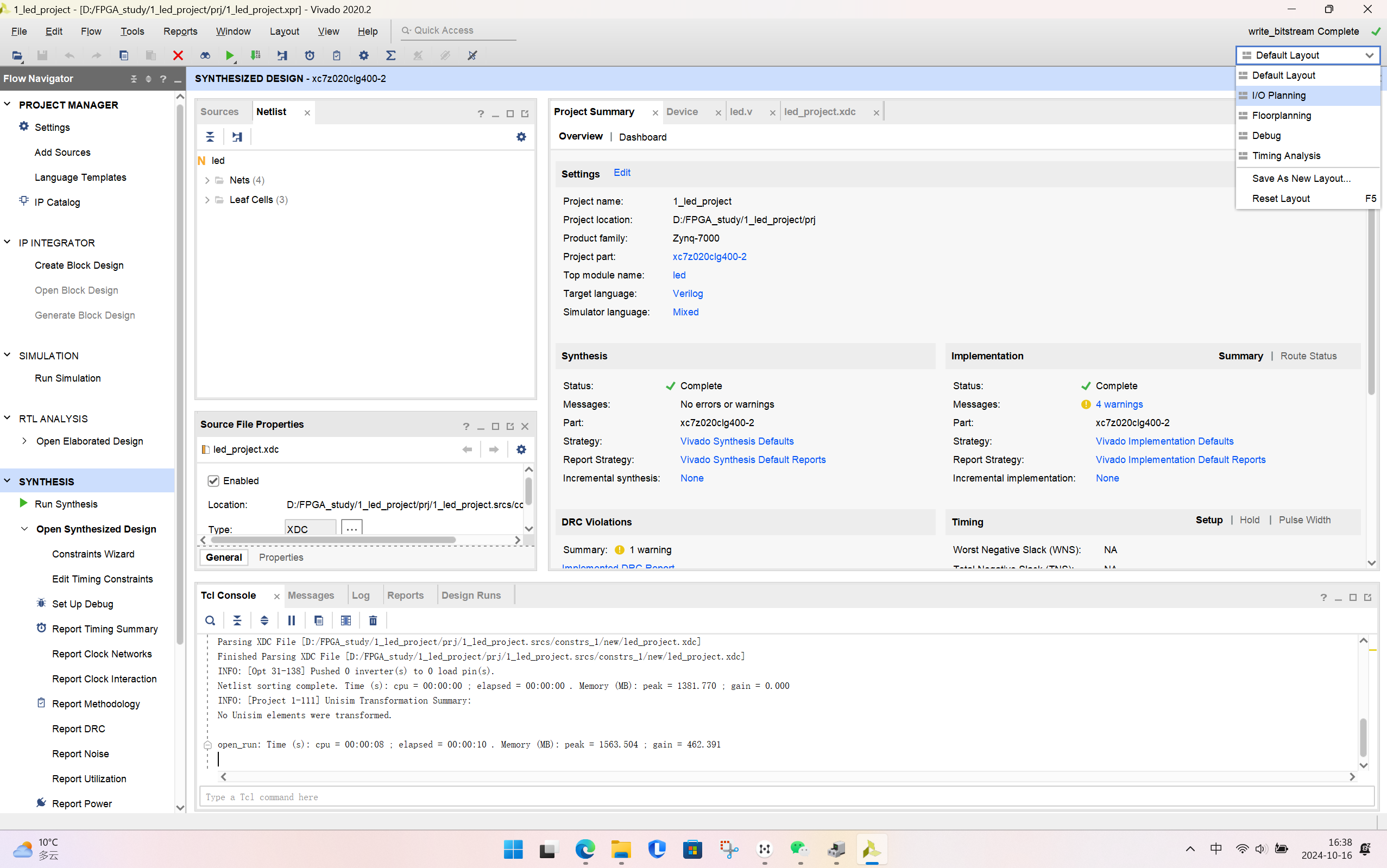

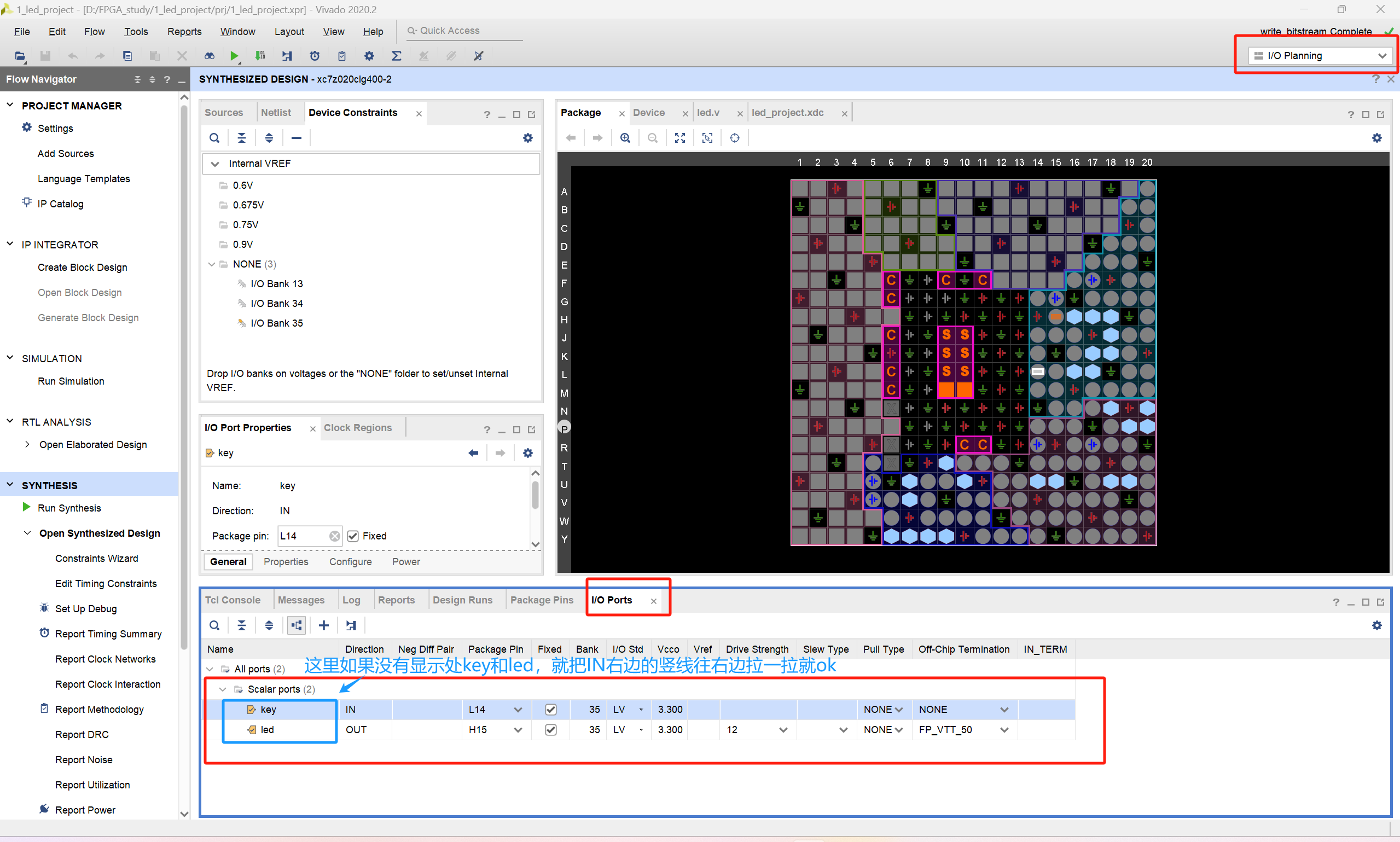

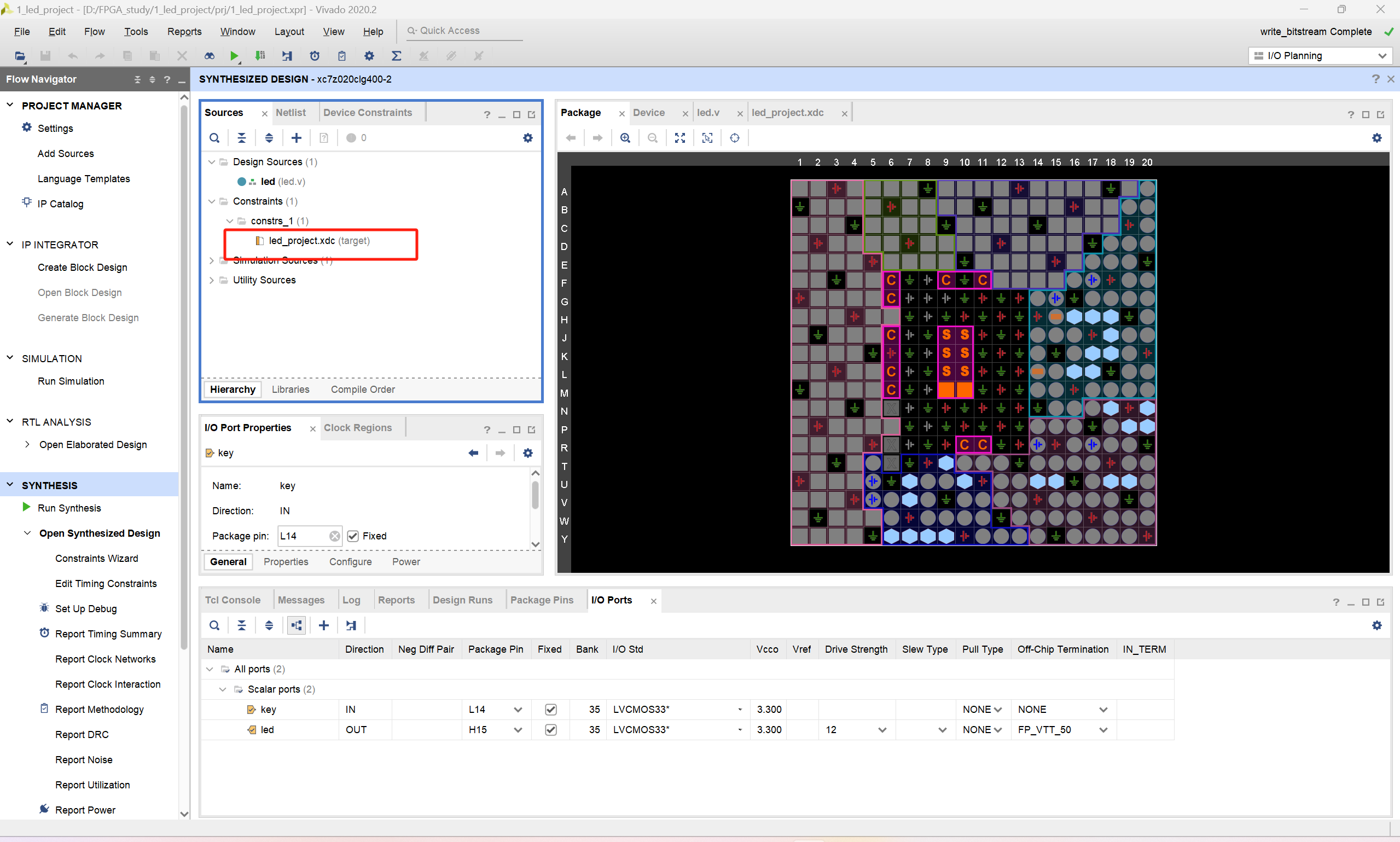

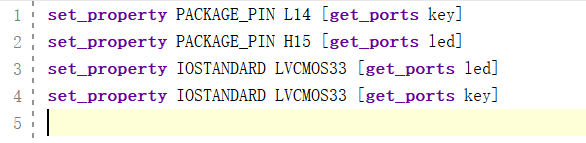

- 我们点击右上角的IO planning (如果你是已经建好一个约束文件,并且已经SYNTHESIS过了,那么就先点击Open Synthesized Design,然后右上角就会出现IO planning了,此时再点击IO planning就好。)

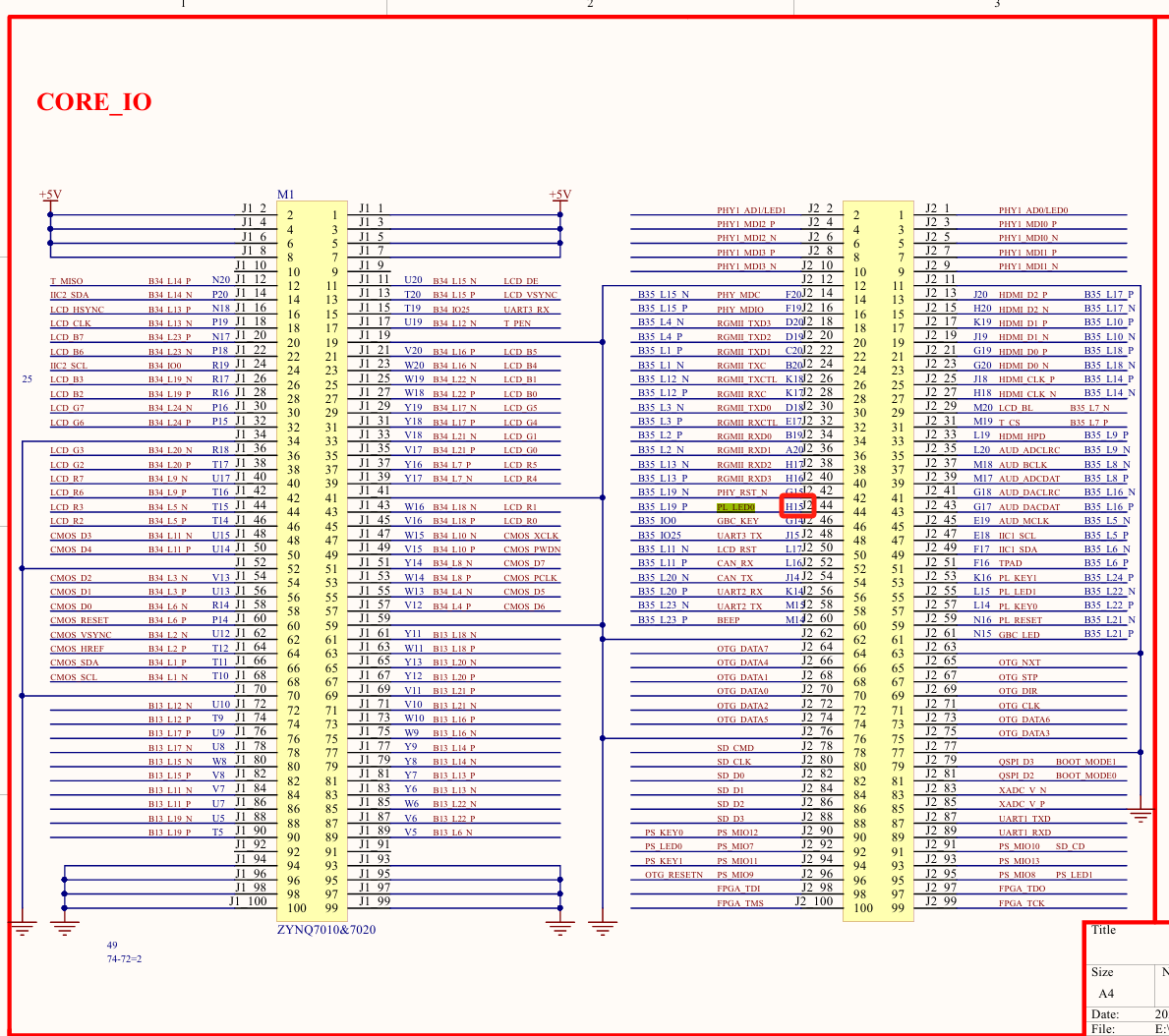

- 在这里要看原理图来选择管脚,L14和H15是我通过看原理图选出来的,不同板卡的原理图不同,这个需要自己学一下怎么看。我是这么做的:此次,我需要点亮LED0,所以在原理图上找到PL LED在核心板上对应的管脚(蓝色是提前标注好的核心板上的管脚),从CORE_IO中可以看出是H15,按键同理。

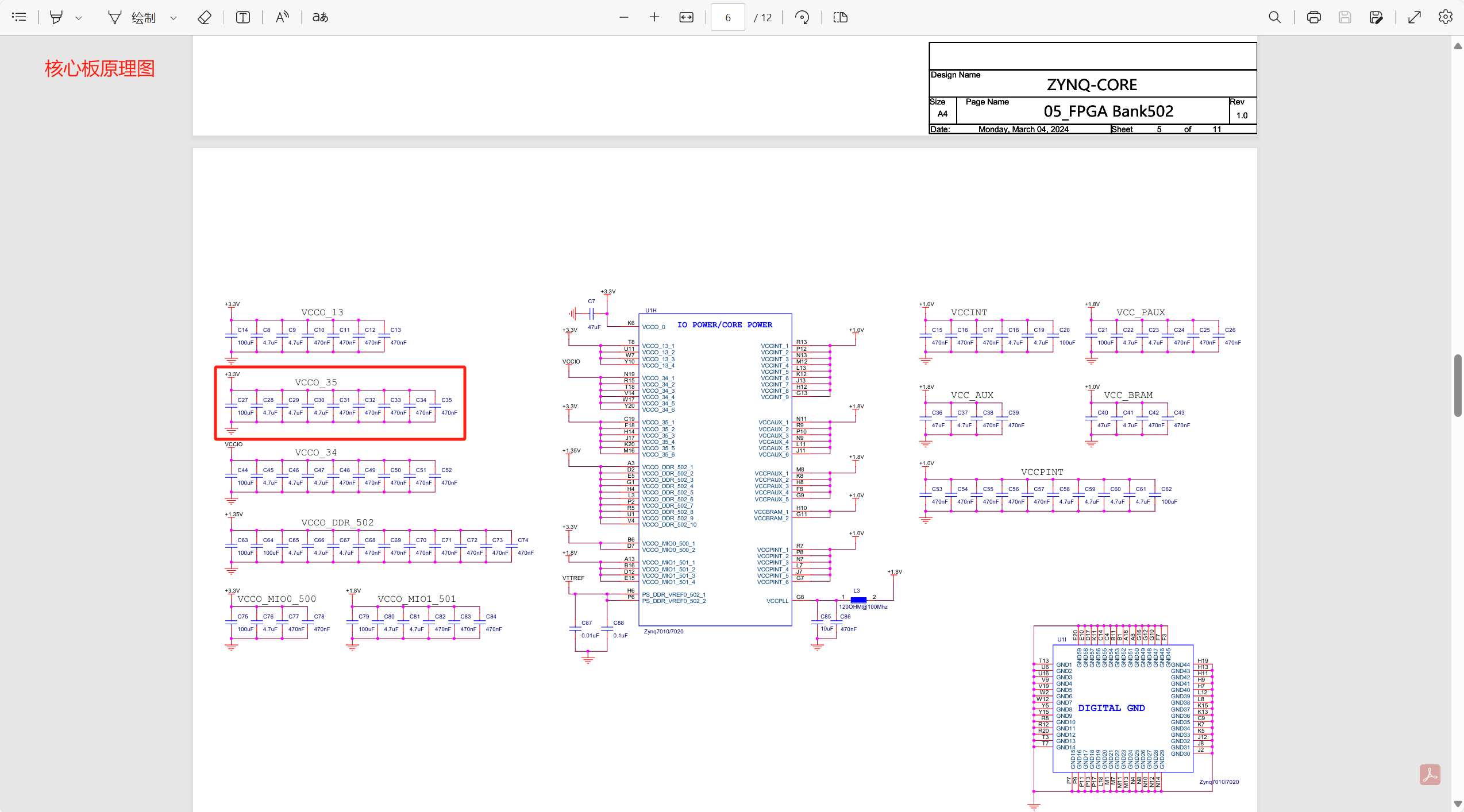

- 然后选Bank电压,也就是IO std这里,当输入完管脚以后,就会在管脚名称后面显示出所属的Bank,比如这里我们就要到核心板上去查找Bank35对应的bank电压,从核心板原理图上可以看出是3.3V,所以选择LVCMS33*。

- 设定完成后,点ctrl+s进行保存,然后单击红框处,即可查看约束代码。

- 我们点击右上角的IO planning (如果你是已经建好一个约束文件,并且已经SYNTHESIS过了,那么就先点击Open Synthesized Design,然后右上角就会出现IO planning了,此时再点击IO planning就好。)

- 第二种方法

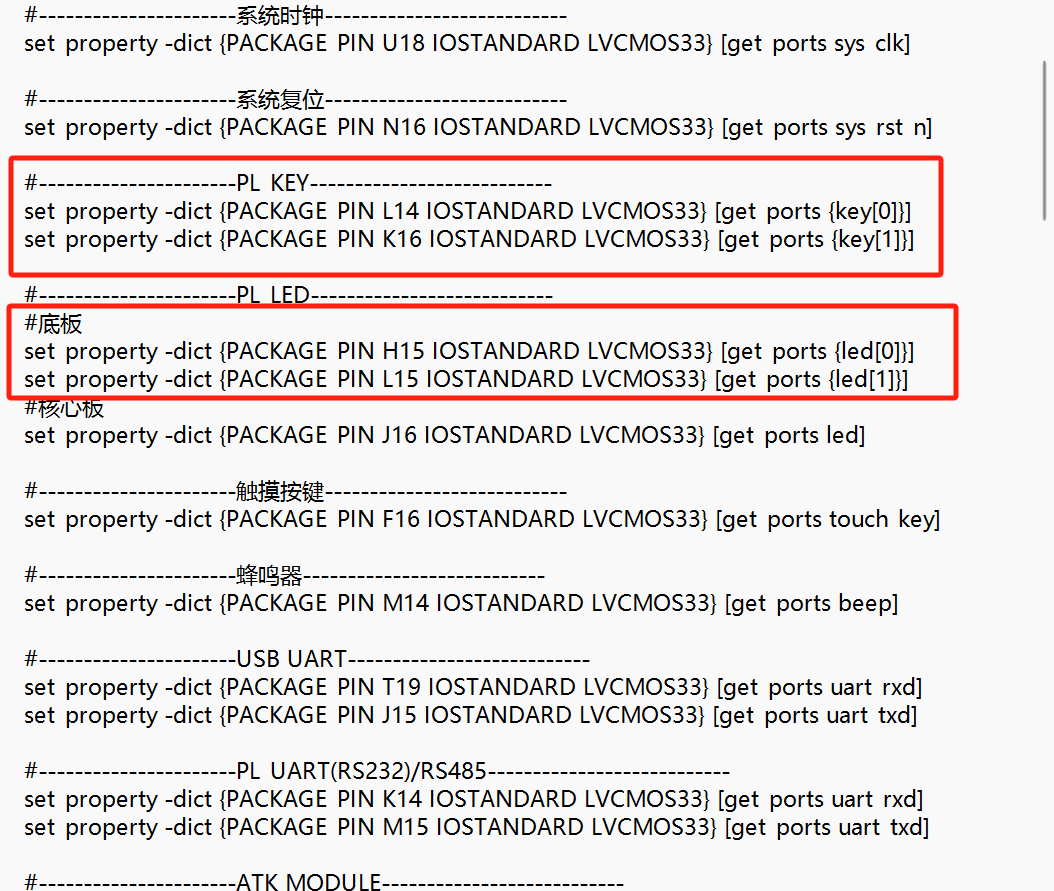

- 点开商家提供的xdc文件,在里面挑选要用的约束代码。

- 注意这个不是无脑照搬,copy以后,要根据自己之前写的led.v文件里的输入输出名称进行更改,比如这里要把LED0改成led。

- 点开商家提供的xdc文件,在里面挑选要用的约束代码。

- 第一种方法

- 添加约束文件,有两种常用的方法,一是通过查看原理图,然后自己手动添加管脚约束,二是直接从正点原子(一般买开发板以后,商家给的资料包里有写好的约束代码)给的约束代码里copy。

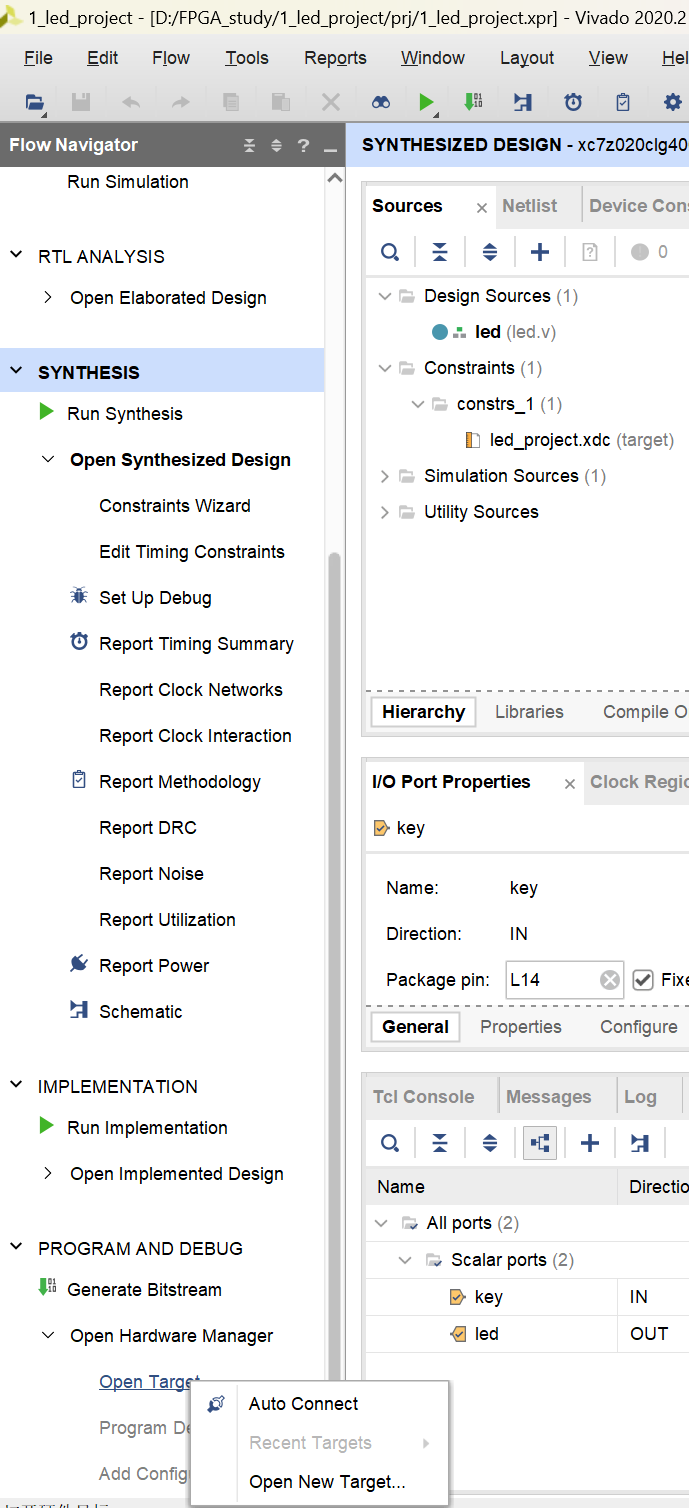

- 之后直接生成点bit流,即可把综合和优化这两个步骤都做了,然后连接开发板,点Open Hardware Manager,在硬件管理器中,点击“Open Target”按钮,选择正确的JTAG链路和FPGA设备。注意:如果没有自动连接成功,要去检查一下是不是自己的下载器驱动没有安装,我这里就犯过这个错误。

-

点灯到此结束!

-

如果在实际上板烧录之前,还想进行仿真,可以编写testbench文件,来进行仿真。

-

后续

-

等学了testbench的写法以后再写一篇帖子来说一说仿真文件怎么写,这里先只附上仿真代码~

`timescale 1ns / 1ps //仿真单位/仿真精度 module tb_led(); //reg define reg key; //wire define wire led; //信号初始化 initial begin key <= 1'b1; //按键上电默认高电平 //key信号变化 #200 //延迟200ns key <= 1'b1; //按键没有被按下 #1000 key <= 1'b0; //按键被按下 #600 key <= 1'b1; #1000 key <= 1'b0; end //例化led模块 led u_led( .key (key), .led (led) ); endmodule

- ①看原理图:查看led灯在什么情况下(高电平or低电平)可以被点亮。这里可以看到LED的一端接地,所以另一端是高电平1时可以将LED灯点亮。

- 开发流程

- 希望对刚入门的伙伴们能有所帮助~

FPGA自学记录2——点亮LED灯

最新推荐文章于 2025-03-12 21:52:41 发布

492

492

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?