文章目录

一、下载Logisim数字逻辑仿真软件

从https://download.csdn.net/download/m0_74045503/88435139下载,先安装Java运行环境JDK,再运行Logsim

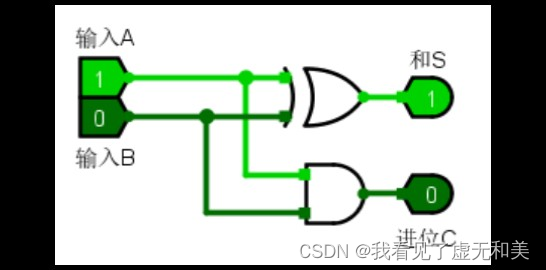

二、设计一个1bit半加器电路

(一)原理分析

1位半加器是一种数字电路,用于执行二进制加法中的最低有效位(LSB)的加法。它可以将两个输入位(A和B)相加,并产生两个输出:和(S)和进位(C)。其逻辑如下:

- 和(S)输出是输入位的异或(XOR)运算结果。即,S = A ⊕ B,其中 ⊕ 表示异或运算。

- 进位(C)输出是输入位的与(AND)运算结果,然后再与(NOT)运算结果。即,C = A ∧ B,其中 ∧ 表示与运算。

在1位半加器中,由于它只能处理一位输入,因此无法处理来自上一位的进位。这就是为什么需要完整的加法器(全加器)来处理多位数相加。

1位半加器可以用以下真值表来表示:

这个电路可以用逻辑门(比如AND门,XOR门等)来实现。

(二)具体实现

确保运算测试正确后,保存为子电路,文件名为half_adder

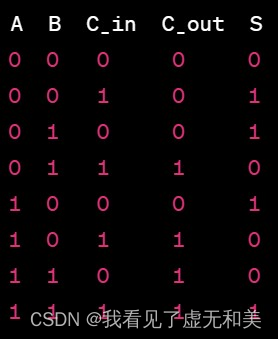

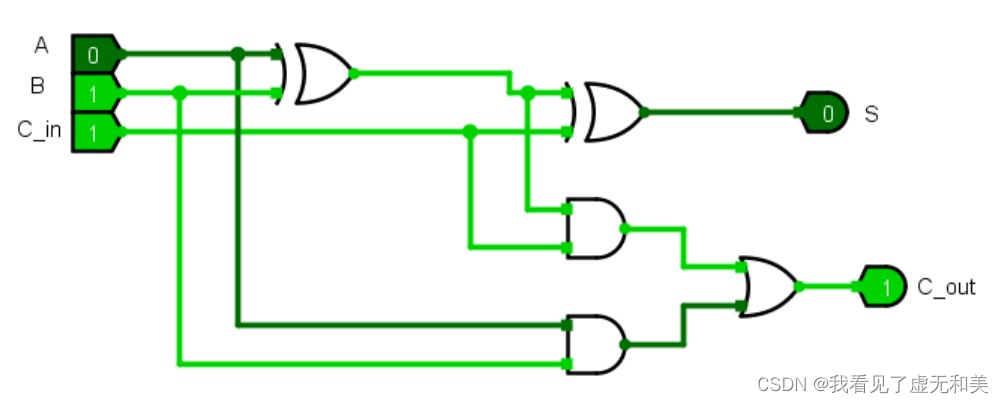

三、设计一个1bit全加器电路

(一)原理分析

1位全加器是一种数字电路,用于执行二进制加法中的位加法。它与半加器不同之处在于,全加器可以处理来自前一位的进位(carry)。1位全加器接受三个输入:两个待相加的位(A和B),以及来自前一位的进位(C_in)。它产生两个输出:和(S)和进位(C_out)。

全加器的逻辑如下:

- 和(S)输出是A、B和C_in的异或(XOR)运算结果。即,S = A ⊕ B ⊕ C_in。

- 进位(C_out)输出有两部分组成,一部分是A和B的与(AND)运算结果,另一部分是(A和B的)异或运算结果与C_in的AND运算结果,然后再通过或(OR)运算得出。即,C_out = (A ∧ B) ∨ (A ⊕ B) ∧ C_in。

1位全加器可以用以下真值表来表示:

这个电路可以用逻辑门(如AND门,OR门,XOR门等)来实现。

(二)具体实现

确保运算测试正确后,保存为子电路,文件名为full_adder

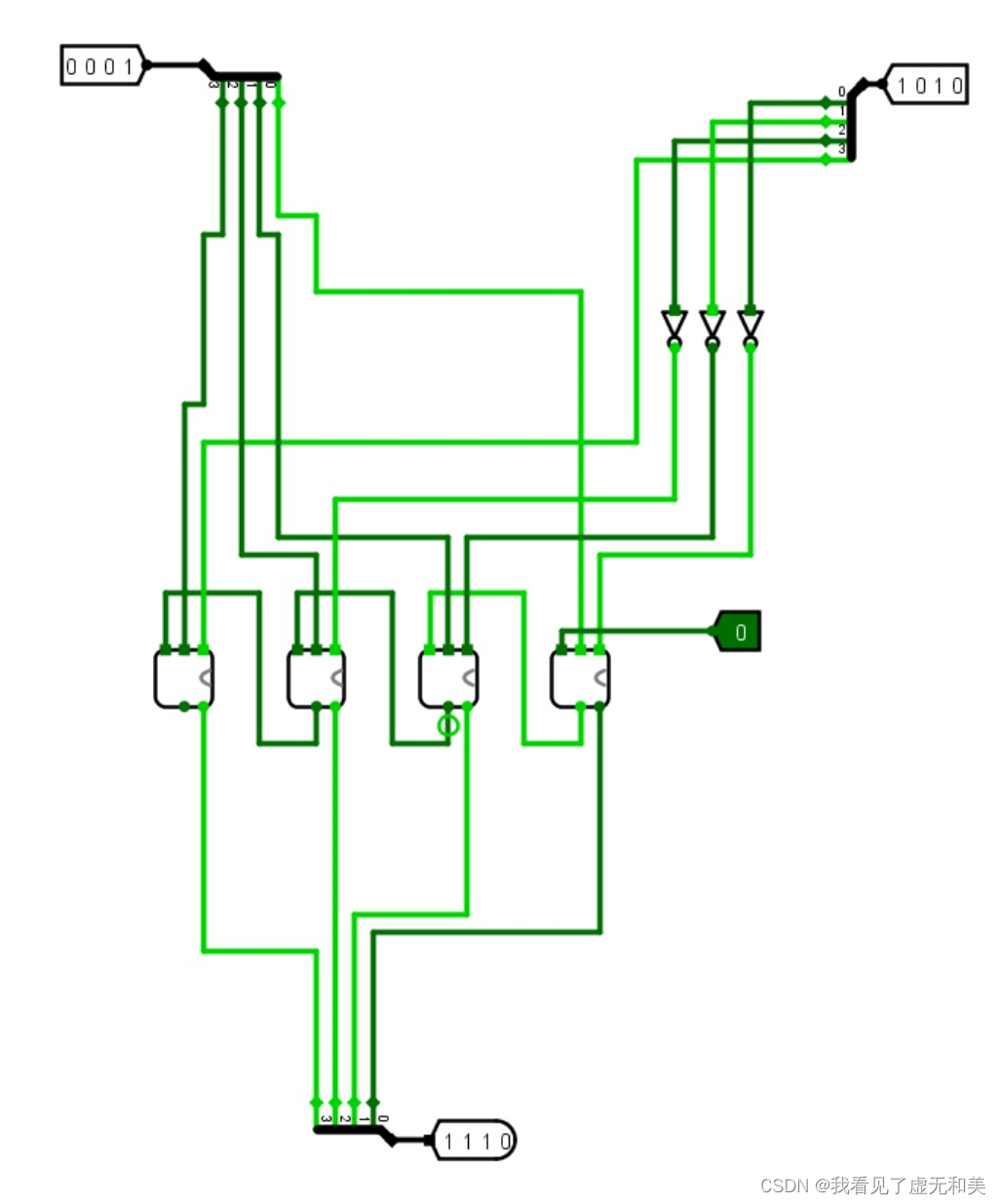

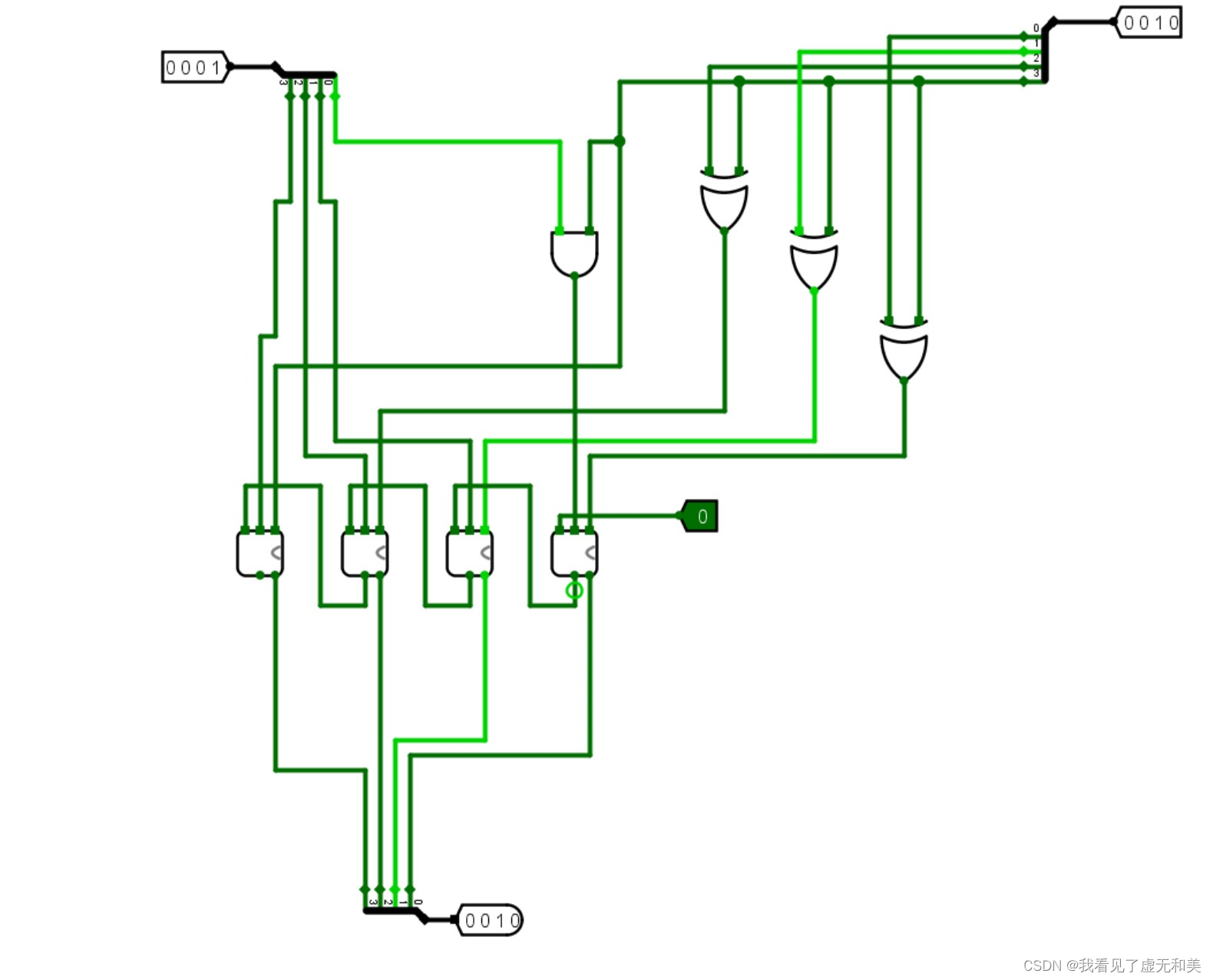

四、实现一个4位二进制数的补码器电路

要求:当输入一个4位二进制数后,补码电路将输出对应的4位二进制补码。

补码原理如下:

(1)正数与原码相同;

(2) 负数的补码,将其原码除符号位外的所有位取反(0变1,1变0,符号位为1不变)后加1。 同一个数字在不同的补码表示形式中是不同的。比如10进制数值-15的二进制原码是10001111,其补码在8位二进制中是11110001,然而在16位二进制补码表示中,不足位数要用符号位补全,也就是1111111111110001。

因为正数和负数的补码运算规则不一样,取决与输入二进制数的最高位(符号位)。从简单入手,可以先只考虑输入为负数情况的补码运算。补码运算中有一个加1运算,需要用全加器实现。 4位全加器可以用4个1位(bit)全加器级联得到。

(一)只考虑输入为负数

此种情况较为简单,按照求补码的思路和理解1bit全加器原理即可做出。

(二)即有正数又可能是负数的情况

思考电路结构,又由异或门(xor)的定义,不难想到,由最高位即是符号位来与每一位进行异或运算,即可在输入正数时输出原来的数,输入负数时取反;输入正数时不需要加1操作,所以用一个简单的与(and)运算来实现是否加1的选择,最后电路实现。

684

684

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?