基于数字电路六位数字钟的设计与实现

- 任务说明

- 主要任务

本实践环节“[27052021]数字电路课程设计”要求基于数字电路实现 6 位数时分秒格式的计时显示。扩展要求:增加时间调节功能。选择合适的元器件,设计、选择合适的输入信号和输出方式,确保电路正确性。设计一个二十四时制的数字钟,时、分、秒分别完成二十四进制或者十二进制(本题我选用的二十四进制的)、六十进制、六十进制的功能,以此来完成计时的功能。

- 目的与意义

通过本课程设计,可以实现一个基于数字电路六位数字钟的设计与实现。进一步巩固所学的理论知识,提高运用所学知识分析和解决实际问题的能力;提高电路布局、布线及检查和排除故障的能力;培养书写综合实验报告的能力。数字钟已成为人们日常生活中必不可少的生活用品。广泛用于个人家庭以及车站、码头、剧场、办公室等公共场所,给人们的生活、学习、工作、娱乐带来极大的方便。

- 设计思路

- 需求分析

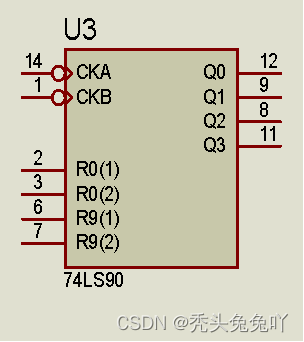

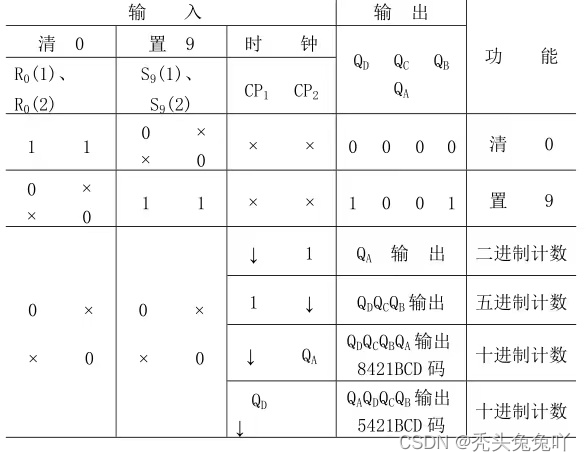

计时对于数电而言就是对已知周期信号的计数,本项目计时单位 为秒,则所用输入脉冲频率应该为 1Hz,然后使用 6 组十进制计数器进行计数, 按照十位为 6 对分秒进行异步清零和进一标志处理,按照两位数为 12 或者 24 进行小时数据异步清零操作;整个电路设置一个输入开关,开关允许时电路计时 否则保持最后的计时数值不变。我用到的元件有:6个7段码显示器(7SEG-COM-ANODE)、6个74LS247、6个74LS90、6个74LS08、1个SW-SPDT、1个激励源DCLOCK等。需要设计一个二十四进制计数器,两个六十进制计数器来实现置零。用74LS90设计24进制电路与60进制电路原理基本相同,只是把原来的60清零改为24清零即可,74LS90是二-五-十进制计数器,它有两个时钟输入端CKA和CKB。其中CKA和Q0组成一位二进制计数器;CKB和Q3Q2Q1组成的五进制计数器;若将Q0与CKB相连,时钟脉冲从CKA输入,则构成了8421BCD码十进制计数器。74LS90有两个清零端R0(1)、R0(2),两个置9端R9(1)、R9(2),且均为高电平有效。

功能1设计

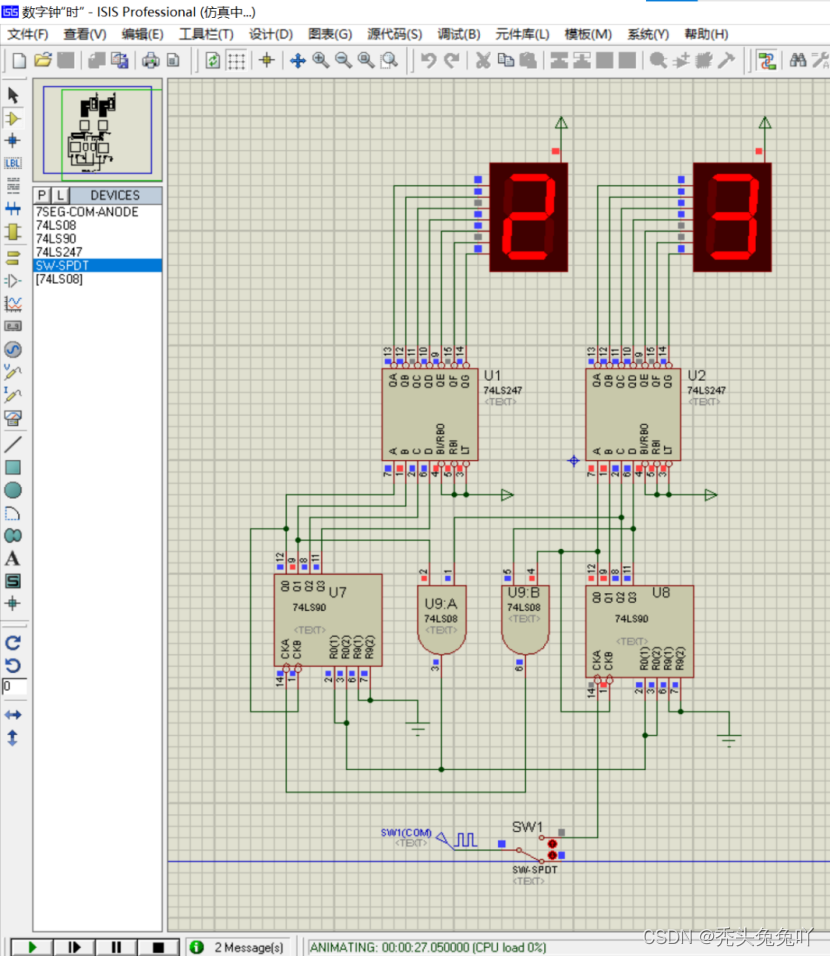

数字钟“时”电路图,设计思路是二十四进制计数,“是按照01———02———03......———22———23———00———01———02......”规律计数的,这与日常生活中的计数规律相同。我用两片74LS90、两片74LS08构成的二十四计数器,利用异步清零端实现“23——00”的反翻转,其中“24”为过渡状态不显示。如图(a)所示

图(a)

功能2设计

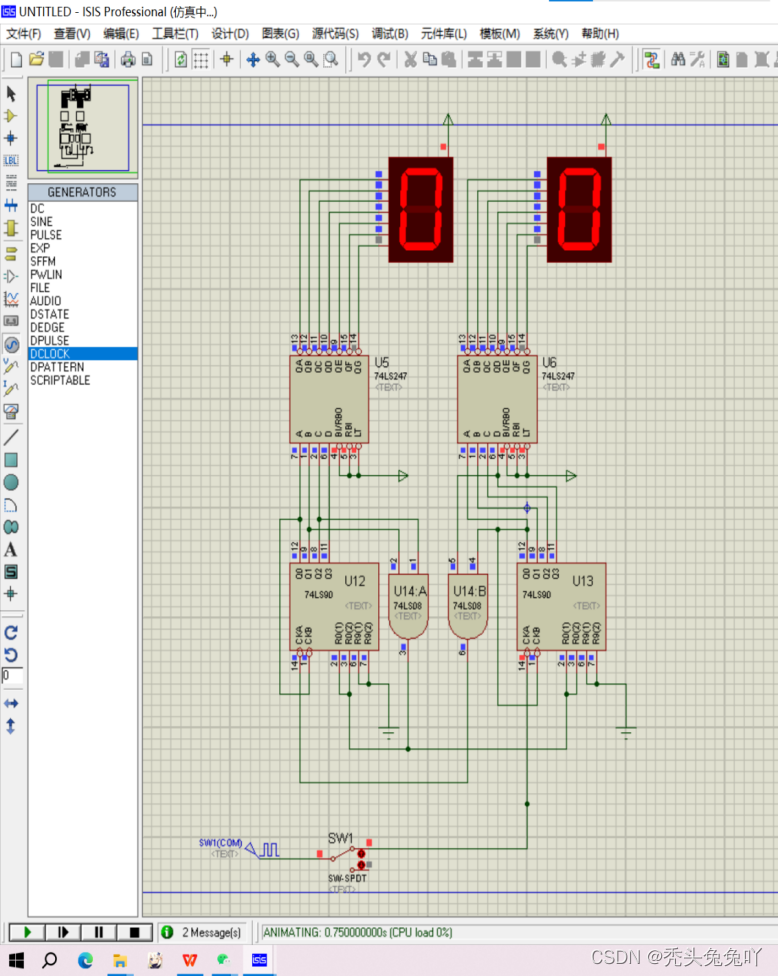

数字钟“分”“秒”电路图,由于分和秒都是运用六十进制计数器,所以电路图是一样的,由激励源DCLOCK来的秒脉冲信号,首先送到“秒”计数器进行 累加计数,秒计数器应完成一分钟之内秒数目的累加,并达到60秒时产生一个进位信号,所以,选用两片74LS90和两片74LS08组成六十进制计数器,来实现六十进制计数。其中“秒”十位是六进制,“秒”个位是十进制。如图(b)所示

图(b)

- 仿真测试

- 1.功能1验证

(1)开关闭合时,显示器停止计时,并且保持原来的数字,如图(c)

图(c)

(2)23之后实现清零状态,如图(d)

2. 功能2验证

(1)开关闭合时,显示器停止计时,并且保持原来的数字,如图(e)

图(e)

(2)59之后可以实现清零状态,如图(f)

图(f)

当电路进行调试时,数字开始计时,开关可以控制运行,而且,电路实现了到达59这个数字时,清零的效果,所以输入输出符合预计效果。

五.设计总结

通过本设计,熟悉了用LS7490设计任意进制计数器,完成了六位数字钟的设计.,对数字钟系统设计与仿真有以下几点收获:

- 在激励源设置时可以编辑它的属性调整频率,由于秒脉冲,所以激励源的频率为1Hz,如果我在调试时想让时间计数的快一点,只要把频率调大一点就可以了。

- .当时在设计脉冲时遇到了问题,经过了老师的辅导我知道了更简单的方法由激励源DCLOCK来给的秒脉冲信号。

- 我在将时、分、秒电路串联设计时,时分秒同时进行了,经过了老师的提点原因是我将秒进制的脉冲信号传达的电路连接错误,没有完全弄清楚74LS90的功能,应该将输出脉冲的那个线连接到下一个进制器的CKA端,就可以实现秒向分进制,分向时进制。

- 刚开始的驱动器选用的元件是CD4511,但是我并没有做出实验,后来经过了探索实现了成功,并且更换了驱动器为元件74LS247,更加贴合我们学过的知识,能更好的理解些。

5.本次实验让我更加了解了任意进制计数器的方法和设计思路。

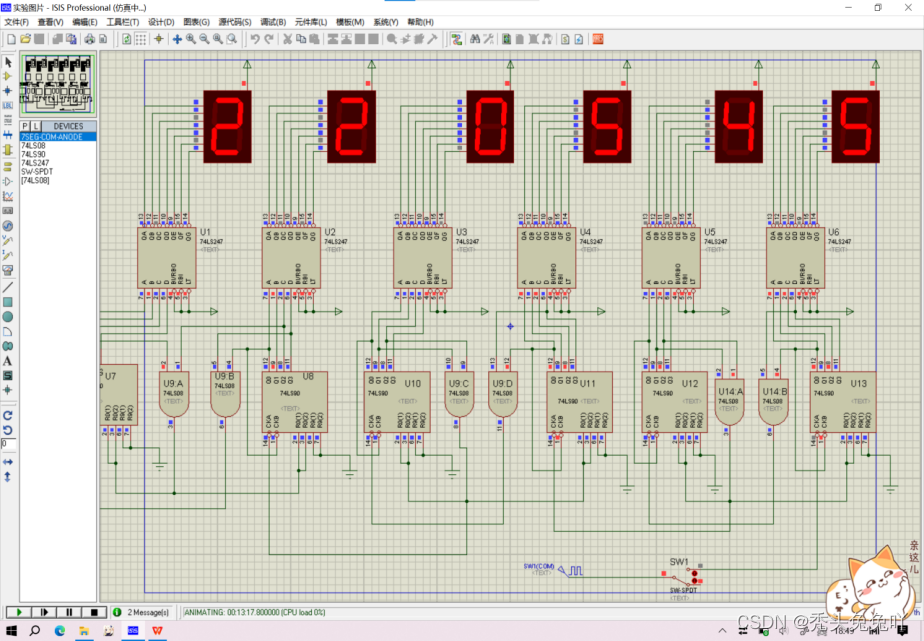

附1,完整电路原理图

由于脉冲频率为1时,时间变化的太慢了,所以我将脉冲源的频率调大,方便我进行验证

附2,电路元件输入输出真值表

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?