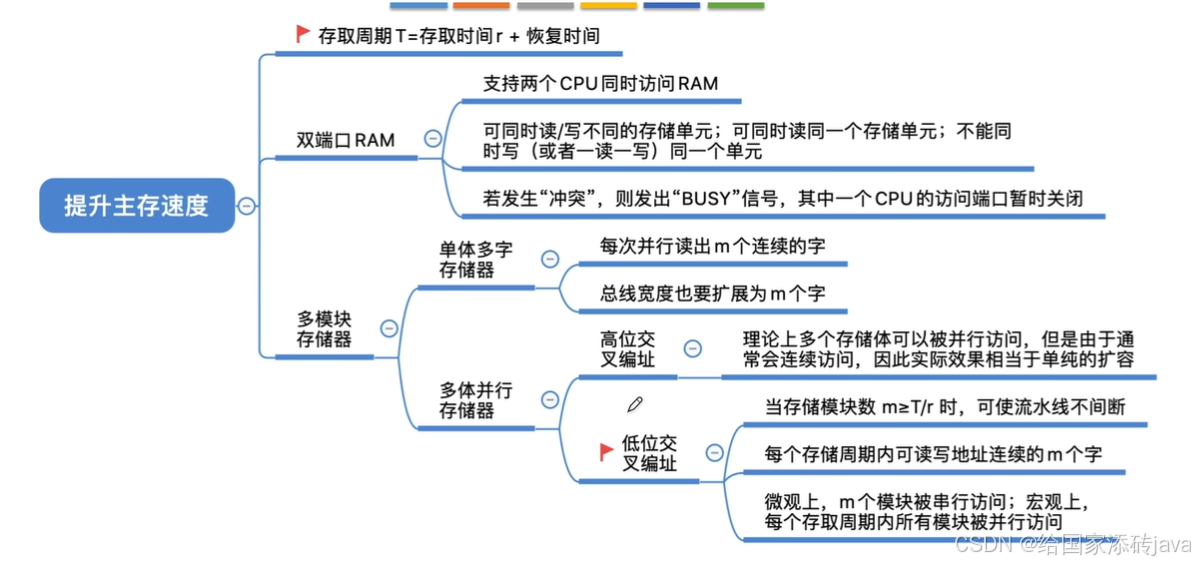

提升主存速度

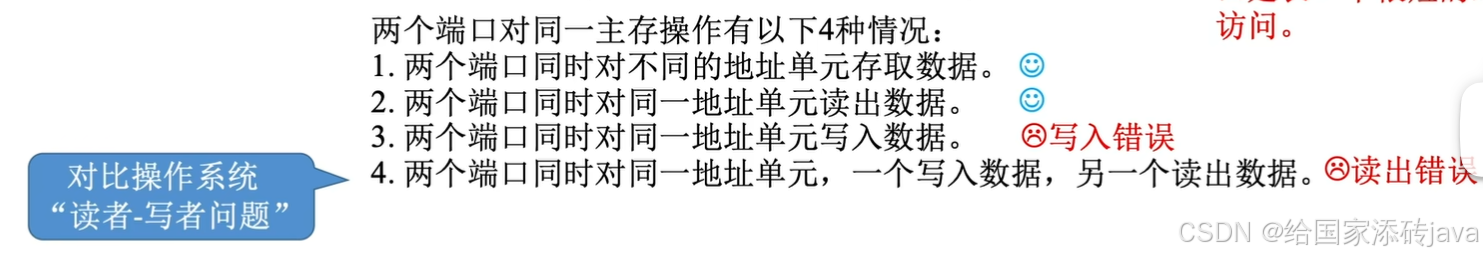

本小节我们讲一下存取周期、双端口RAM(考察的是双端口同时读/同时写的问题)、单体多字存储器、高位交叉编址和低位交叉编址

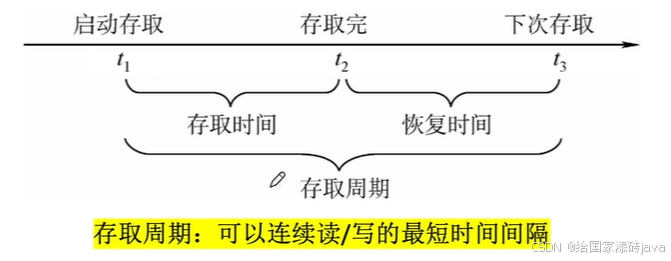

1.存取周期T

存取时间:CPU从内存中读出一个字所需要的时间

存取周期=存取时间+恢复时间

在做题的时候有一点需要注意的是:主机读出一个数据字的时间和向CPU提供一个数据字的时间是不一样的,主机读出一个数据字的时间是存取时间,而提供一个数据字的时间还需要包括恢复时间

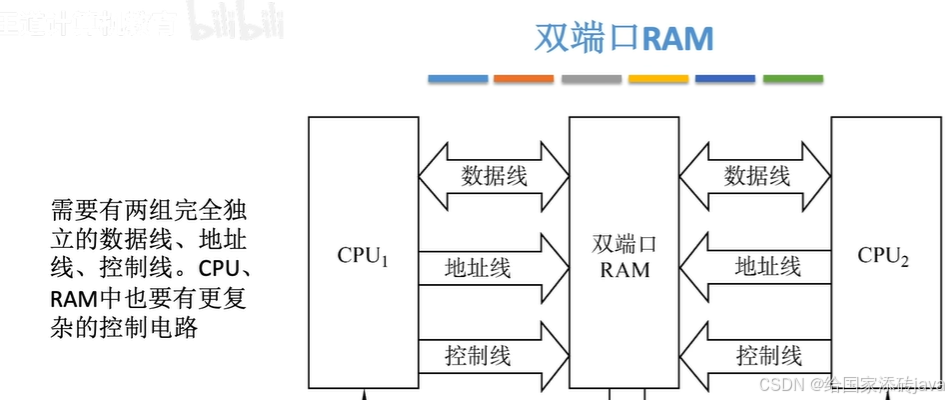

2.双端口RAM

3.多模块存储器

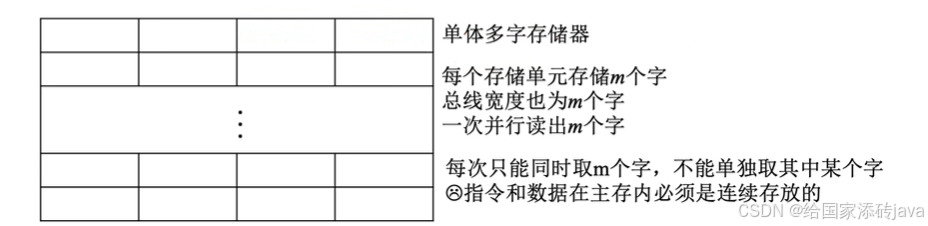

3.1单体多字存储器

每次并行读出m个连续的字,总线宽度也要扩展为m个字,灵活性不如多体并行存储器

3.2多体并行存储器

多体并行存储器有两种编制方案:高位交叉编址和低位交叉编址

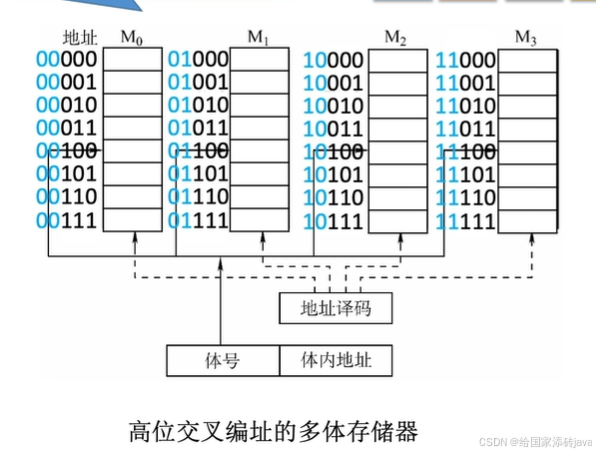

3.2.1高位交叉编址

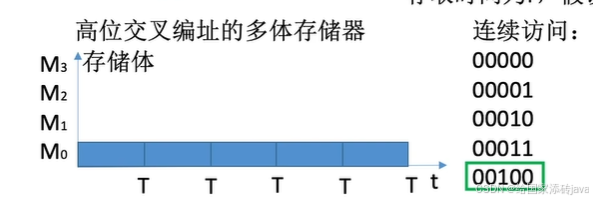

按照地址的从小到大的顺序进行访问,当在访问它的8个地址的时候,还轮不到其余的M,所以他们只能等待

结束,这样就会导致访问n个字需要的时间:

=T*n

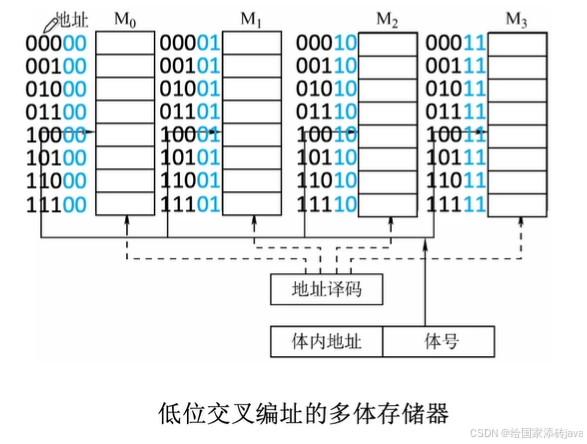

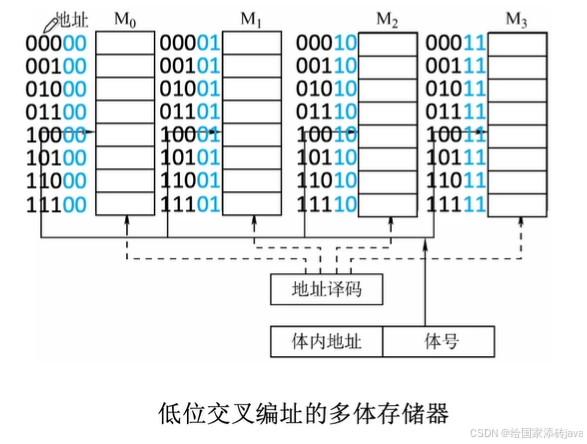

3.2.2低位交叉编址

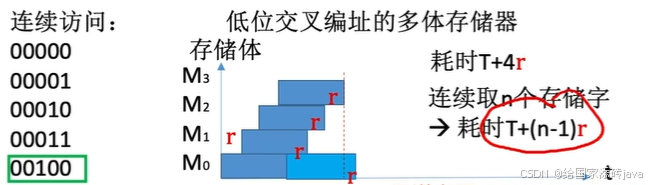

当在访问00000的时候,一旦过了存取时间(不是存取周期),

就紧跟而上,这样就会充分利用CPU,不会让他闲置下来了,访问n个字需要的时间:

=T+(m-1)*r,其中m是模块的数量,r是存取时间

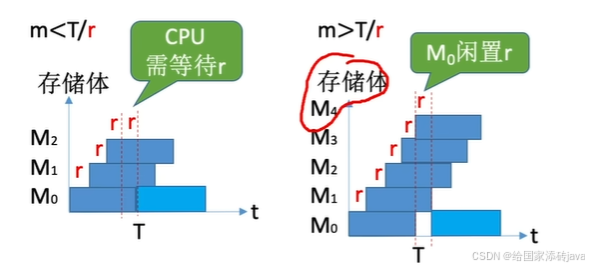

为了“压榨”CPU,我们应该保证模块数m>=T/r

当m<=T/r的时候,CPU至少需要继续等待r的时间,明明所有的模块都经过各自的存取时间了,但是重新轮到该模块的时候,还没到恢复时间,所以它得等恢复时间走完才能接着干活。

当m>T/r的时候,其中一个模块恢复时间已经走完了,它想干活了,但是总模块数量太多了,导致其他的模块存取时间还没走完,所以它只能等到别人的存取时间都结束之后才能干活,这就导致它偷懒了一段时间

思考:给定一个地址x,怎么知道它是在哪个存储体呢?

可以根据地址x的末尾来判断,因为低位交叉编址同一个模块的末尾是相同的

思维导图

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?