前言

- 原理图和接线图,使用multisim仿真软件画原理图,立创EDA画接线图。

- 数字电子钟安装调试问题详见安装调试故障分析

- 个人作业,借鉴即可!

- 还待完善,敬请期待!

- 欢迎评论区留言你对博主写作的建议,感谢!

1.设计要求

1.具有时、分、秒计时及显示。计时范围00时00分00秒——23时59分59秒。

2.具有手动校时、校分功能。

3.能整点报时。从59分51秒开始,逢单响一下(持续1秒),前4响频率为500Hz,最后1响频率为1000Hz。也可逢双响。

2.总体方案设计

根据设计要求1可以得出设计需要译码器、数码和计数器。用译码器和数码管可以将计数器所输出的数据显示出来。

计数器使用CD4029芯片,其功能齐全,可以做到二进制和十进制的加减计数。利用CD4029可以构成时、分、秒计时,他灵活多变,可以达到预期的效果。其数据置数端可以将输出的信号经过处理(即使用逻辑门电路处理)后输送给置数端,从而构成不同的进制,实现23时59分59秒计时,其中逻辑门电路采用集成芯片74LS00和74LS04构成。

译码器和数码管功能是将计数芯片输出的信号转换为具体数据进行显示。

译码器使用CD4511芯片,CD4511 是一片 CMOS BCD—锁存/7 段译码/驱动器,用于驱动共阴极 LED (数码管)显示器的 BCD 码-七段码译码器。具有BCD转换、消隐和锁存控制、七段译码及驱动功能的CMOS电路能提供较大的拉电流。可直接驱动共阴LED数码管。利用CD4511芯片作为译码器可以将计数芯片输出的信号快速的转换为LED数码管所需的信号进行数据显示。

根据设计要求2可以得出,进行计数的时脉冲和分脉冲需要灵活的进行改变。可以使用不同频率的脉冲进行校时校分。

根据设计要求3可以得出,进行整点报时时,数据应当为分十位为5,分个位为9,秒十位为5,秒个位为单数或双数,可以通过数据选择器控制是否报时,数选器选用74LS153,逻辑门电路选用74LS74。因为报时前4响频率为500Hz,最后1响频率为1000Hz,所以需要不同频率的脉冲对蜂鸣器进行输入,达到整点响时不同的效果。

3.各部分单元电路设计

3.1计数器设计

计数器的设计主要是通过改变CD4029的LD端的状态从而达到不同进制的实现,置数端全部置0。其中使用 CD4511和LED数码管显示数值。其接线图如图3.1所示

图3.1 CD4511和LED数码接线图

3.1.1 M60进制计数器设计

CD4029计数器的功能选择为十进制同步加计数,即B'/D与U'/D端接高电平。

根据需求可以获得状态转换表如图3.1.1.1所示:

图3.1.1 M60进制转换表

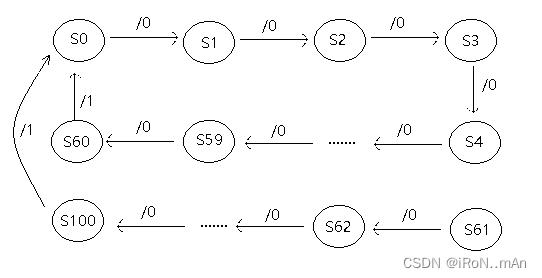

根据状态转换表可以获得状态转换图如图3.1.1.2所示:

图3.1.1.2 M60状态转换图

由状态转换图可以得出,电路可以自启动。

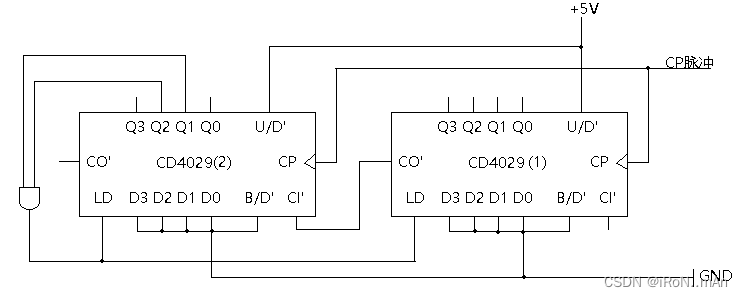

60进制计数器由两片CD4029芯片构成,十位为高位片,个位为低位片。

60进制计数器的原理图如下图3.1.1.3所示

图3.1.1.3 M60进制计数器原理图

高位片应设计为6进制加计数,低位片为10进制加计数,进行极连后构成60进制计数器。60的二进制为0110 0000,因为计数达到60后应该清零,所以当高位片Q2,Q1同时为1时,LD端有效,两个芯片同时清零,重新开始计数,实现了60进制的加计数。

3.1.2 M24进制计数器设计

CD4029计数器的功能选择为十进制同步加计数,即B'/D与U'/D端接高电平。

根据需求可以获得状态转换表如图3.1.2.1所示:

图3.1.2.1 M24进制转换表

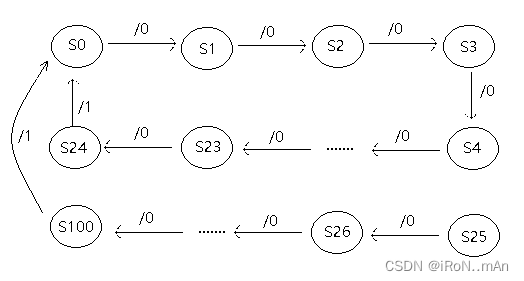

根据状态转换表可以获得状态转换图如图 3.1.2.2所示:

图 3.1.2.2 M24状态转换图

由状态转换图可以得出,电路可以自启动。

24进制计数器由两片CD4029芯片构成,十位为高位片,个位为低位片。

24进制计数器的原理图如下图3.1.2.3所示

图3.1.2.3 M24进制计数器原理图

24的二进制为0010 0100,因为计数达到24后应该清零,所以当高位片Q1和低位片的Q2同时为1时,LD端有效,两个芯片同时清零,重新开始计数,实现了24进制的加计数。

3.2时分秒设计

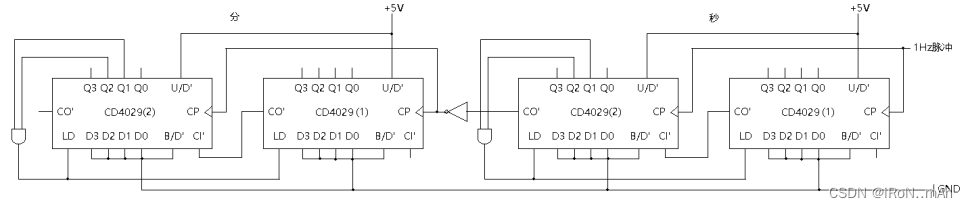

将设计好的一个60进制计数器的脉冲输入端接入频率为1Hz的方波信号,实现秒的设计。

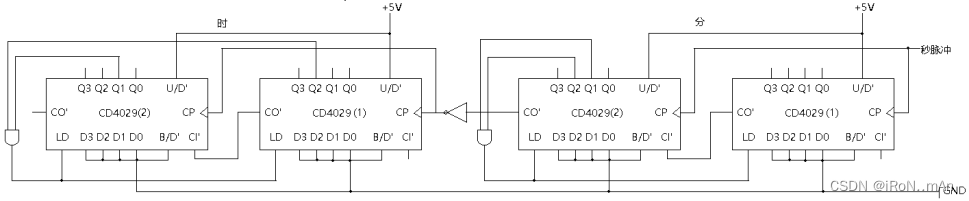

将秒的高位片进位输出端的信号取反后作为脉冲信号给到另一个60进制计数器的脉冲输入端,实现了分的设计。其原理图如下图3.2.1所示:

图3.2.1分秒原理图

将分的高位片进位输出端的信号取反后作为脉冲信号给到24进制计数器的脉冲输入端,实现了时的设计。其原理图如下图3.2所示:

图3.2.2时分原理图

3.3手动校时、校分设计

连接好的时钟上电后与标准时间有误差,或者与预期时间不符,为了能够调整时间,需要设计校时与校分电路。

校分电路如图3.3.1所示:

图3.3.1 校分电路

校时电路如图3.3.2所示:

图3.3.2 校时电路

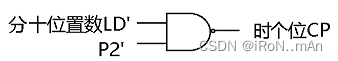

因为CD4029芯片是上升沿触发,作为分的脉冲需要上升沿脉冲信号,所以当秒发生进位时,分CP脉冲应从低电平变为高电平。为了保证未校分的时候,秒位产生的进位脉冲能够使得计数正常工作,这样分个位脉冲就是由秒产生的进位信号控制,用LD作为进位信号时,LD是由低电平变成高电平,将LD取反后变为由高电平变成低电平,与分位的CP脉冲条件不符,所以需要将LD取反后作为CP脉冲信号。当进行校分操作时,因为秒十位置数LD'只有产生进位时,LD'才会有变化,没有进位时,LD'始终保持高电平,分个位CP脉冲由P1'控制,实现了校分操作。

校时原理与校分相似,仅是将手动校时脉冲给到P2'脉冲,然后与分十位置数LD'相与后作为时的时间脉冲,从而实现校时的操作。

3.4整点报时

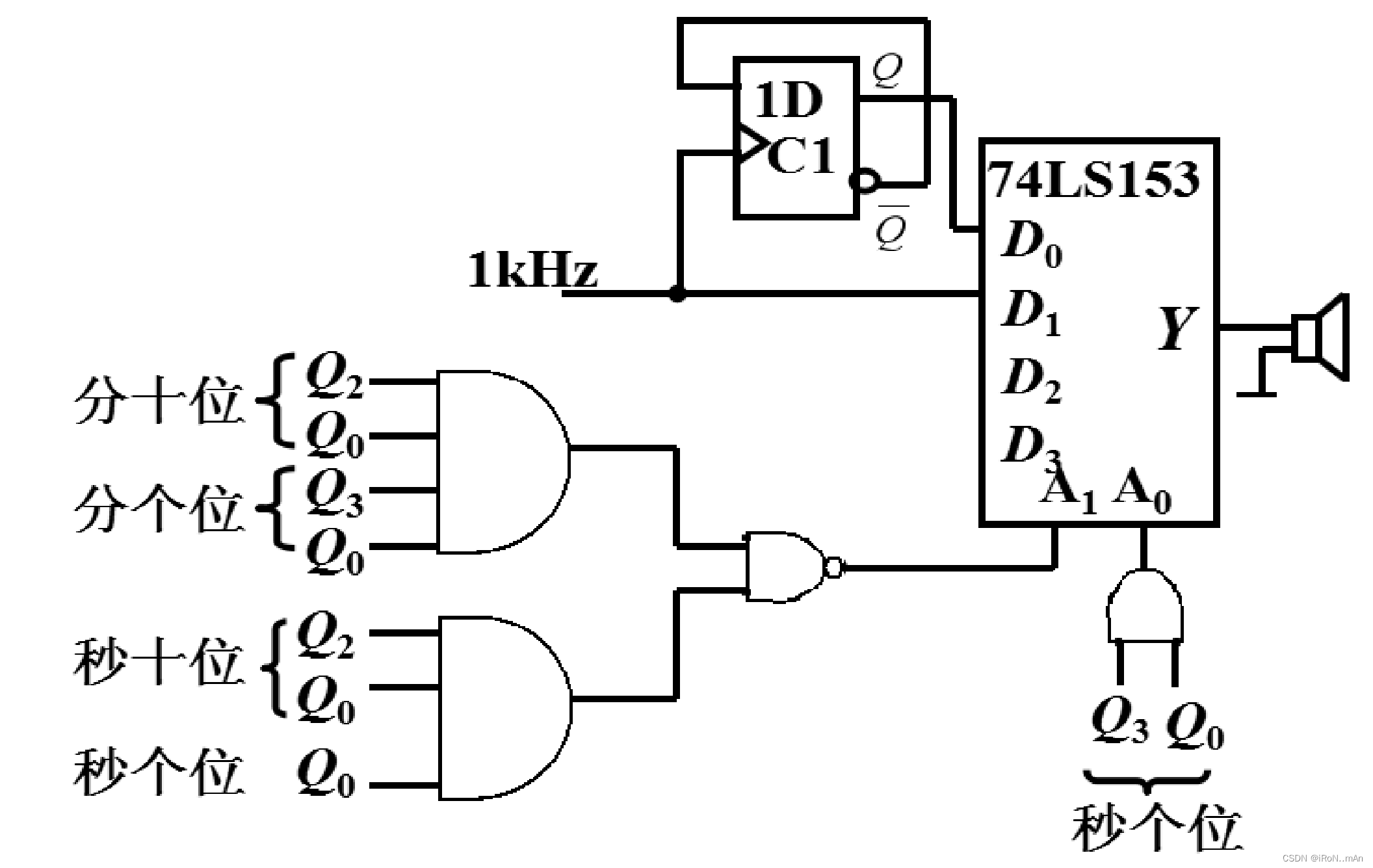

整点报时原理图如图3.4所示:

图3.4 整点报时原理图

整点报时设计要求为逢单响能整点报时。从59分51秒开始,逢单响一下(持续1秒),前4响频率为500Hz,最后1响频率为1000Hz。

使用喇叭进行输出,喇叭在不同频率下的声响会有不同,可以区别前四响和最后一响。

其中使用D门电路作为频率分频,即将一千赫兹的信号变为五百赫兹的信号。D门触发的功能是来一次脉冲翻转一次,相当于将信号削减为原来的一半,可以将1kHz的信号变为原来的一半,即500Hz,可以提高信号的利用率。

为了完成在指定的条件下喇叭响声不同,即59分51秒开始,逢单响一下,前4响频率为500Hz,最后1响频率为1000Hz。使用74LS153芯片对数据进行选择,可以达到目的。将500Hz的信号接入D0,1kHz接入D1,D2、D3皆接地。数选器的表达式如下:

Y=D0(A1A0)+D1(A1A0)+D2(A1A0)+D3(A1A0)

因为时间需要达到59分51秒时喇叭为500Hz时的响声,所以在数选器的数选输入端A1A0应该在这个时间的时候同时为0(低电平),选择500Hz的信号进行输出。此时分十位为5(即分十位片的Q2Q0为1),分个位为9(即分个位片的Q3Q0为1),秒十位为5(即秒十位片的Q2Q0为1),秒个位为1(即秒个位片的Q0为1),即A1由他们控制。因为500Hz信号在D0,所以A1应为0,可以得到作为A1的表达式应为A1=(Q2(分十)Q0(分十)Q3(分个)Q0(分个)Q2(秒十)Q0(秒十)Q0(秒个))'。

因为时钟逢单响,最后一响为1kHz,D1为1kHz,所以通过A0的状态可以进行数据选择。通过分析可知,秒个位为9时输出1kHz,为其他为500Hz。所以前四响时数据选择器输出都是D0,即A0为0,最后一响输出D1,即A0为1。所以可以得出最后一响和秒个位的Q3有关,其他都只和Q0有关,得出A0表达式应为A0=Q3Q0。

最终可以实现整点报时功能。

4.安装、布线、调试注意事项

安装、连线注意事项:

1 检查器件,确保器件无断脚、弯脚,管脚应稍向外偏,以便接触良好;

2 所有器件按照在图中的位置布局好,匀称分布;

3 所有器件就近布局、缺口朝左、跨槽放;

4 弯管脚拨直后用,断管脚的不用,确保器件和面包板接触良好;应用小切子拨下器件

5 将所有IC的电源端串接在一起,接数字箱上的Vcc(+)端;将所有IC的地端串接在一起,接数字箱上的GND(-)端;确保数字箱上电源和地不短路,(如果指示灯不亮,数字箱上电源和地可能短路),确保所有IC接上电源和地、数字箱上电源不短路;

6 应接高电平的管脚就近接其Vcc端,应接低电平的管脚就近接其GND端,

7 连接导线两边裸头以5mm为宜,太短接触不好,太长易造成短路;连线接触良好,弹性—不用—两根插一孔;

8 接线正确,不能有短路、断路、多线、少线和接触不良现象;

总体调试步骤:

秒个位 秒十位(10) 秒十位(6)

秒(60) 分个位 分十位(10)

分十位(6) 分十位(10) 时个位

(10) 时十位(10) 时(24)

校时、校分 整点报时 脉冲产生

5.调试中遇到的问题和故障分析

1.校时校分模块线路接好后,分秒、时分进位异常,失去计数功能。将校时校分手动脉冲所控制的输入端断开后,正常工作。通过分析74LS00芯片得出断开时,对应的管脚为高电平,发现手动脉冲不工作时接入的是低电平,换为不工作时状态为高电平时的脉冲后,计时正常。

2.校时校分时,按下脉冲后,分和时没有逐次加一,会出现随机值,通过分析确定是接触不良。初步认为导线问题,将导线跟换后,效果一样。确认不是导线问题后,认为是脉冲输入有问题。将脉冲更改为开关控制,校时校分工作正常。

3.时间报时模块线路接好后,发现喇叭不响,以为喇叭损坏,将喇叭直接接入脉冲时,喇叭正常工作,排除喇叭损坏情况。猜想数选控制端输入异常,用电压表测出各个电位正常,目测控制输入端路线没问题。猜想74LS20芯片损坏,将其输入端全接入高电平,用电压表测得输出低电平,将任意一根接入低电平,测得输出高电平,排除该芯片问题。用同样的方法排查74LS04和74LS00芯片,确定未损坏。排查153芯片,将A1A0、D0D1D2D3端同时接地,分析得出输出应为低电平,但测得输出为1.405V,认为芯片损坏,更改芯片后,发现结果差不多。检查153电路发现,芯片的异步清零端接入高电平,更改后喇叭响。

4.喇叭输出声响全部相同,认为153芯片D1D0端信号相同,即74LS74芯片未正常工作,将喇叭正极接入153芯片D1D0端,喇叭正常工作,排除74LS74芯片出错。认为A0端输入有问题,检查线路发现,A0端输入信号接到其他管脚,更改后调试,报时正常工作。

6.设计结果情况

时钟工作正常,给1Hz的信号时,时分秒计时工作正常。手动校时脉冲输入时,时正常增加,校分脉冲输入时,分正常增加,校时模块工作正常。当时间到59分51秒时,喇叭低响,持续1秒,随后时间每增加俩秒,即逢单时响,前四响低响,第五响,即59秒时高响,报时模块工作正常。

7.心得体会

通过这次实践课程,我获得了很多有用的经验。

通过设计数字时钟,让我掌握了如何利用Multisim绘制原理图,利用立创EDA绘制接线图。接线过程中也学会了如何布置各芯片和线路,能够在面包板上接线好看。

在设计时间计时模块时,让我深刻理解并掌握了其原理和接线,学会了如何设计计数进制。在设计校时校分、整点报时模块时掌握了如何将需求和理论相结合。更是学会了如何调试并检查电路出现的问题,能够合理利用所学的理论知识检查电路,并通过分析猜测故障出现的可能原因并逐次对其进行排查。

这次实践也让我体会到了努力所带来的喜悦,让我明白了想要做好实验,需要有一颗沉稳冷静的心,也让我明白当遇见问题时应该要学会分析问题可能出现的原因。相比较以前做实验的自己,发现自己进步了很多。以前线路一有问题,第一想法就是线路接得有问题,总是会将所有的线路拆掉重接,遇见输出结果有问题,第一想法就是芯片有问题,然后一次又一次地更换芯片。

总的来说,通过这次的课程设计,让我理解了部分理论知识。通过实践与理论相互结合,不仅帮助我解决电路遇见的问题,同时也让我理解原理,让我对其印象深刻。同时也让我学会了发现问题、分析问题和解决问题的方法。

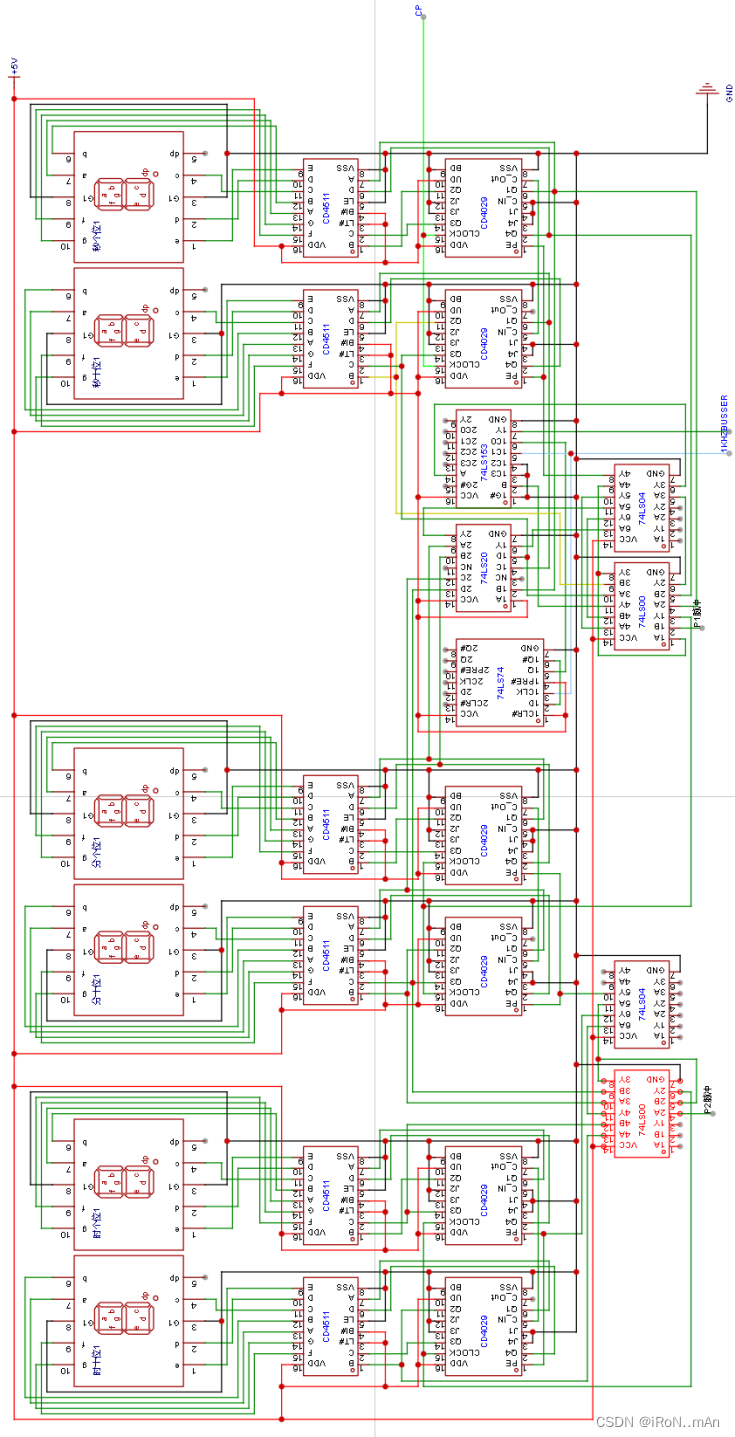

附录(含有电路原理总图、总接线图)

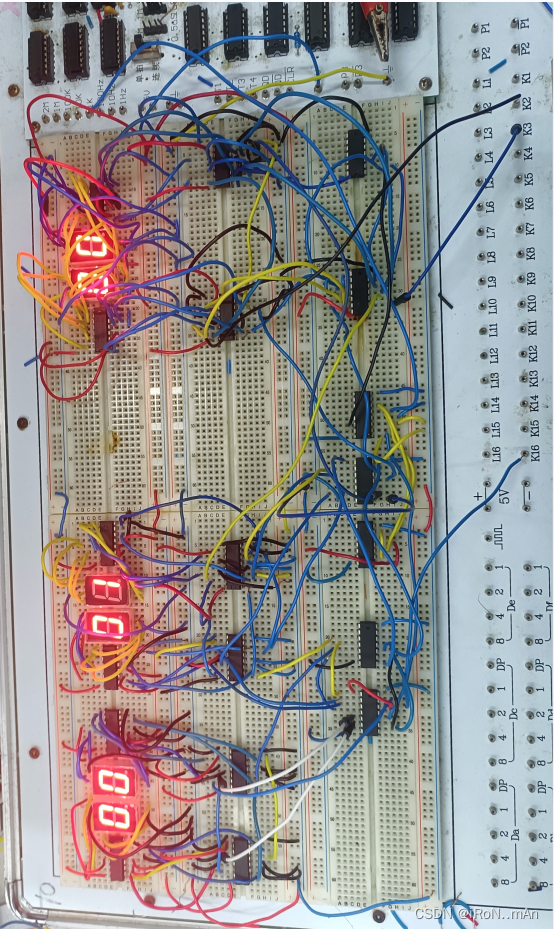

总接线图如下图所示:

实物接线图如下图所示:

器件清单

74LS00 四 2输入与非门

74LS04 六反相器

74LS20 双4输入与非门

CD4029 二/十进制同步计数器

CD4511 译码器

74LS74 双上升沿DFF

74LS153 双4选1数据选择器

BS207 数码管

参考文献

[1]电子技术实验与课程设计.蔡忠法.浙江大学出版社.2003.1.

[2]数字电路实验与课程设计.吕思忠.哈尔滨工业大学出版社.2008.8.

[3]电子电路设计与实践.姚福安.山东科技出版社.2001.10.

[4]电子技术课程设计指导.彭介华.高等教育出版社.1997.9.

[5]数字电子技术基础(第六版).阎石.高等教育出版社.2016.4.

请各位喝点小酒,顺便帮忙点个赞!感谢!

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?