一 、实验目的

-

- 掌握时钟的使用方法

- 掌握锁存器和触发器的原理

- 掌握计数器模块的设计方法

- 掌握移位寄存器的设计方法

- 掌握存储器阵列的设计方法

- 了解点阵屏在数字电路中的应用

- 理解时序电路设计在应用场景中的作用

二 、实验环境

本实验采用Logisim电路仿真平台。在使用Logisim设计本实验基础题要求的数字电路的时候,允许使用和不允许使用的器件如下:

| 允许使用 | Logisim提供的运算器(如封装好的加法器和复用器)、带译码器的七段数码管 |

| 不允许使用(除非特别提示) | Logisim提供的存储单元(如封装好的D触发器、计数器、移位寄存器、存储器阵列) |

三 、实验记录

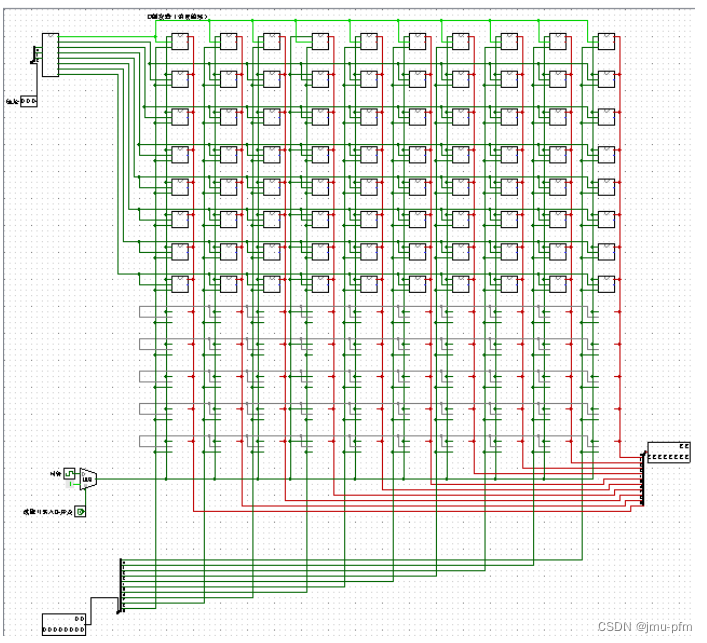

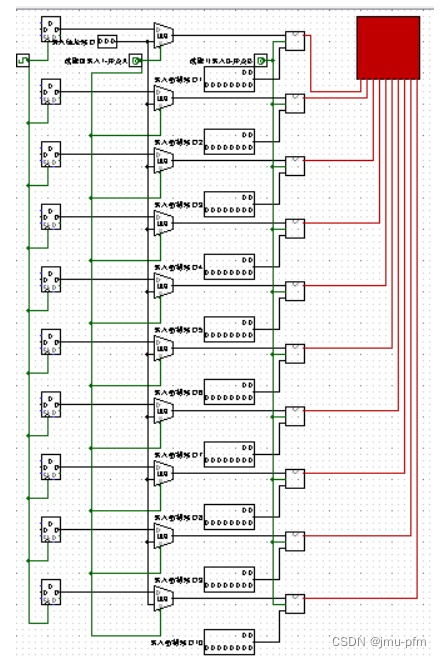

在f题基础之上,我们重新设计了一个8X10存储器并利用此设计了一个10X10的具有存储功能的显示屏。

8X10寄存器原理图如下:

最终效果原理图:

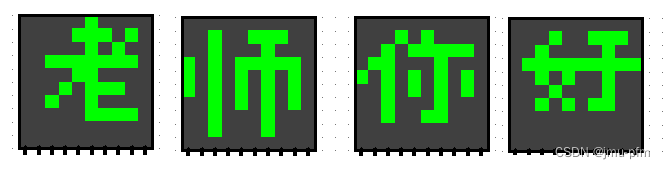

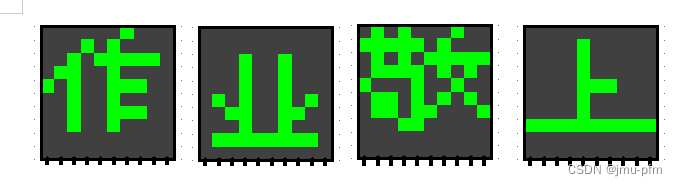

测试结果:我们将“老师你好,作业敬上”这句话存储在了8X10存储器里,并最终依次输出,最终效果如下:

四、问题以及其解决

在设计8X10存储器时有部分障碍导下问题完美解决。

五、总结

各部分实验正常运行达到预期目标,实验圆满完成!

3880

3880

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?