文章目录

Buaa-logisim基础时序逻辑电路

前言

- 本文顺序参考的是🐂老师教学PPT,但对一些细节方面有优化,主要解决了🐂老师上课讲不清楚PPT也没写清楚的bug

- 同以前博客,一些基础概念性和过于简单的内容不会提及,博客主要方式以电路分析+logisim实例实现为主

- 本文大部分时钟采用引脚代替是因为需要使用电路封装。

时序逻辑简介

时序逻辑电路,最大的特点就是电路输出由输入和电路当前状态共同决定(类似Mealy有限状态机的定义,但略有不同,之后会讲解)

第二个小特点就是与时钟沿的密切关系,同步时序电路状态均在时钟沿才发生改变

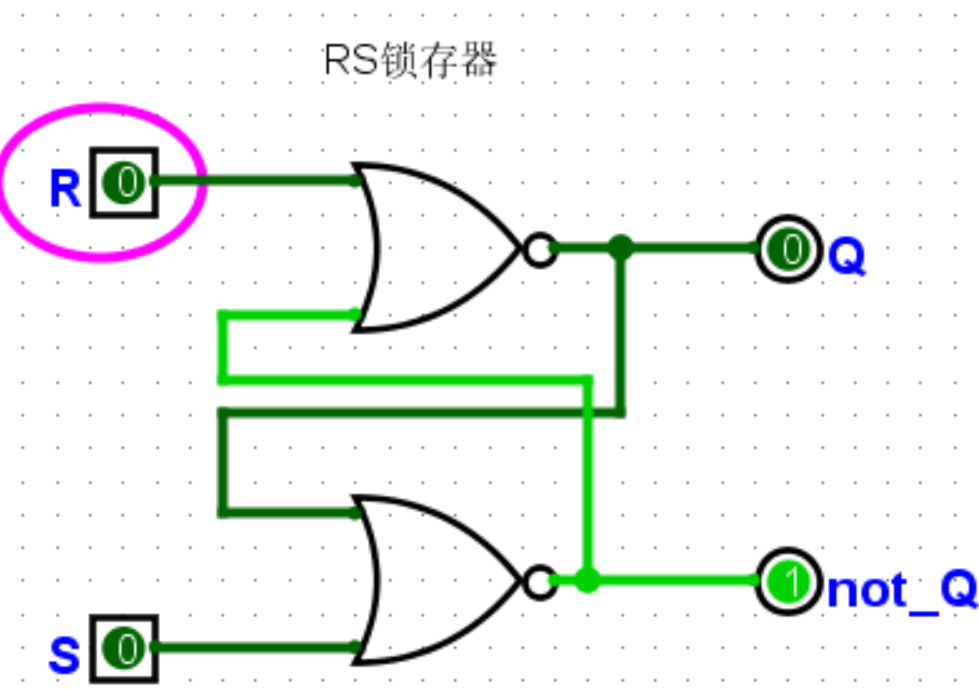

RS锁存器

是许多时序逻辑电路的基础,本文实现的各种D触发器、寄存器、有限状态机等均以其为基础

问题1:为何叫RS锁存器?

答:R(RESET)S(SET)锁存器,基本功能是存储输出,具有两个输入引脚R、S,R的作用是重置输出端Q为0,S的作用则是赋值输出端Q为1

logisim实现

4类输入输出情况

| R | S | 输出Q | 功能 |

|---|---|---|---|

| 0 | 0 | Q p r |

本文详细介绍了基于Buaa-logisim的时序逻辑电路,包括RS锁存器、D锁存器及其优化后的D触发器。通过电路分析和logisim实例,阐述了时序逻辑电路的工作原理和问题解决,重点讨论了D触发器的四种实现方式,引入了使能端和复位功能。

本文详细介绍了基于Buaa-logisim的时序逻辑电路,包括RS锁存器、D锁存器及其优化后的D触发器。通过电路分析和logisim实例,阐述了时序逻辑电路的工作原理和问题解决,重点讨论了D触发器的四种实现方式,引入了使能端和复位功能。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3867

3867

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?