#教育优质作者发文挑战赛#

大家好,今天给同学们介绍一下RIP基本功能相关配置

01、基本概念

RIP是一种基于距离矢量(Distance-Vector)算法的协议,它使用跳数(Hop Count)作为度量值来衡量到达目的地址的距离。在RIP网络中,缺省情况下,设备到与它直接相连网络的跳数为0,通过一个设备可达的网络的跳数为1,其余依此类推。也就是说,度量值等于从本网络到达目的网络间的设备数量。为限制收敛时间,RIP规定度量值取0~15之间的整数,大于或等于16的跳数被定义为无穷大,即目的网络或主机不可达。由于这个限制,使得RIP不可能在大型网络中得到应用。

02、组网需求

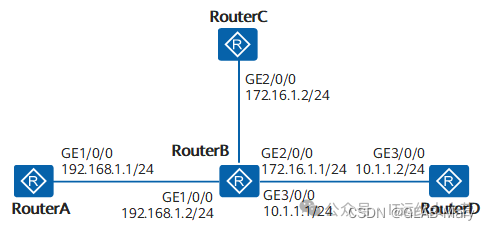

在网络中有4台路由器,要求在RouterA、RouterB、RouterC和RouterD上实现网络互连。

03、实验拓扑

配置RIP版本组网图

04、配置思路

由于要在小型网络中实现设备的网络互连,所以推荐配置RIP-2路由协议。

配置各接口IP地址,使网络可达。

在各路由器上使能RIP,基本实现网络互连。

在各路由器上配置RIP-2版本,提升RIP路由扩展性能。

05、操作步骤

1、配置各路由器接口的IP地址

配置RouterA。

<Huawei> system-view

[Huawei] sysname RouterA

[RouterA] interface gigabitethernet 1/0/0

[RouterA-GigabitEthernet1/0/0] ip address 192.168.1.1 24

RouterB、RouterC和RouterD的配置与RouterA一致(略)。

2、配置RIP基本功能

配置RouterA。

[RouterA] rip

[RouterA-rip-1] network 192.168.1.0

[RouterA-rip-1] quit

配置RouterB。

[RouterB] rip

[RouterB-rip-1] network 192.168.1.0

[RouterB-rip-1] network 172.16.0.0

[RouterB-rip-1] network 10.0.0.0

[RouterB-rip-1] quit

配置RouterC。

[RouterC] rip

[RouterC-rip-1] network 172.16.0.0

[RouterC-rip-1] quit

配置RouterD。

[RouterD] rip

[RouterD-rip-1] network 10.0.0.0

[RouterD-rip-1] quit

查看RouterA的RIP路由表。

[RouterA] display rip 1 route

Route Flags: R - RIP

A - Aging, S - Suppressed, G - Garbage-collect

-------------------------------------------------------------------------

Peer 192.168.1.2 on GigabitEthernet1/0/0

Destination/Mask Nexthop Cost Tag Flags Sec

10.0.0.0/8 192.168.1.2 1 0 RA 14

172.16.0.0/16 192.168.1.2 1 0 RA 14

从路由表中可以看出,RIP-1发布的路由信息使用的是自然掩码。

3、配置RIP的版本

在RouterA上配置RIP-2。

[RouterA] rip

[RouterA-rip-1] version 2

[RouterA-rip-1] quit

在RouterB上配置RIP-2。

[RouterB] rip

[RouterB-rip-1] version 2

[RouterB-rip-1] quit

在RouterC上配置RIP-2。

[RouterC] rip

[RouterC-rip-1] version 2

[RouterC-rip-1] quit

在RouterD上配置RIP-2。

[RouterD] rip

[RouterD-rip-1] version 2

[RouterD-rip-1] quit

4、验证配置结果

#查看RouterA的RIP路由表。

[RouterA] display rip 1 route

Route Flags: R - RIP

A - Aging, S - Suppressed, G - Garbage-collect

-------------------------------------------------------------------------

Peer 192.168.1.2 on GigabitEthernet1/0/0

Destination/Mask Nexthop Cost Tag Flags Sec

10.1.1.0/24 192.168.1.2 1 0 RA 32

172.16.1.0/24 192.168.1.2 1 0 RA 32

从路由表中可以看出,RIP-2发布的路由中带有更为精确的子网掩码信息。

06、配置文件

RouterA的配置文件

#

sysname RouterA

#

interface GigabitEthernet1/0/0

ip address 192.168.1.1 255.255.255.0

#

rip 1

version 2

network 192.168.1.0

#

return

RouterB的配置文件

#

sysname RouterB

#

interface GigabitEthernet1/0/0

ip address 192.168.1.2 255.255.255.0

#

interface GigabitEthernet2/0/0

ip address 172.16.1.1 255.255.255.0

#

interface GigabitEthernet3/0/0

ip address 10.1.1.1 255.255.255.0

#

rip 1

version 2

network 192.168.1.0

network 172.16.0.0

network 10.0.0.0

#

return

RouterC的配置文件

#

sysname RouterC

#

interface GigabitEthernet2/0/0

ip address 172.16.1.2 255.255.255.0

#

rip 1

version 2

network 172.16.0.0

#

return

RouterD的配置文件

#

sysname RouterD

#

interface GigabitEthernet1/0/0

ip address 10.1.1.2 255.255.255.0

#

rip 1

version 2

network 10.0.0.0

#

return

以上是配置RIP基本功能示例

关注 工 仲 好:IT运维大本营,获取60个G的《网工系统大礼包》

1038

1038

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?