题目1: 设计一个 8 位字节比较器

1、设计方案

输入为时钟i_clk,复位i_rst,a,b;输出为re,reb,eq。使用组合逻辑,always语句块

2、程序代码

2.程序代码

`timescale 1ns/1ns

module compare_8bit(

input i_clk,

input i_rst,

input [7:0]a,

input [7:0]b,

output reg re,

output reg reb,

output reg eq

);

always@(*)begin

if(i_rst==1'b1)begin

re = 'd0;

reb = 'd0;

eq = 'd0;end

else if(a>b)begin

re = 'd1;

reb = 'd0;

eq = 'd0;end

else if(a<b)begin

re = 'd0;

reb = 'd1;

eq = 'd0;end

else if(a==b)begin

re = 'd0;

reb = 'd0;

eq = 'd1;end

else begin

re = re;

reb = reb;

eq = eq;end

end

endmodule3.仿真测试

`timescale 1ns/1ns

module compare_8bit_tb();

reg i_clk;

reg i_rst;

reg [7:0]a,b;

wire re,reb,eq;

compare_8bit compare_8bit(

.i_clk(i_clk),

.i_rst(i_rst),

.a(a),

.b(b),

.re(re),

.reb(reb),

.eq(eq)

);

always #50 i_clk = ~i_clk;

initial begin

i_clk = 0;

i_rst = 1;

#200

i_rst = 0;

a = 8'd100;

b = 8'd25;

#300

a = 8'd3;

b = 8'd75;

#400

a = 8'd98;

b = 8'd98;

#200

$stop;

end

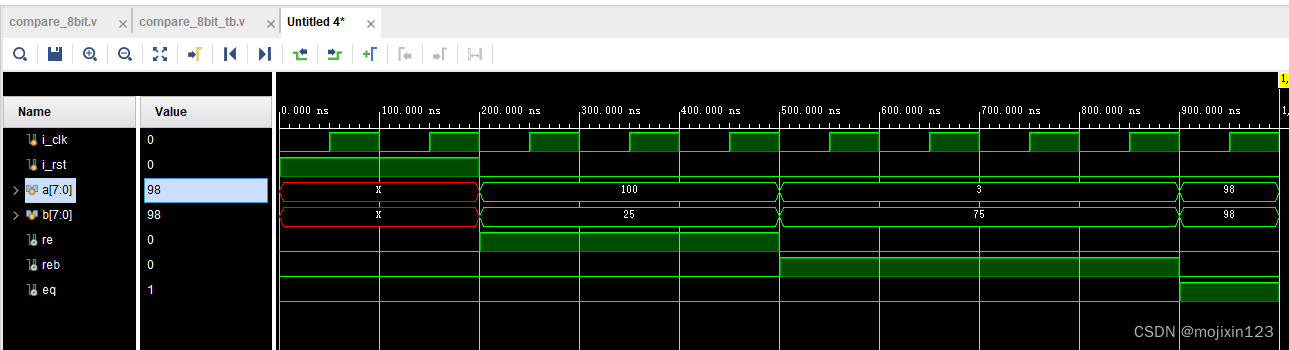

endmodule4、结果分析

输入都为8bit,200ns时,a=100,b=25,则re = 1; 500ns时,a=3,b=75,则reb = 1;

900ns时,a=98,b=98,则eq = 1;

979

979

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?