题目4:设计下图所示寄存顺序的环形计数器,异步复位,复位时计数器中的值为4’b0001。

1、设计方案

环形计数器的计数周期为2*WIDTH-1,例如8bit的寄存器计数周期为15。

寄存器cnt的初值为8’b00000001,首先采用位拼接运算符将cnt高位移到低位,然后采用一个寄存器count进行计数,当计数器count计数大于等于7时,也就是8‘b10000000时,再将cnt的低位移到高位,当计数器count计数到WIDTH*2-3时复位,然后循环此操作。

2、程序代码

module circular4_cnt #(

parameter WIDTH = 8

)(

input i_clk,

input i_rst,

output [WIDTH-1:0] ring_cnt

);

reg [WIDTH-1:0] cnt;

reg [WIDTH/2-1:0] count;

always@(posedge i_clk or negedge i_rst)begin

if(i_rst=='d1)begin

cnt <= 8'b00000001;

count<='d0;

end

else begin

if(count>=(WIDTH-1)&& count<(WIDTH*2-3))begin

cnt <= {cnt[0],cnt[WIDTH-1:1]};

count<=count+1;end

else if(count==(WIDTH*2-3))begin

count<='d0;

cnt <= {cnt[0],cnt[WIDTH-1:1]};end

else begin

cnt <= {cnt[WIDTH-2:0],cnt[WIDTH-1]};

count<=count+1; end

end

end

assign ring_cnt = cnt;

endmodule3、仿真测试

module circular4_cnt_tb;

reg i_clk;

reg i_rst;

wire [7:0]cnt;

circular4_cnt circular4_cnt(

.i_clk(i_clk),

.i_rst(i_rst),

.ring_cnt(cnt)

);

always #50 i_clk = ~i_clk;

initial begin

i_clk = 0;

i_rst = 1;

#200

i_rst = 0;

end4. 结果分析

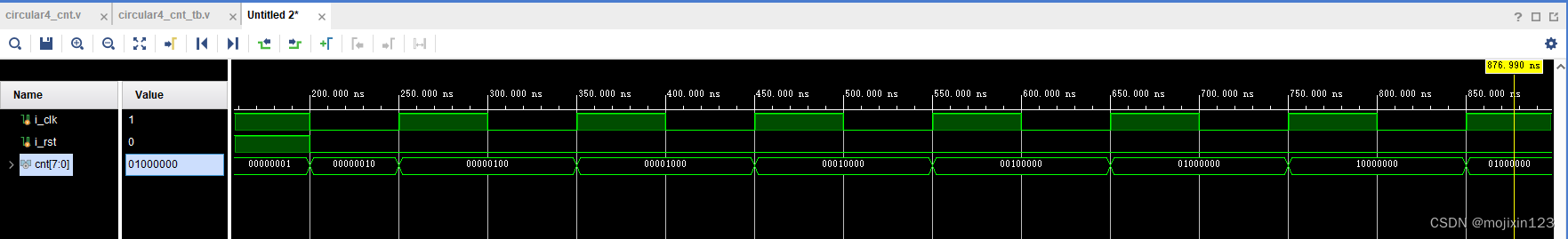

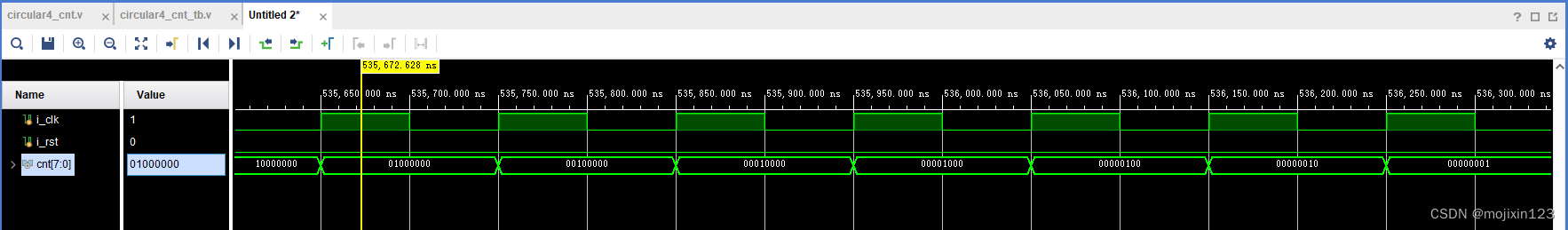

当复位为低时开始计数,从8’b00000001开始移位,00000010,00000100,00001000,00010000,00100000,01000000到8’b10000000,然后再移位01000000,00100000,00010000,00001000,00000100,00000010再到8’b00000001

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?