题目5:序列检测器

1、设计方案

2、程序代码

module sequential5_detector(

input i_clk,

input i_rst,

input i_seq,

output reg out

);

parameter idle = 5'b00000,

s1 = 5'b00001,

s2 = 5'b00010,

s3 = 5'b00100,

s4 = 5'b01000,

s5 = 5'b10000;

reg [4:0] i_buffe;

reg [4:0]current_state;

always@(negedge i_clk or negedge i_rst)begin

if(i_rst == 1'b1)begin

current_state <= idle;

out <=0;

i_buffe <=0;

end

else begin

case(current_state)

idle:begin

current_state<=s1;

out <=0;

i_buffe <=0;end

s1:begin

if(i_seq==1)begin

current_state<=s2;

i_buffe <={i_buffe[3:0],i_seq};end

else begin

current_state<=s1;

i_buffe <={i_buffe[3:0],i_seq};

end

end

s2:begin

if(i_seq==0)begin

current_state<=s3;

i_buffe <={i_buffe[3:0],i_seq};end

else begin

current_state<=s2;

i_buffe <={i_buffe[3:0],i_seq};

end

end

s3:begin

if(i_seq==0)begin

current_state<=s4;

i_buffe <={i_buffe[3:0],i_seq};end

else begin

current_state<=s2;

i_buffe <={i_buffe[3:0],i_seq};

end

end

s4:begin

if(i_seq==1)begin

current_state<=s5;

i_buffe <={i_buffe[3:0],i_seq};end

else begin

current_state<=s1;

i_buffe <={i_buffe[3:0],i_seq};

end

end

s5:begin

if(i_seq==1)begin

current_state<=s2;

i_buffe <={i_buffe[3:0],i_seq};end

else begin

current_state<=s3;

i_buffe <={i_buffe[3:0],i_seq};

end

end

default:current_state<=idle;

endcase

end

end

always @(negedge i_clk or negedge i_rst) begin

if(i_rst==1'b1)

out<=0;

else if(i_buffe==5'b10011)

out<=1'b1;

else

out<=0;

end

endmodule3、仿真测试

module sequential5_detector_tb;

reg i_clk;

reg i_rst;

reg i_seq;

wire out;

sequential5_detector sequential5_detector(

.i_clk(i_clk),

.i_rst(i_rst),

.i_seq(i_seq),

.out(out)

);

always #20 i_clk = ~i_clk;

initial begin

i_clk = 0;

i_rst = 1;

#60

i_rst = 0;

$stop;

#40

@(negedge i_clk) i_seq = 0;

@(negedge i_clk) i_seq = 1;

@(negedge i_clk) i_seq = 0;

@(negedge i_clk) i_seq = 1;

@(negedge i_clk) i_seq = 0;

@(negedge i_clk) i_seq = 0;

@(negedge i_clk) i_seq = 1;

@(negedge i_clk) i_seq = 1;

@(negedge i_clk) i_seq = 0;

@(negedge i_clk) i_seq = 1;

@(negedge i_clk) i_seq = 0;

@(negedge i_clk) i_seq = 0;

@(negedge i_clk) i_seq = 1;

@(negedge i_clk) i_seq = 1;

@(negedge i_clk) i_seq = 0;

@(negedge i_clk) i_seq = 0;

@(negedge i_clk) i_seq = 1;

@(negedge i_clk) i_seq = 1;

end

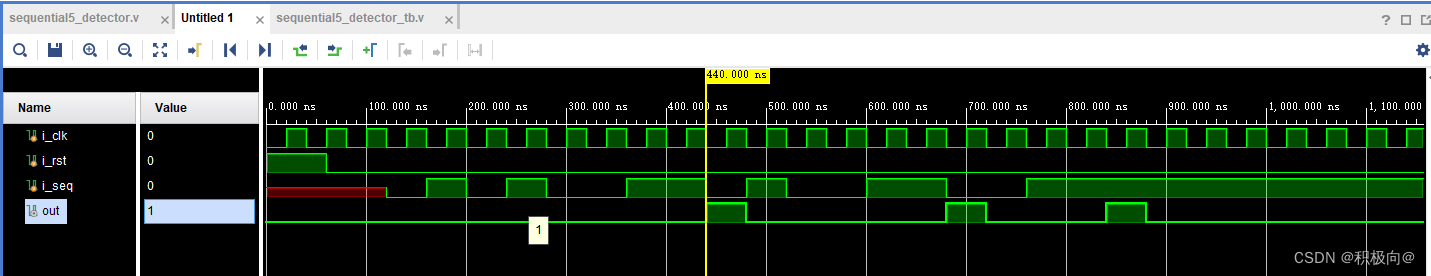

endmodule4、结果分析

当复位为0时,开始输入,当时钟上升沿到来时给输入,01010011时,最后是10011所以下一个时钟输出1。输入为010100110100110011,总共检测到三个10011,分别为01010011,输出1,01010011010011,输出1,010100110100110011输出1。

768

768

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?