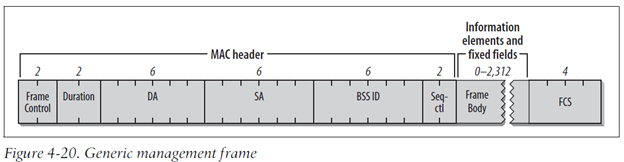

下面是普通WIFI management packet的格式,我们看到它有3个地址,但是Data frame有可能有4个地址。

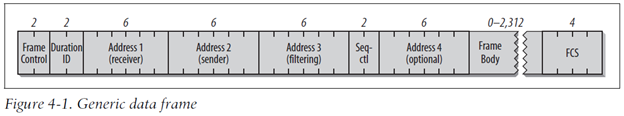

下面是普通WIFI data packet的格式,我们看到它有4个地址,其中前3个是必须的,第4个地址是可选的。

第4个地址只有WDS模式时用道。

WIFI data frame中4个地址的用法如下表。

下图是WDS结构,其中SA(Source Address), DA(Destination Address); TA(Target Address), RA(Receiver Address)。

1300

1300

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?