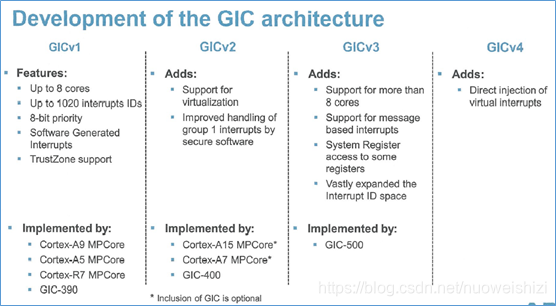

GIC,是arm为了实现复杂的中断控制,而定义的一套架构。版本也历经了多个变化,从最初的GICv1到现在最新的GICv4。每一个新的版本,都增加了一些新的功能。

目前最新的GIC-600 IP,支持GICv4。

不过从GICv3开始,架构就和之前的架构,变化就比较大了。

一、变化一:cpu interface

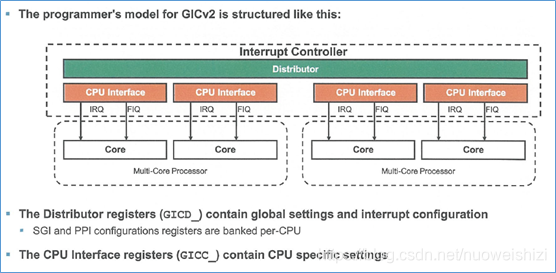

下图是GICv2架构,cpu interface是实现在gic内部,而且gic的寄存器,都是memory-mapped方式访问。

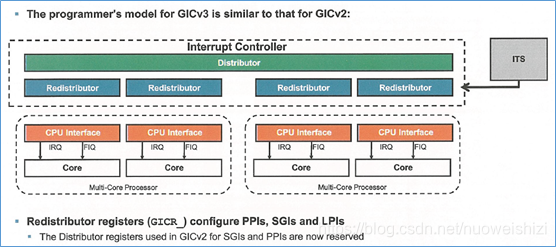

下图是GICv3架构,cpu interface从gic内部剥离,实现在PE的内部。并且将cpu interface的寄存器,提供了系统寄存器访问方式,从而实现中断的快速响应。

二、变化二:core的标识

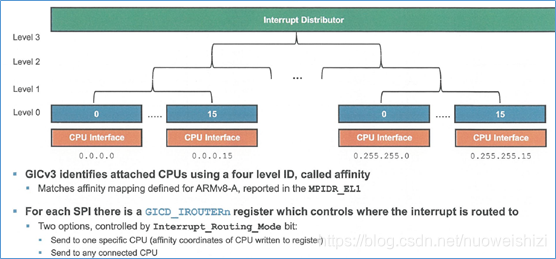

GICv3中,对于core的标识,使用了属性层次的方式,来进行标识,从而可以支持更多的core。

而GICv2中,支持最大8个core。

三、变化三:消息中断

GICv3中,加入了LPI中断类型,来实现消息中断。并且提供了ITS,来实现中断的转换。

四、变化四:SGI处理

对于SGI的处理,有如下的变化。

五、总结

gicv3/v4,架构,比gicv2架构,增加了很多的特性,从而支持更复杂的中断管理,支持更多的cpu。

自此,本系列博文到此就要结束了,基本上,除了虚拟中断的相关内容,我将GIC的内容都进行了介绍。希望大家看完这系列博文,能够对GIC有所认识。当初,自己也是看了很多的文档,外加上代码,才对这个理解的。

后面,如果我有去了解过虚拟中断,会在写一系列博文,来介绍虚拟中断。

原文首发于骏的世界博客

作者:卢骏.

本文介绍了ARM为实现复杂中断控制定义的GIC架构,其版本从GICv1发展到GICv4。从GICv3开始架构变化较大,如cpu interface从gic内部剥离到PE内部,core标识采用属性层次方式,加入LPI中断类型和ITS,SGI处理也有变化,能支持更复杂中断管理和更多CPU。

本文介绍了ARM为实现复杂中断控制定义的GIC架构,其版本从GICv1发展到GICv4。从GICv3开始架构变化较大,如cpu interface从gic内部剥离到PE内部,core标识采用属性层次方式,加入LPI中断类型和ITS,SGI处理也有变化,能支持更复杂中断管理和更多CPU。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?