在现代芯片设计中,功耗已成为衡量芯片性能的三大指标之一,尤其是在移动设备和物联网设备领域。为了满足这些应用场景对低功耗的需求,UPF(Unified Power Format)技术应运而生,成为低功耗设计流程中不可或缺的一部分。

UPF技术概述

UPF是一种标准化的低功耗设计格式,广泛应用于低功耗设计流程中。它定义了一套完整的低功耗设计规则和方法。它允许设计工程师通过编写UPF文件来定义和管理芯片的低功耗特性,如电源门控、隔离单元等。掌握UPF文件的编码方法、调试方法以及基于UPF文件的芯片物理实现和时序功耗分析流程,对于芯片设计工程师来说至关重要。

在UPF低功耗实现流程中,设计工程师需要掌握一系列关键技能。

首先,他们需要了解如何编写UPF文件,这是实现低功耗设计的基石。

其次,工程师必须熟悉Cadence和Synopsys等EDA工具的低功耗设计流程,这些工具提供了从设计到验证的全套解决方案。

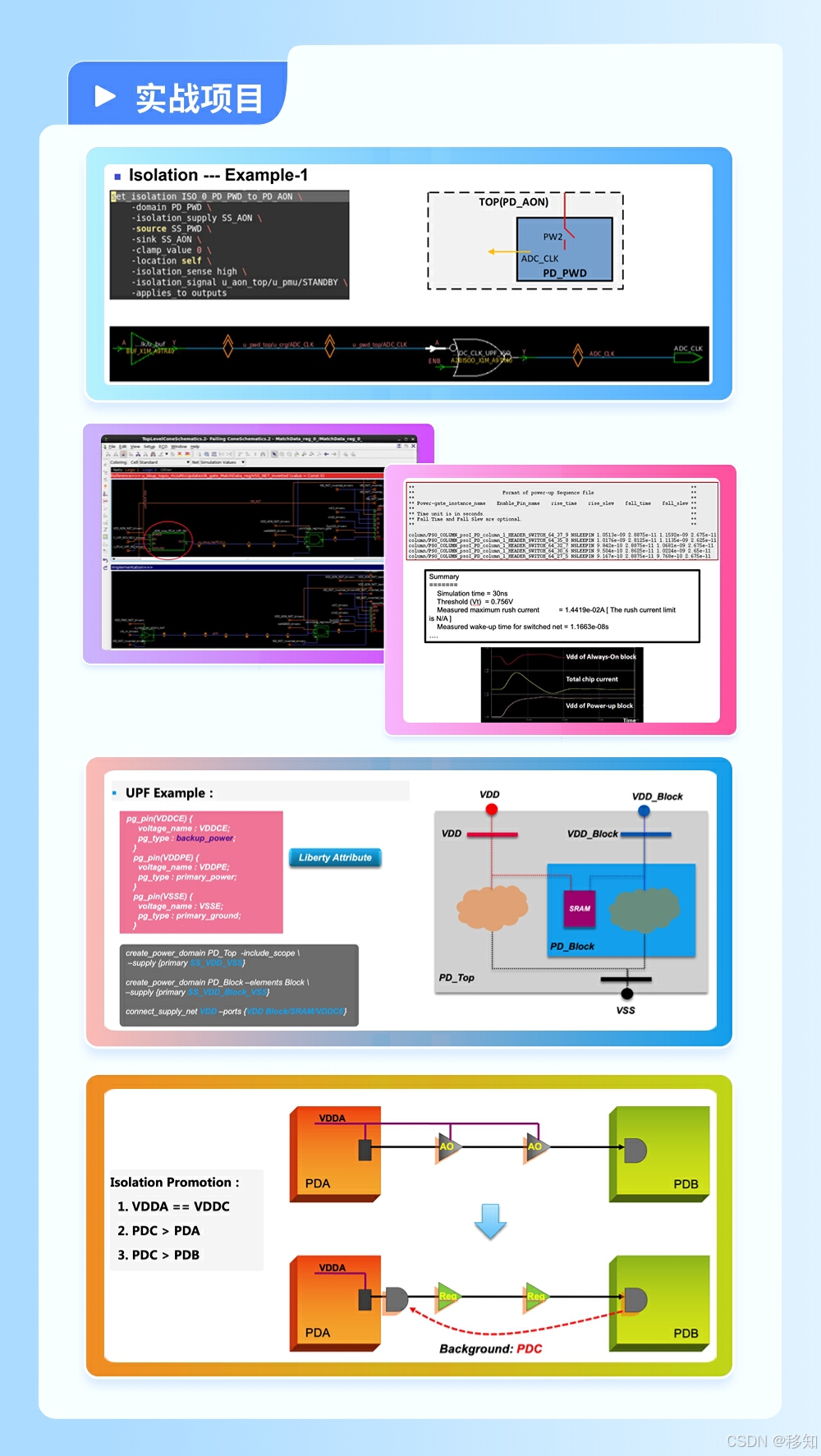

此外,对于电源网络的编码、电压域的划分、低功耗单元的使用,以及层次化设计的编码等技术细节,工程师也需要有深入的理解和实践。

UPF低功耗实现流程

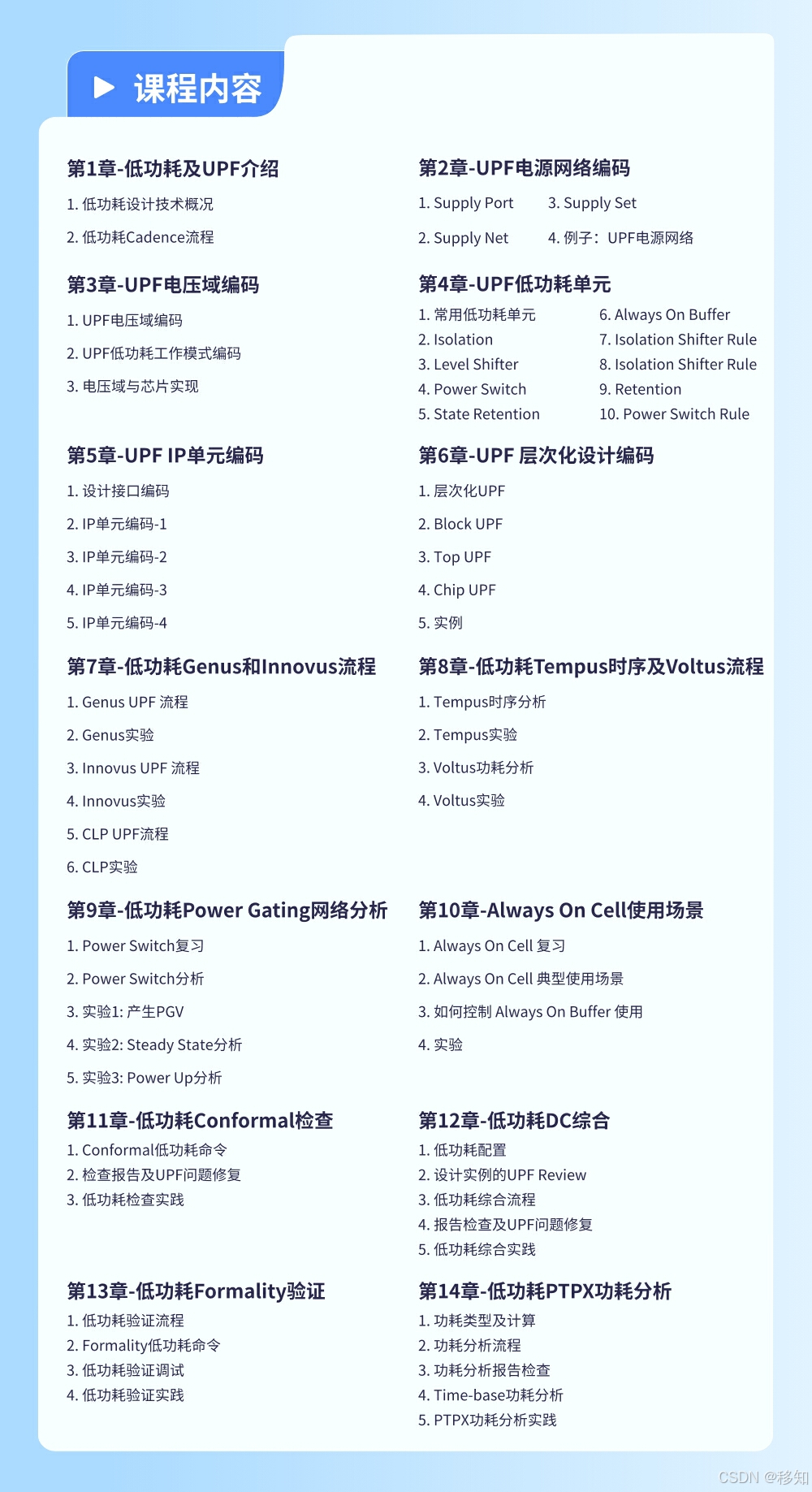

《UPF低功耗实现流程》涵盖了从设计到验证的各个阶段,包括电源网络编码、电压域编码、低功耗单元的使用、层次化设计编码等关键步骤。通过掌握这些流程,工程师能够更有效地控制和管理芯片的功耗,从而设计出性能优异且能效比高的芯片产品。以及如何通过Cadence和Synopsys工具来掌握这一关键技术。

低功耗设计是芯片设计中的一个重要领域,而UPF技术则是实现低功耗设计的关键工具。移知的UPF低功耗实现流程课程,为广大芯片设计工程师提供了一个全面、系统的学习平台。

无论您是芯片设计的新手,还是希望进一步提升技能的资深工程师,本课程都将为您提供宝贵的知识和实践经验。我们的资深讲师团队,凭借丰富的行业经验和项目实战,将引导您一步步走进低功耗设计的大门。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?