使用并行扩频序列的100 Gbps无线系统与电路设计

1 引言

使用毫米波到太赫兹频率范围内的载波频率进行无线通信,对于高速数据应用正变得越来越重要。这些频率上可用的高带宽使得即使采用相对较低的频谱效率也能实现非常高的数据速率,例如在[1]中使用的240 GHz无线系统通过使用8-PSK调制,已实现了96 Gbps的通信链路。尽管低频谱效率在某些方面可能简化系统设计,但显然对于100 Gbps而言,将需要极高的基带带宽,这要求发射机中使用超高速数模转换器(DAC)和接收机中的模数转换器(ADC)[1]。此外,即使频谱效率较低,100 Gbps所需的信号处理量也将非常巨大。在传统100 Gbps射频(RF)接收机中,经过模数转换后,我们必须经过一系列数字信号处理阶段,包括同步、均衡、检测、纠错等。预计所需的数字信号处理性能将达到数百千兆浮点运算每秒(GFLOPS)的量级。同时,该系统的能耗也将相当显著。

并行扩频序列(PSSS)如[2]所述,有望成为解决上述问题的一种可行方案。它基于直接序列扩频技术,并结合正交码分复用,以实现更高的数据吞吐量。目前,PSSS主要用于在ISM频段运行的低功耗、低成本和低速率应用,例如家庭和工业自动化、无线传感器网络以及医疗数据采集。2006年,PSSS被纳入IEEE 802.14.5无线个人区域网络(WPAN)标准,从而引入了主要工作在868至915 MHz和2450 MHz频率的Zigbee标准。在[3]中,已实现并演示了一款60 GHz PSSS WLAN收发器。链路实验表明,其在数据速率、频谱效率和传输距离方面的性能与60 GHz正交频分复用(OFDM)收发器[3]相当。与OFDM相比,PSSS非常适用于模拟信号处理。我们在超宽带无线收发器方面的研究基于以下假设:在基带中重新划分数字/模拟信号处理,更加侧重于模拟处理,有望在功耗、复杂度和成本方面优于纯数字基带处理器。例如,假设基带带宽为25 GHz,频谱效率为4 bits/s/Hz,为实现100 Gbps的目标数据速率,需要采用PAM-16调制方式,无论是数字还是混合信号基带处理器均需在接收机基带中使用4位ADC。在传统的数字基带架构中,4位ADC需要以至少50 GHz的采样率处理25 GHz的输入基带信号;而在混合信号PSSS基带架构中,4位ADC所需的采样率和带宽均有所降低(采样率和带宽的降低程度取决于所用码的码长)。如第2.3节中将进一步解释的,当前系统采用码长为15,使ADC的采样频率降低了15倍,即每个并行的15个ADC输入端的采样频率为1.66 GHz,同时输入信号的带宽也大大降低(ADC获取的是相关器电路中积分器的采样输出)。

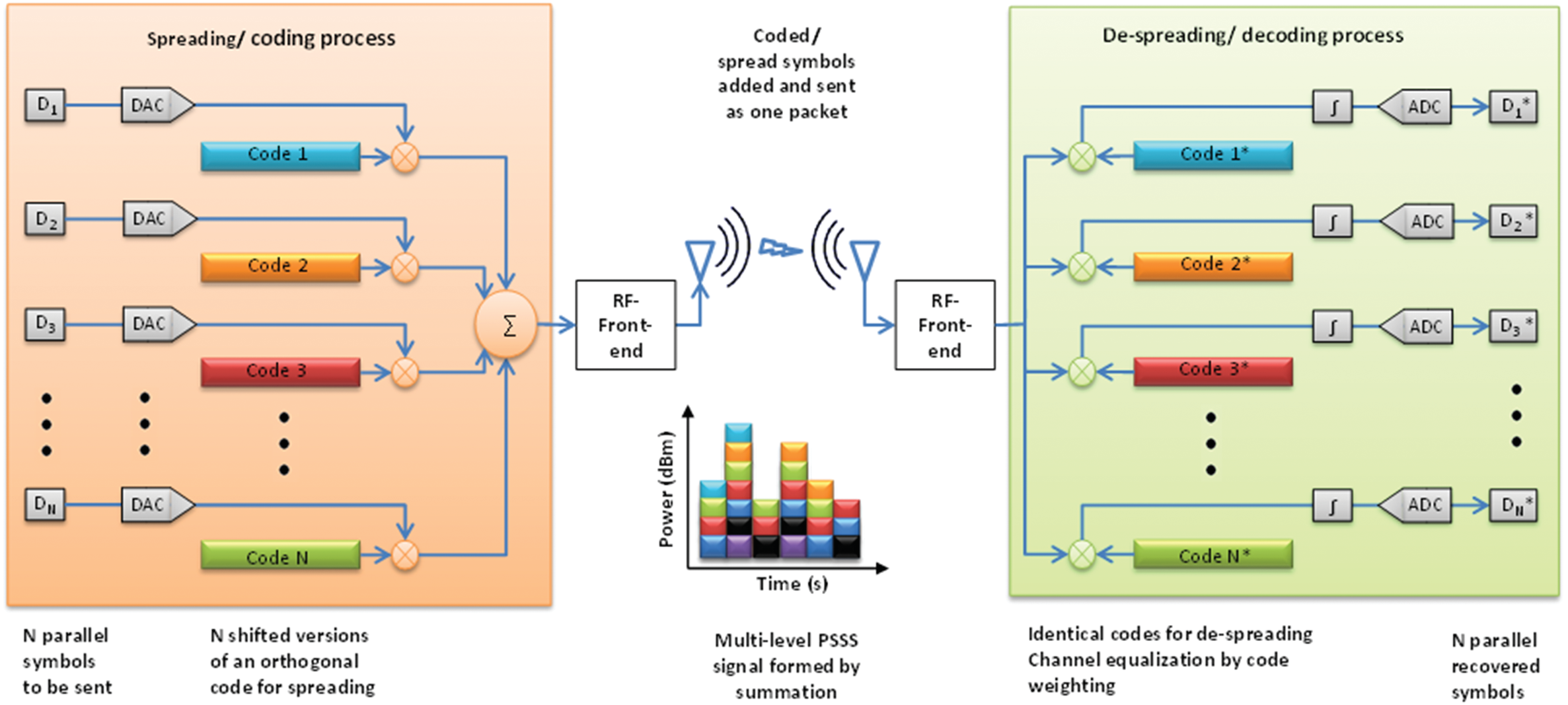

图1展示了PSSS发射机和接收机的基本概念。在PSSS发射机中,N个并行符号D1到DN被N个正交PSSS码编码,并累加为一个单一的量化PAM信号。这些信号被上变频至射频,通过无线信道传输,然后再次下变频至基带。在接收机中,信号与N个先验已知PSSS码进行互相关,以恢复符号D1到DN。发射机中的完整扩频/编码过程以及接收机中的解扩/解码过程,可以利用高速模拟电路(如模拟乘法器、加法器和积分器)在模拟域中非常高效地实现。除了高速和低晶体管数量外,混合信号实现的另一个重要优势是降低了速度要求。数据转换器的要求。在图1所示的混合信号PSSS基带中,采用N路并行DAC和ADC,其采样频率等于相对较低的符号速率。相反,在全数字PSSS收发机中,DAC和ADC需要处理编码后的PSSS信号,即采样频率至少为PSSS信号带宽(码片速率)的2倍,而码片速率是符号速率的整数倍。因此,数据转换器的带宽要求大大降低。

混合信号PSSS收发机的另一个优点是,可以在解扩/解码过程中实现对接收信号的自适应均衡[3],即基于相关性的均衡。这种基于相关性的均衡非常有吸引力,因为它可以实现为一种混合信号均衡器,能够在单一步骤中完成扩频解码和均衡。

本文组织如下:在第2节中,介绍了包括PSSS系统的通用描述、系统模型以及主要系统参数确定在内的整体系统设计。接着在第3节中,讨论了PSSS发射机和接收机基带的混合信号实现的设计考虑。本小节还给出了最关键的电路——超宽带积分清零相关器的实现结果。在第4节中,讨论了具有极高载波频率的射频同步系统的挑战,并提出了相应的解决方案并进行了研究。同时展示了初始电路测量结果,例如用于宽带Costas环的超宽带相关器的结果。在第5节中,讨论了使用240 GHz射频前端和硬件在环实验室设置进行PSSS系统演示的结果。最后对结果进行了总结。

2 系统设计

下一节将讨论基于PSSS的无线通信链路的系统级设计方面以及当前设计的具体参数。

2.1 数学概述

2.1.1 PSSS - 编码与解码

基于PSSS的通信系统使用N个正交码并行编码N个符号。PSSS通信系统中使用的正交码可以是单独的正交码,例如最长序列(MLS或m序列)、巴克码或沃尔什码等,也可以是这些码的循环移位版本。在基于PSSS的系统中,通常使用m序列。公式(1)描述了基本正交码(例如m序列)ms1,如下所示:

$$

ms1 = \left(m_{11}, m_{21}, …, m_{M1}\right)^T \quad (1)

$$

完整的编码矩阵EN(见公式(2))通过添加N个正交码构成,这些正交码类似于公式(1)中给出的码。以下的编码矩阵包含基码ms1的循环移位版本

$$

E_N =

\begin{bmatrix}

m_{11} & m_{12} & \cdots & m_{1N} \

m_{21} & m_{22} & \cdots & m_{2N} \

\vdots & \vdots & \ddots & \vdots \

m_{M1} & m_{M2} & \cdots & m_{MN}

\end{bmatrix}

\quad (2)

$$

D是表示N个数据比特的列向量,如公式(3)所示,其中N等于所用正交码的长度,例如,对于由具有m个寄存器的线性反馈移位寄存器(LFSR)生成的m序列,N = $2^m - 1$。

$$

D = \left(d_1, d_2, …, d_N\right)^T \quad (3)

$$

在编码过程中,数据向量D与EN相乘,得到多电平PSSS符号向量S,如公式(4)所示。

$$

S = E_N \cdot D \quad (4)

$$

PSSS符号解码可以通过对接收到的PSSS符号向量S与编码矩阵EN中的N个正交码msi进行循环互相关(CCC)来实现,即对每个正交码msi分别与S进行相关运算,从而得到N个符号的数据。该操作类似于将解码矩阵DE(如公式(5)所示)与PSSS符号向量S相乘,结果如公式(6)所示。注意,解码矩阵DE是编码矩阵的转置。这两个矩阵可以独立地选择为单极性${0, 1}$或双极性${-1, +1}$,甚至可以具有直流偏移。

$$

D_E = E_N^T \quad (5)

$$

$$

CCF = S \cdot D_E \quad (6)

$$

CCF是一个向量,表示PSSS符号S与解码矩阵DE之间的循环互相关。数据比特重建通过公式(7)中所述的阈值判决完成。

$$

d’_n(\text{ccf}_n) =

\begin{cases}

d’_n = 0; \leq (0) \

d’_n = 1; > (0)

\end{cases}

\quad (7)

$$

$d’_n(\text{ccf}_n)$是选择等于零的阈值时重建的数据比特。对于更高的比特负载或复杂数字调制(即每符号比特数更高),上述简单的判决阈值将扩展为具有等于比特负载的最小分辨率的模数转换器。

2.1.2 信道均衡

我们定义一个有效信道,该信道包含由物理信道和射频前端电子器件引起的损伤。信道去卷积是补偿信道损伤和射频损伤的过程。H表示时域中的信道响应。PSSS符号S与信道响应H进行卷积后得到G′,即接收到的PSSS符号,如公式(8)所示,其中#表示时域中的循环卷积。

$$

G’ = S # \tilde{H} \quad (8)

$$

$ms_{-1}^1$是公式(1)的时间反向序列,用作相关参考。CCF′是G′与$ms_{-1}^1$的循环卷积。如公式(9)所评估的CCF′未补偿多径效应和射频损伤损耗。

$$

CCF’ = G’ # \tilde{ms}_{-1}^1 \quad (9)

$$

$H^{-1}$是时域中的逆信道响应,将其与$ms_{-1}^1$进行卷积,我们得到作为新的相关参考的$ms_{-1, \text{new}}^1$,如公式(10)所示。

$$

ms_{-1, \text{new}}^1 = H^{-1} # \tilde{ms}_{-1}^1 \quad (10)

$$

循环互相关函数$CCF’ {\text{new}}$是G′与$ms {-1, \text{new}}^1$的循环卷积,如公式(11)所述。根据公式(11)的评估,可补偿循环互相关函数$CCF’_{\text{new}}$的多径效应和射频损伤损耗。

$$

CCF’

{\text{new}} = G’ # \tilde{ms}

{-1, \text{new}}^1 \quad (11)

$$

因此,循环互相关函数$CCF’ {\text{new}}$用于通过阈值判决重构数据比特,如公式(7)所述。新的解码参考$ms {-1, \text{new}}^1$仅需在信道变化时进行计算,即计算速率大于或等于信道相干时间的倒数。

2.2 系统设计参数

基于PSSS的数据通信系统中一个重要的系统级决策是所用正交码的类型和长度。最长序列(MLS或m序列)通常被用作PSSS的正交码[3–5],但其他正交码如巴克码等可能更适用于混合信号实现,如下文各小节所述。无论选择何种正交码,单极性${0, 1}$或双极性${-1, 1}$形式的数据、编码和解码序列的组合都会产生不同的PSSS和循环互相关(CCC)结果值集合,从而为系统设计提供一定程度的自由度。

2.2.1 正交码的选择

在接下来的讨论中,码长将与码的名称一起写出,例如码长为7的MLS将写作MLS-7等。该码MLS的长度为N = $2^m - 1$,其中m ≥ 3,而巴克码的码长为2、3、4、5、7、11或13。较短的码实用性不高,且Barker-7与MLS-7相同,因此值得关注的巴克码是Barker-11和Barker-13。表1列出了任意长度为N的MLS对应的PSSS电平最大数量、循环互相关(CCC)值以及积分器输入动态范围。对于Barker-11和Barker-13,为了将其用于PSSS,需要对解码序列进行均值偏移(直流偏移)。Barker码所需的直流偏移及其对应的PSSS电平、CCC值以及积分器输入动态范围列于表2中。从表中可以看出,单极性编码序列与双极性解码序列组合,或反之亦然,会产生双值的循环互相关(CCC)结果。

PSSS幅度集合的幅度分布在所有情况下均呈现高斯分布,然而对于单极性数据,PSSS幅度集合的均值为非零。此外,在PSSS幅度集合元素数量相同的情况下,双极性数据的CCC值之间的差值是单极性数据的两倍,这使得双极性数据优于单极性数据。在采用双极性数据的两种方案中,使用单极性编码序列与双极性解码序列的方案生成的PSSS幅度集合(数量上)最小,从而对发射机电路的线性度要求最低。

PSSS幅度集中的元素数量越少,达到所需误码率(BER)所需的信噪比(SNR)要求就越低,性能越好,发射机的峰均功率比(PAPR)就越低。因此,对于所讨论的无线通信链路中的混合信号PSSS收发器,最佳组合将是使用双极性数据、单极性编码序列和双极性解码序列的方案。

混合信号基带设计的另一个重要考虑因素是模拟积分器和相关器电路的线性度。积分器输入是输入PSSS流与(加权)解码序列的乘积。表1和表2显示了不同编码序列及其组合下的积分器输入动态范围。这些值是通过对所有可能的PSSS向量与一个解码序列相乘得到的。从表1可以看出,采用单极性编码序列和双极性解码序列的双极性数据对积分器及转储相关器电路的线性度要求最低,因此是用于基于PSSS[6]的无线通信链路的混合信号基带实现中最合适的组合。

2.2.2 码长

码长越长,处理增益(定义为符号长度Ts与码片长度Tc之比,即Ts/Tc)越大,可并行传输的符号数量也越多。使用较长码的另一个优势是链路利用率得到提升,如下一小节所述。然而,对于混合信号实现而言,从一个MLS迁移到下一个更长的MLS会导致晶体管数量和整体芯片尺寸大致翻倍。因此,对于码片速率约为25 Gcps的混合信号实现,PSSS优选的正交码序列(就码长而言)为MLS-7、MLS-15或长度为7、11或13的巴克码。

2.2.3 保护间隔长度

PSSS块是由数据流中每个符号经其对应的编码序列编码后生成的多值码片流之和,并添加一些用作保护间隔的额外码片构成。保护间隔可通过零填充或循环前缀实现。这两种形式的保护间隔均有助于消除PSSS流中相邻块之间的符号间干扰(ISI),然而,若采用循环前缀实现,则可使频域上的线性卷积变为选择性多径信道表现为循环卷积,这是PSSS的基本要求。

循环前缀的长度由多径无线信道的时延扩展以及有线信道的接口阻抗失配和带宽限制(或群延迟色散)决定。对于给定的码长,保护间隔越短,链路利用率越高(定义为用于有效载荷数据的信道容量与用于有效载荷数据加上在保护间隔期间浪费的信道容量之比)。如果码长与保护间隔之和(以芯片数衡量)为二进制数,则具有优势,即发射机和接收机电路中的时钟和数据信号分配路径可以实现为二叉树,从而允许每个节点处的对称布局和等长路径。

2.3 系统模型和规格

2.3.1 系统模型

基于PSSS并采用混合模拟/数字信号处理的通信系统框图如图2所示。系统研究[3, 4]表明,PSSS是实现100 Gb/s速率的合适候选方案,尤其是在混合信号基带实现中,大部分信号处理在模拟域(红色框)完成。

PSSS利用时域中的正交性,类似于OFDM在频域中所采用的方式。与OFDM符号的生成相比,PSSS序列在发射机中的生成更为简单,因为它不需要进行IFFT(逆快速傅里叶变换)计算。如[6]中所述,针对高速无线通信的模拟-混合信号基带实现在多个方面具有优势。与数字基带实现相比,混合信号实现得益于更简单的硬件、更小的芯片面积以及更好的能效。PSSS非常适合混合信号实现,因为在发射机中对并行数据符号的编码及其组合成多值PSSS流、在接收机中对符号的解码,甚至信道均衡都可以通过模拟/混合信号电路来实现。

信道均衡的加权系数通过低速数字硬件进行计算和应用。假设信道相干时间远大于符号持续时间,则使用低数据速率的数模转换器来实现解码的自适应系数。因此,在混合模式模拟/数字设计中,接收机架构得以简化,因为信道估计和均衡也是如[3]中所述的简单的模拟互相关操作。PSSS信号通过MILLILINK项目开发的射频前端收发器[1]在空中传输。为了恢复传输的数据比特,PSSS系统需要一个相干接收机,以提供同步PSSS基带信号。同步在模拟域中使用科斯塔斯环进行,如图2所示。

2.3.2 系统规格

在发射机端,比特流被并行化,并使用正交码进行编码。当前的混合信号基带实现采用长度15的m序列作为基本正交码。15 × 15编码矩阵通过级联基本m序列的移位版本获得。输入数据流经过预编码/成帧模块,以降低发射机中功率放大器对峰均功率比(PAPR)的要求。PSSS编码的数据流附加了3个码片的循环扩展,以减少相邻PSSS块之间的ISI效应。

数据流在使用正交码进行编码之前采用脉冲幅度调制(PAM)。为了在240 GHz频段利用MLS-15编码矩阵通过PSSS实现100 Gbps的目标数据速率,需要更高的数字调制复杂度。50 GHz双边带射频带宽对应25 GHz基带带宽,这将最大码片速率限制在约25–30 Gcps。采用25 Gcps的码片速率用于PSSS编码需要至少4 bits/s/Hz的频谱效率,以实现100 Gbps的目标数据速率。编码后的序列附加了最多3个码片的保护间隔(以循环扩展的形式),以减少相邻PSSS块之间的ISI(符号间干扰)效应。链路利用率降低至83.33%。为了弥补链路利用率的损失,码片速率被提高到30 Gcps。3 × Tchip的保护间隔对应100皮秒。该时间也被积分电路用于复位自身,为下一个PSSS输入块做准备。通过对单个PSSS编码数据流进行求和得到的PSSS块,形成一个离散的多幅度信号,其长度等于所选PSSS编码矩阵的长度。PSSS信号可被视为具有双边带调制的高阶PAM信号。

2.3.3 信道均衡

自适应信道均衡根据以下方案实现,并在概念上如图2所示。假设采用基于帧的架构,在发射机侧,输入数据流被组织成数据帧。在每个帧的开始,发送一个训练序列,用于信道估计和均衡。在训练序列之后,是一系列PSSS编码的有效载荷数据流。对于训练序列数据的解码,使用理想无权解码序列。随后,对有效载荷数据使用加权解码序列。解码序列的权重通过对接收到的训练序列进行解码所获得的信道估计来计算。训练序列由所有经过信道失真的(循环移位的)编码序列组成。码片权重通过数字硬件对接收的训练序列数据进行矩阵运算来计算(参见图2,绿色框)。在基于帧的系统中,码片权重的计算仅在帧开始时执行,但可以根据固定时间间隔进行重新计算,或在链路性能下降时请求重新计算。权重计算的更新速率取决于无线链路特性。假设为室内视距链路且无干扰,如[6]所述,温度和湿度变化不大,意味着信道具有较长的相干时间。在这种情况下,由于很少需要请求重新计算码片权重,帧长度可以非常大。

3 混合信号发射机和接收机设计

下文将讨论发射机和接收机基带,重点介绍其电路级实现。

3.1 发射机基带架构

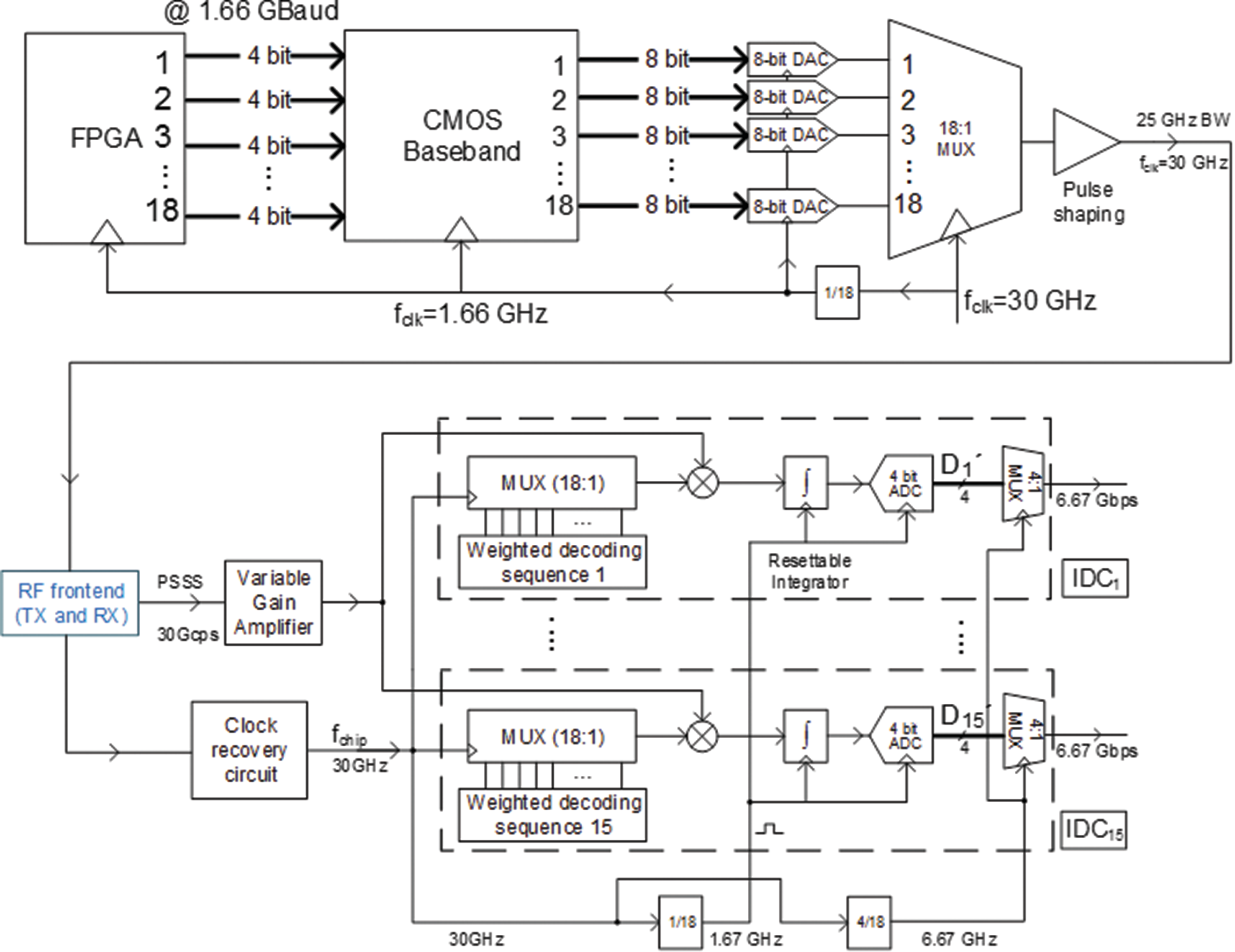

在[6]中讨论了一种混合信号无线收发机的架构,并解释了与数字收发器设计相比,混合信号实现如何减少晶体管数量和电路复杂度。该架构在[6]中采用混合信号方法,其中N个符号通过使用异或门与循环移位的正交码相乘而并行扩频(其中N ≤码长)。扩频后的符号经过各自的脉冲成形滤波器后,通过电流求和放大器(CSA)进行相加。CSA的带宽和线性度是一个非常重要的电路设计参数,因为它对链路性能有显著影响。另一种方法(如图3所示)是在数字域中完成大部分基带处理,包括扩频过程,然后使用数模转换器(DACs)生成电流信号作为宽带高速多路复用器(MUX)的输入。在这种情况 下,模拟多路复用器的线性度和带宽将成为最重要的设计参数。多路复用器的输出连接到脉冲整形放大器,以改善输出波形的形状,然后再将信号送至发射机射频前端。

3.2 接收机基带架构

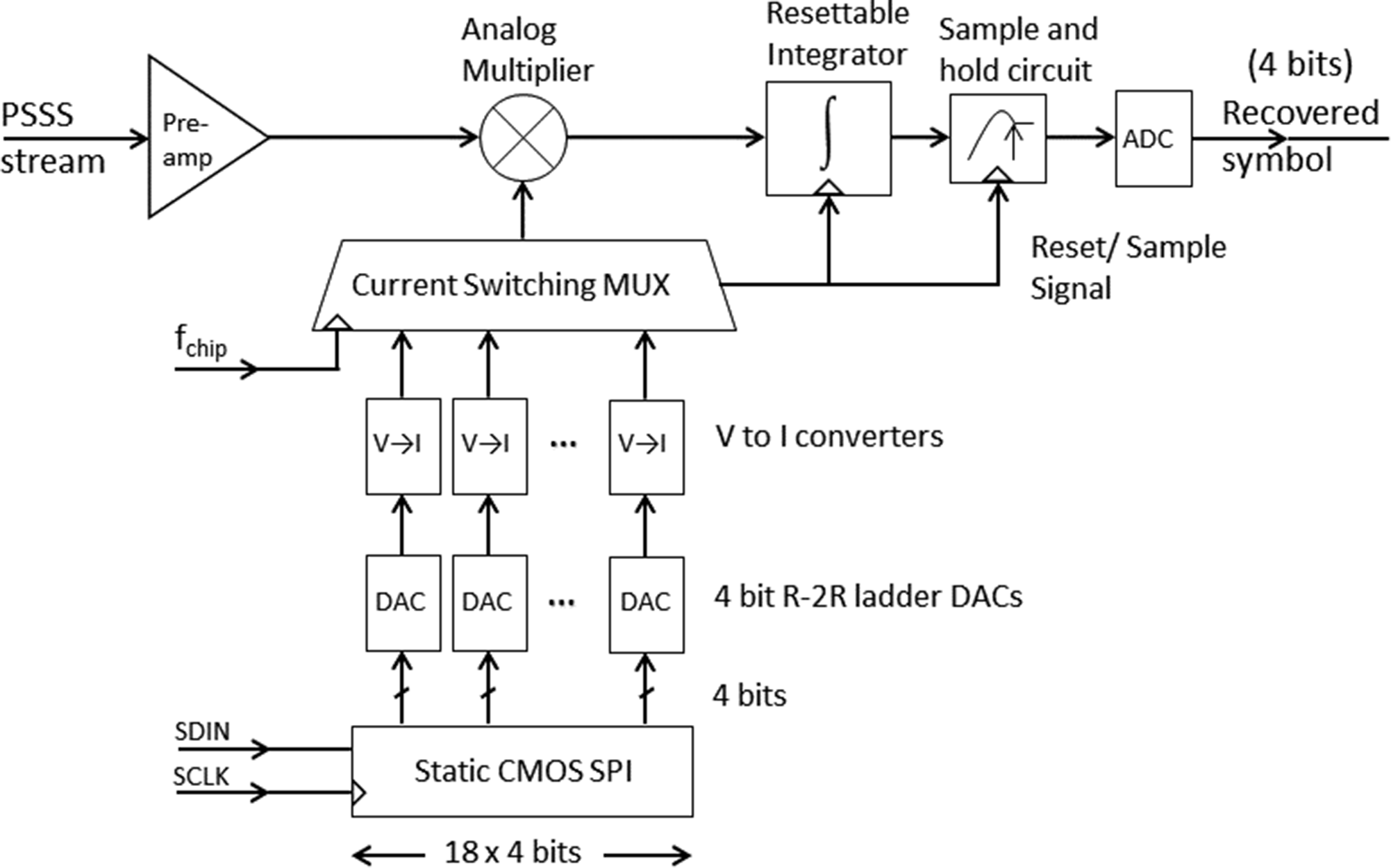

在接收端,基带中最关键的电路是模拟积分清零相关器(IDC)电路。每个传输的符号都需要一个独立的IDC电路来执行相关和检测,因此总共需要N个并行的IDC电路,如图3所示。

单个IDC电路的框图如图4所示。模拟多路复用器的输入为直流电流信号而非电压,因为长走线的直流电阻可能导致显著的电压降,并且电压信号可能从附近走线拾取大量噪声[6]。与发射机相比,该多路复用器的设计要求大大放宽,因为在接收机中,MUX的输入是固定直流信号,而发射机情况下的输入则是在符号速率下切换的可变信号。对于接收机MUX,其输入为解码序列权重,这些权重保持固定,直到由于链路性能下降等原因需要进行权重的重新计算,并可通过低速SPI接口存储,该接口驱动N个4–6位R-2R梯形数模转换器(分辨率取决于码片权重计算所需的精度级别)。数模转换器的电压输出通过电压-电流转换器(例如差分射极耦合对电路)转换为电流信号。MUX电路在码片速率(fchip´)下将N个电流信号之一转发至输出端,并使用模拟乘法器(例如吉尔伯特单元乘法器)与输入PSSS流相乘。一个快速线性宽带可复位积分电路对乘法器的输出进行积分,在持续N × Tchip的积分周期结束时,产生对应于PSSS流与加权解码序列之间互相关结果的信号。在末尾处,ADC之前设有采样保持电路。该采样保持电路的动态范围应与最终积分器输出(而非运行时积分器输出)相匹配,并应表现出极小的衰减。模数转换器仅需在符号速率即fchip=N下工作,其分辨率等于比特负载,即每符号比特数。

3.2.1 宽带模拟相关器电路

积分清零相关器电路的关键核心组件是宽带模拟相关器。四象限乘法器电路通过使用吉尔伯特单元实现,其两个输入均经过线性化处理,以确保至少工作到700 mVdiff。对于上述使用30 Gcps码片速率且保护间隔长度为3 × Tchip的100 Gbps PSSS基带电路,积分器的复位时间将被限制为3 × Tchip,即100皮秒,其中Tchip = 1/30 Gcps = 33.33 ps。此外,相关器电路应能够处理带宽约为24 GHz的信号。另外,由于接收机基带是在130纳米SiGe BiCMOS技术中设计的,该技术不提供任何PNP晶体管,因此额外的约束是仅使用NPN晶体管进行设计[7]。

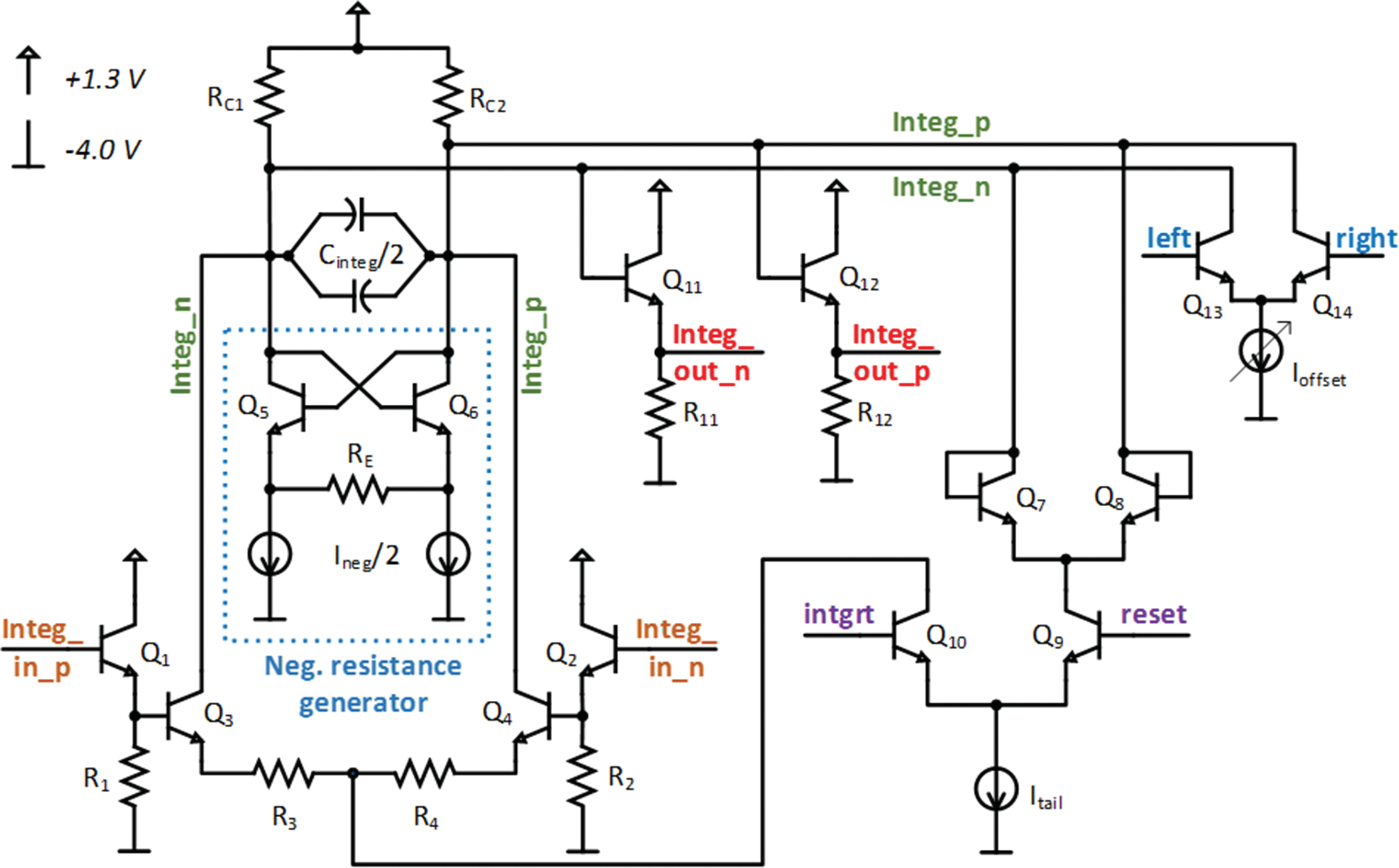

3.2.1.1 电路设计

为了表征相关器电路的性能,制造并测试了一款测试芯片。该电路采用双电源供电,即+1.3 V和-4伏特。宽带积分器仅使用NPN晶体管实现。它采用负阻生成电路,并通过交叉耦合晶体管构成,如图5中虚线框所示。此外还增加了快速复位电路和手动偏移校正电路。积分器需要具有高线性度,并在下一次积分周期开始前支持快速复位操作。

RC积分电路的线性度取决于其RC时间常数。在积分阶段,RC时间常数需要非常大,而在复位阶段则应足够小,以实现快速放电。这两个阶段中所需的RC时间常数变化是通过切换RC谐振负载的电阻实现的,同时在积分和复位阶段保持电容不变。在积分阶段,通过将负电阻与RC负载并联(即R(C1+C2) × integ)来获得所需的大阻值。该负电阻的幅度设计得与正电阻非常接近,从而在积分电容上形成一个非常大的等效电阻。该负电阻由交叉耦合的差分对Q(5,6)Q提供。通过发射极退化电阻R(E)来调节负电阻的值,使其等于主差分对的集电极电阻R(C1+C2)R。积分器的最大输出电压受限于交叉耦合对管Q(5,6)Q的基极到集电极电压;因为当该电压增大到较大值时,两个晶体管中的一个或另一个会进入饱和状态。此外,交叉耦合对产生的负电阻是其两端差分电压的函数,因此在大输出幅度下会改变积分器的有效RC常数。因此,积分器的最大输出幅度被限制在大约360 mVdiff。

在复位操作期间,积分电容(Cinteg)的两个端子通过电流开关连接到低阻抗放电路径Q(7−9)Q。当晶体管Q9被复位信号导通时,晶体管Q7, Q8作为二极管工作,迫使节点Integ p和Integ n的电压相等,从而导致Cinteg放电。注意,在复位和积分阶段,节点Integp和Integ n的共模电压保持不变。

添加了一个手动偏移校正电路,用于校正积分器电路Q(13,offset)14,QI中的任何制造后偏移误差。该电路允许控制偏移校正的幅度和符号。此外,在积分核心的输入端Q(1,2)Q和输出端Q(11,12)Q均添加了射极跟随器级作为缓冲器。电流源Ineg=2采用电流镜实现,其值可以外部调整以使负电阻的值与集电极电阻R(C1+C2)R的值相匹配。

3.2.1.2 工艺与布局

该电路采用IHP微电子有限责任公司提供的130纳米锗硅 BiCMOS工艺制造。这是一种自对准单多晶硅技术,具有130纳米最小光刻发射极宽度和七层铝金属化层(5层薄金属层和2层厚金属层)。位于堆叠上层的较厚金属层用于高频互连和传输线结构。金属-绝缘体-金属(MIM)电容对以交叉耦合方式连接,使电容两端具有相同的电容值。该工艺中的异质结双极型晶体管(HBT)的fT和fmax分别为250吉赫兹和300吉赫兹[8]。电路布局采用对称设计,以最大限度地减少共模效应。

3.2.1.3 测量与结果

在测量过程中,该芯片通过引线键合连接到高速(Isola Astra)印刷电路板(PCB)基板上。为了缩短键合线的长度,将芯片放置在PCB上的一个腔体中,该腔体与PCB底面的接地平面短接。芯片上所有高频输入/输出焊盘的接地连接均通过引线键合连接到腔体周围的接地环,以降低片上与片外接地之间的电感:首先,与非接地走线的键合线连接相比,显著缩短了键合线长度;其次,如图6所示,将多个接地键合线并联连接。由于放置在腔体中的芯片高度几乎与PCB本身相同,因此回路高度以及信号连接的键合线总长度被最小化。

使用快速比特模式发生器(BPG)(SHF 12,103 A)向测试芯片施加高速非归零(NRZ)差分输入信号(乘法器两个输入端的m序列以及积分器的复位信号)。该BPG允许在其各输出之间进行精确的相位调节,最大调节范围达±25 ps,分辨率为0.1 ps。相关器电路的差分输出通过高带宽数字采样示波器(Keysight DCA-X 86100D)的两个单端输入进行测量。进行了以下测试以表征相关器电路的性能。

如果相关器的两个输入是具有零时间偏移的相同m序列,则会观察到对应于斜坡输出的相关峰值。如果两个m序列中的一个被移动了1个或更多比特,则输出为两个m序列无时间偏移时输出的-1/N倍;其中N是所用m序列的长度。在当前实现中,两个输入均使用长度15的m序列,即f1 1 1 1 1 −1 −1 1 −1, , , , , , , , ,−1, 1,1, −1,1, −1g,数据速率达33 Gbps。

当输入端的两个m序列之间的时间偏移为零时,相关器的输出为斜坡信号,因为m序列与其自身的乘积会产生一个全为1的N长序列。通过使用比特模式发生器的偏斜控制选项调整输入之间的相位差或偏斜,以使相关峰值最大化。同时应用了同一m序列的移位版本,结果在积分阶段结束时输出值很小,符合预期。这两种情况的结果如图7所示。相关峰值还取决于两个输入信号的幅度。相关峰值的幅度在当前测量中为±76 mVdiff,适合由采用130纳米锗硅 BiCMOS技术制造的、经过适当设计的比较器进行识别。

对于积分/复位信号,使用周期为2 × 536皮秒(或30/28吉比特每秒)的方波,提供每次为15/28吉周期每秒= 536皮秒的复位和积分阶段,并且积分器输出在大约120皮秒[7]内已完成复位。

根据线性度和相关性测试的结果可以得出结论:当PSSS信号应用于相关器两个输入端之一时,相关器仍能正常工作,而不仅限于在相关器的两个输入端都应用m序列。需要注意的是,PSSS信号是多值信号,且其最大幅度受限于P1dB,因此相关器的输出应保持线性。

3.2.2 单IDC测试

已制造并测试了基带接收器电路中单个IDC片的测试电路。图8显示了通过引线键合连接到高速(Isola Astra)基板上的芯片的显微照片。该电路对应于图4中的框图,但模数转换器的输出通过4:1多路复用器进行串行化。低速 SPI接口和1选18脉冲生成电路用于MUX的选择命令已验证可正常工作。图9显示了IDC芯片直接相关器输出的一个示例,其中PSSS输入使用了恒定的直流信号电平,而IDC内部的内部模拟多路复用器被编程以生成一个m序列,并在积分器的复位阶段后接3个额外的循环扩展比特。因此,施加到积分器输入端的乘法器输出为1 1 {f g}

请注意,在本例中,积分/复位信号也是在芯片上生成的。积分阶段持续15个时钟周期,而复位阶段仅为3个时钟周期。用于当前测量的时钟信号频率为15吉赫兹。正在进行针对不同PSSS输入序列、不同解码向量序列以及不同 时钟信号频率的IDC完整表征。

从基带芯片到FPGA的高速接口已单独进行了测试。该接口使用数据加扰以确保目标FPGA中高速收发器内的时钟和数据恢复电路正常工作。该接口由15个并行数据流组成,每个数据流的数据速率为6.666吉比特每秒。制造了一款测试芯片,可生成2个独立的并行数据流,每个数据流速率为6.666吉比特每秒,该数据流可成功与目标FPGA板进行接口连接。该接口概念已扩展至15个并行数据流,但在这种情况下,这些数据流由另一块FPGA板生成。

4 射频同步

随着对更高数据速率的需求不断增长,对更高载波频率的需求也在增加高达300吉赫兹的数值[9]。由于相位噪声在高载波频率下影响显著,模拟载波同步因其对相位和频率变化的相对鲁棒性而日益重要。在高数据速率下,基带中的数字同步由于功耗较大,实现起来并不具有优势[10]。而模拟载波同步则具有功耗低、电路设计复杂性低等重要优势。

在线性时变信道中,必须校正诸如时变频率等非线性效应。在线性时不变信道的情况下,则需要校正恒定相位和频率偏移,这适用于发射机和接收机的非相干本振情况。在这两种情况下,本地生成载波都必须在频率和相位上与接收到的射频载波同步,以完全恢复下变频数据信号。PSSS数据调制系统需要一个相干接收机来提供同步PSSS基带信号。然而,在240 GHz系统中,这将要求电路在射频频率下工作。文献[10]中提到了一种前馈载波恢复方法,其中使用中频(IF)下变频级来提取载波信息,但在本研究中采用直接下变频接收机以利用完整射频带宽。在这种情况下,科斯塔斯环是一种可行的选择,其利用基带信息进行载波恢复。然而,其缺点是该架构依赖于所使用的调制方案[11]。由于PSSS采用抑制载波调制,因此需要特殊的载波恢复方案来提取载波信息。此时可采用前馈载波恢复方案来获取载波信息。但在240 GHz系统中,这将要求载波恢复电路在射频频率下运行。更好的方法是利用基带信息来提取载波信息。尽管科斯塔斯环具有在基带工作且易于在模拟电路中实现的优点,但其缺点是架构依赖于调制方式[11]。

4.1 科斯塔斯环 - 系统级仿真

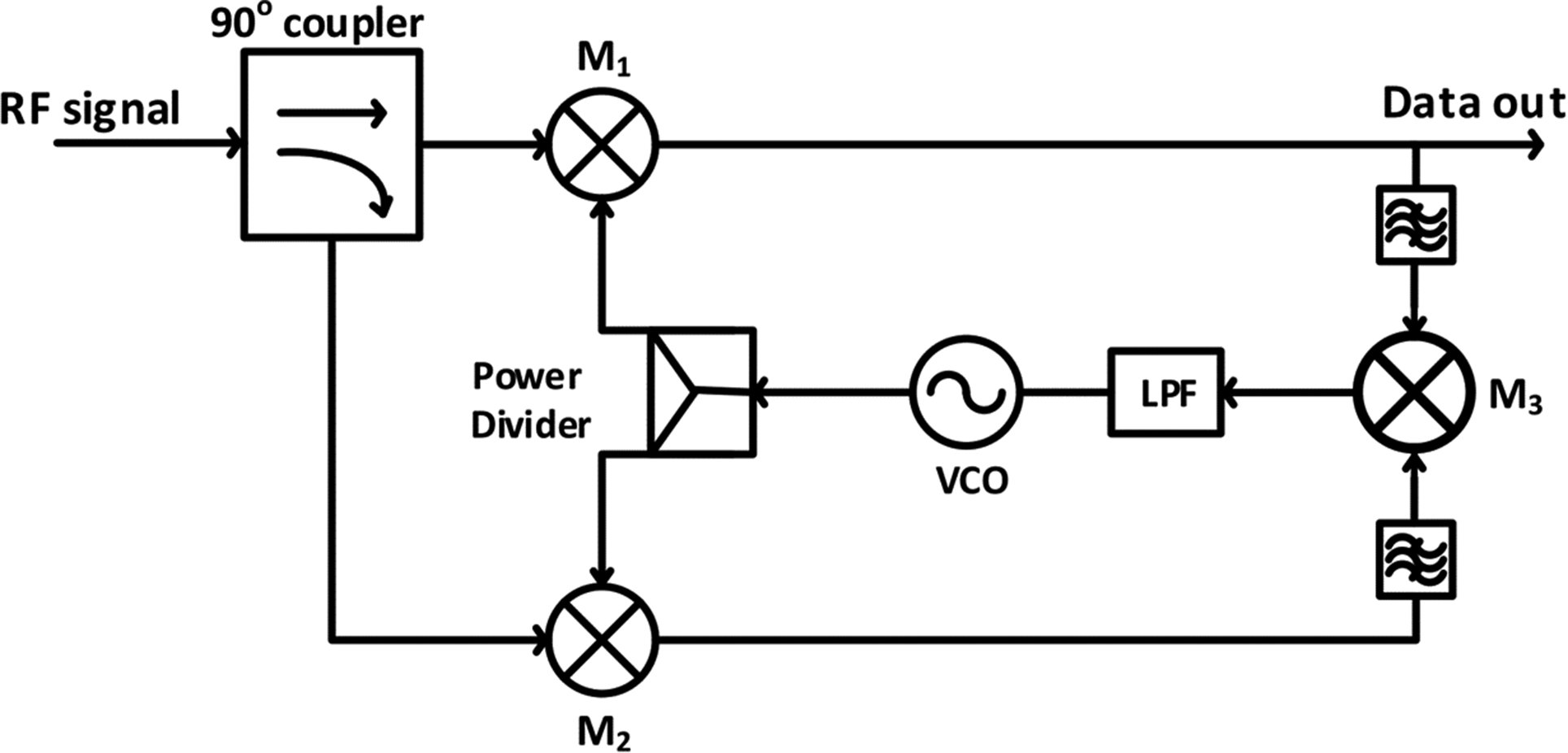

通过使用一组BPSK前导符号对模拟基带(BB)信号进行相位同步用于信道估计和自动增益控制。科斯塔斯环利用下变频基带信号中的幅度信息。图10显示了科斯塔斯环的框图。

下变频混频器级M1和M2提取相位差信息,并将其转换为基带信号中的幅度信息。当载波的相位差趋近于零时,同相信号的幅度增加到1,而正交信号的幅度趋近于零。这些基带信号通过模拟乘法器级M3进行线性相乘,从而形成误差信号。围绕M3的支路滤波器(AF1,、AF2)有助于滤除来自正交支路的噪声信号,以保持环路误差信号的幅度为零。

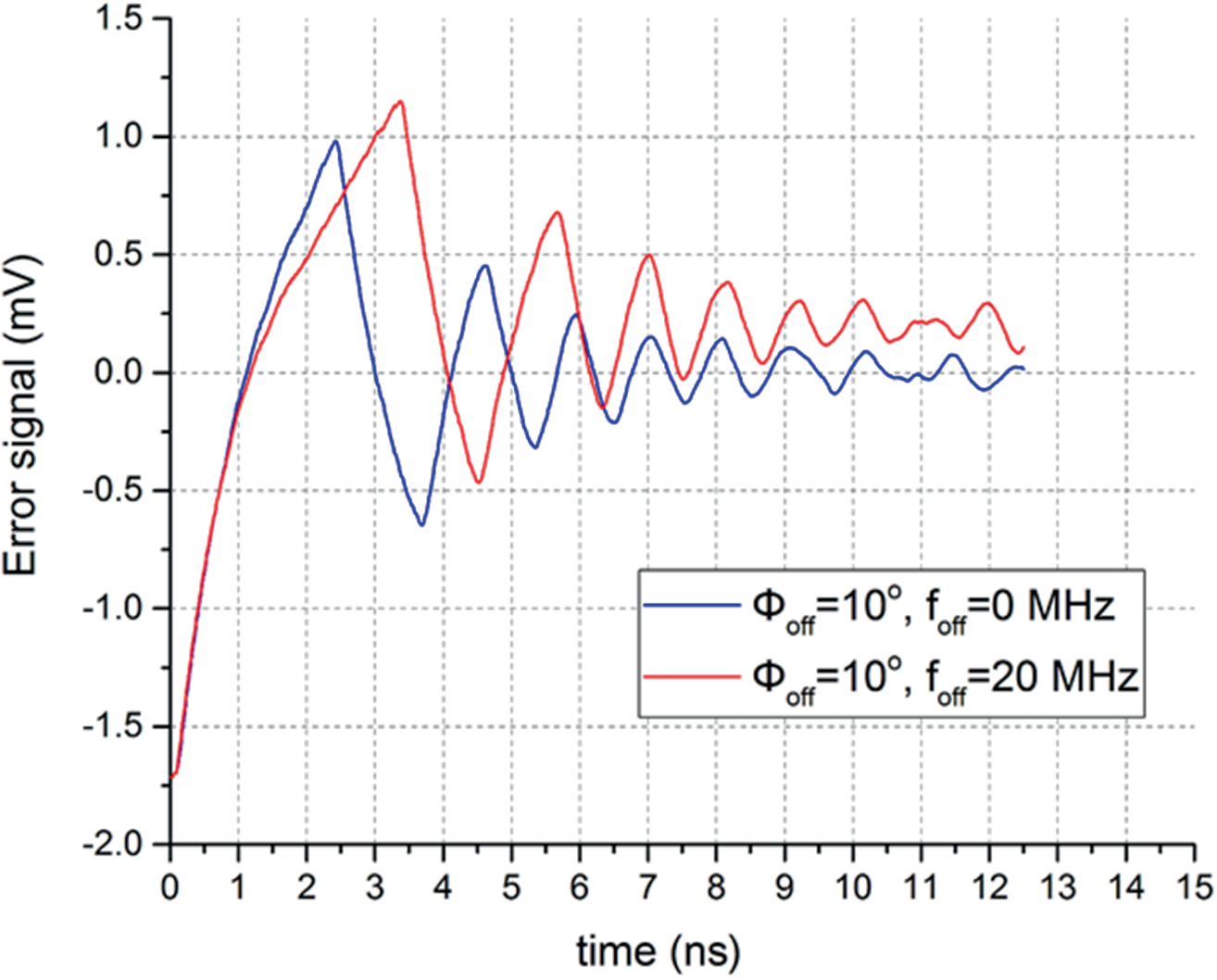

通过包络仿真,分析了使用时间和频率信息的科斯塔斯环的动态特性。图11显示了给定相位误差(Φoff)下误差信号随时间的变化。低通滤波器(LPF)增益使用16 dB的(KLPF)和150兆赫的带宽(BWLPF)。M1, M2和M3的增益设为1,因此环路参数依赖于LPF。误差信号稳定在接近零的值,噪声很小,这是由于在仿真模型中VCO在100 KHz处添加了55 dBc/Hz的相位噪声所致。

当存在相位偏移和频率偏移(foff)时,进入锁定状态所需的时间几乎相同,但误差信号会稳定在某个恒定的直流值,如图11所示。该直流电压使VCO保持在所需频率,以匹配接收到的射频载波。锁定时间还随着环路带宽的变化而变化。当环路带宽减小时,实现快速锁定所需的分析频率被抑制,从而导致锁定时间增加[12]。为了加快锁定过程,可以增大环路带宽,但这会使噪声进入环路。因此,在锁定时间和噪声之间存在一种权衡。

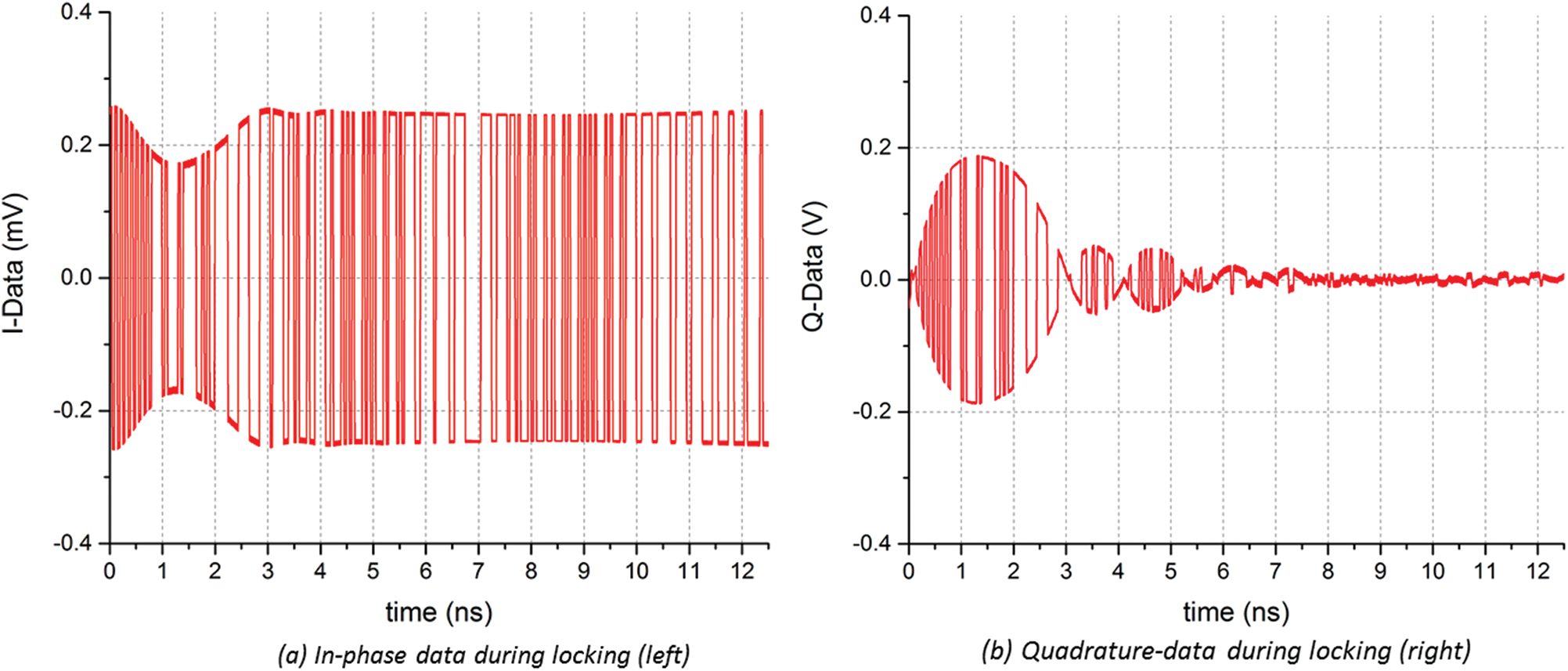

选择环路带宽。但可以使用图10所示的arm滤波器来减小该锁定期间的同相数据恢复如图12(a)所示。这些仿真条件与上述相同,Φoff= 10o和foff= 30兆赫。在同步过程中,所需的同相数据完全恢复到其最大值,而由于载波偏移产生的正交数据则逐渐消失,如图12(b)所示。此处显示的微小波动是由于误差信号中的噪声所致。

4.2 宽带相关器(直流 – 40 GHz)

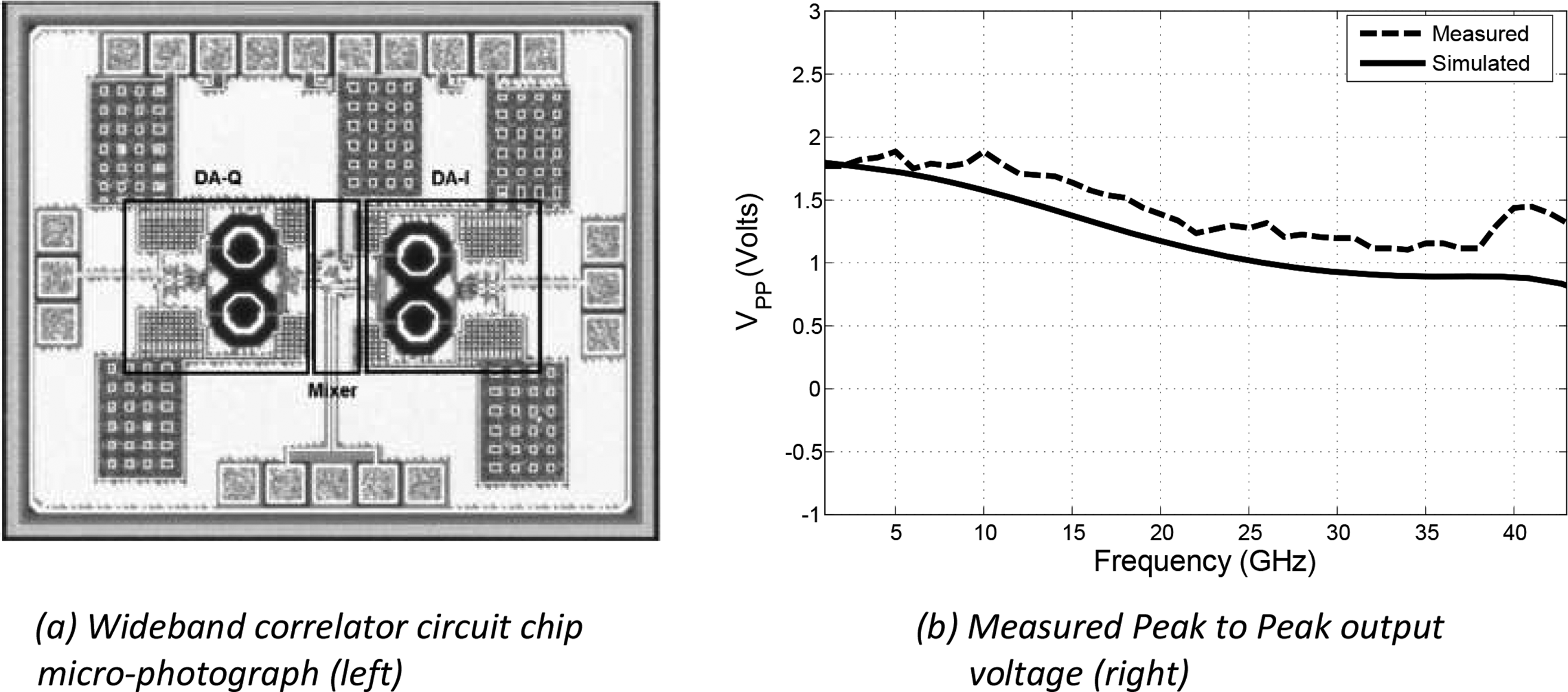

由于科斯塔斯环中的误差检测器功能类似于相关器,因此采用IHP SiGe 0.25 um HBT工艺设计了一个宽带相关器[13]。图1显示了相关器电路的芯片照片。该电路由两个输入驱动放大器和一个有源吉尔伯特单元混频器级。驱动放大器充当单端转差分转换器,连接至吉尔伯特单元混频器的输入端。图13(b)显示了在电路输出端测得的直流到40 GHz范围内的峰峰值电压。

宽带相关器电路芯片显微照片(左) (b) 测得的峰峰值输出电压(右))

宽带相关器电路芯片显微照片(左) (b) 测得的峰峰值输出电压(右))

5 240 GHz下的PSSS系统演示

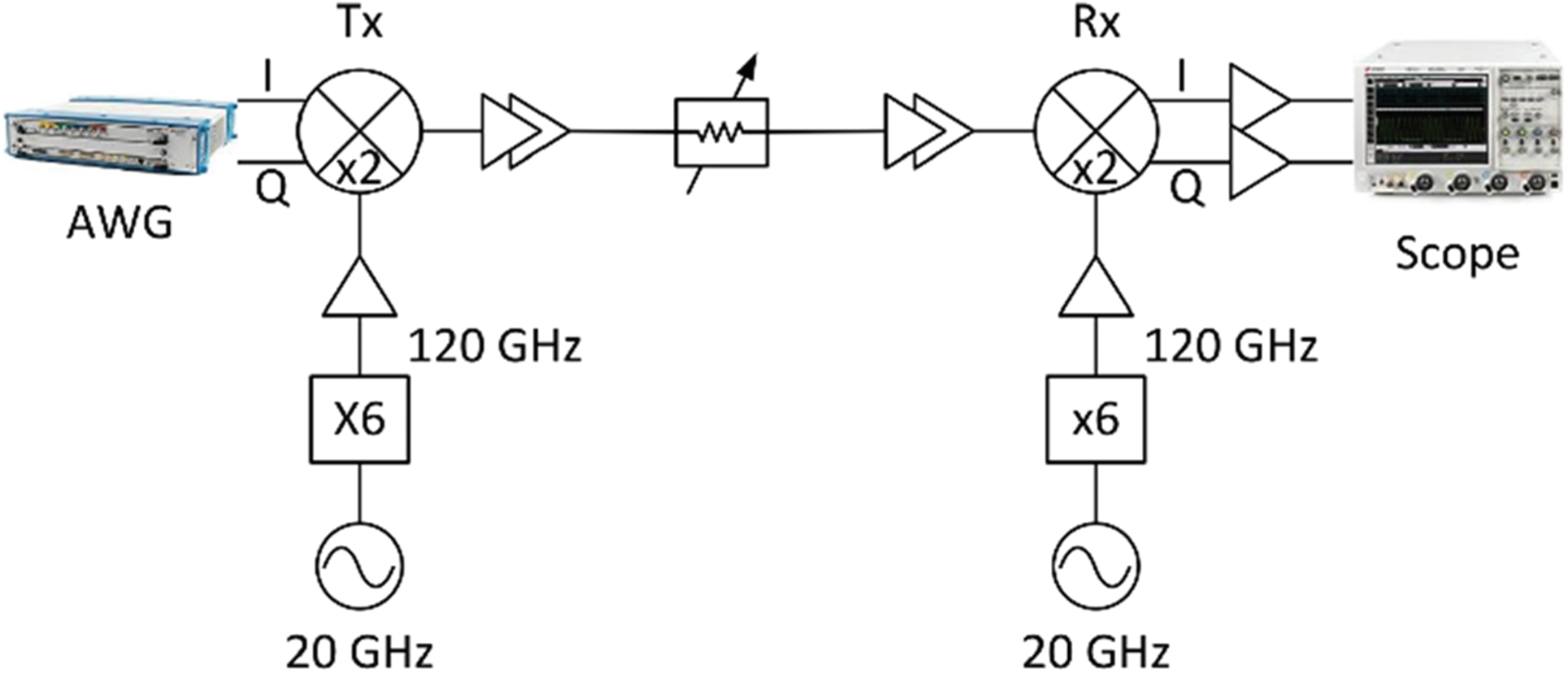

硬件在环测量在如图14所示的背靠背配置中进行。一台以60 GS/s运行的是德科技M8195A任意波形发生器(AWG)向射频前端提供基带信号,而一台以80 GS/s运行的实时是德科技DAS-X 93204A数字存储示波器(DSO)对接收到的基带信号进行采样和存储。

PSSS收发器已在MATLAB/Simulink中离线实现。用于传输的基带(BB)数据(即PSSS调制符号)已存储在任意波形发生器(AWG)中,PSSS调制信号通过240 GHz射频前端[1]发射。数字存储示波器(DSO)对接收信号进行采样并存储。接收到的PSSS基带(BB)数据经过后处理,用于同步、信道估计、信道去卷积的参考计算、解码和误码率计算[14]。

如图14所示,240 GHz无线链路[1]通过背靠背方式连接一个可变衰减器,以模拟传输信号的信道。该系统设置为非相干传输,其中数据和本振(LO)信号来自不同时钟。本振(LO)信号由频率合成器产生,而PSSS调制信号则通过任意波形发生器[14]生成。这种非相干性是由于发射机和接收侧使用了不同的LO源,以及生成的数据信号采用独立时钟所致。在这种非相干设置情况下,同步在数字域中完成。

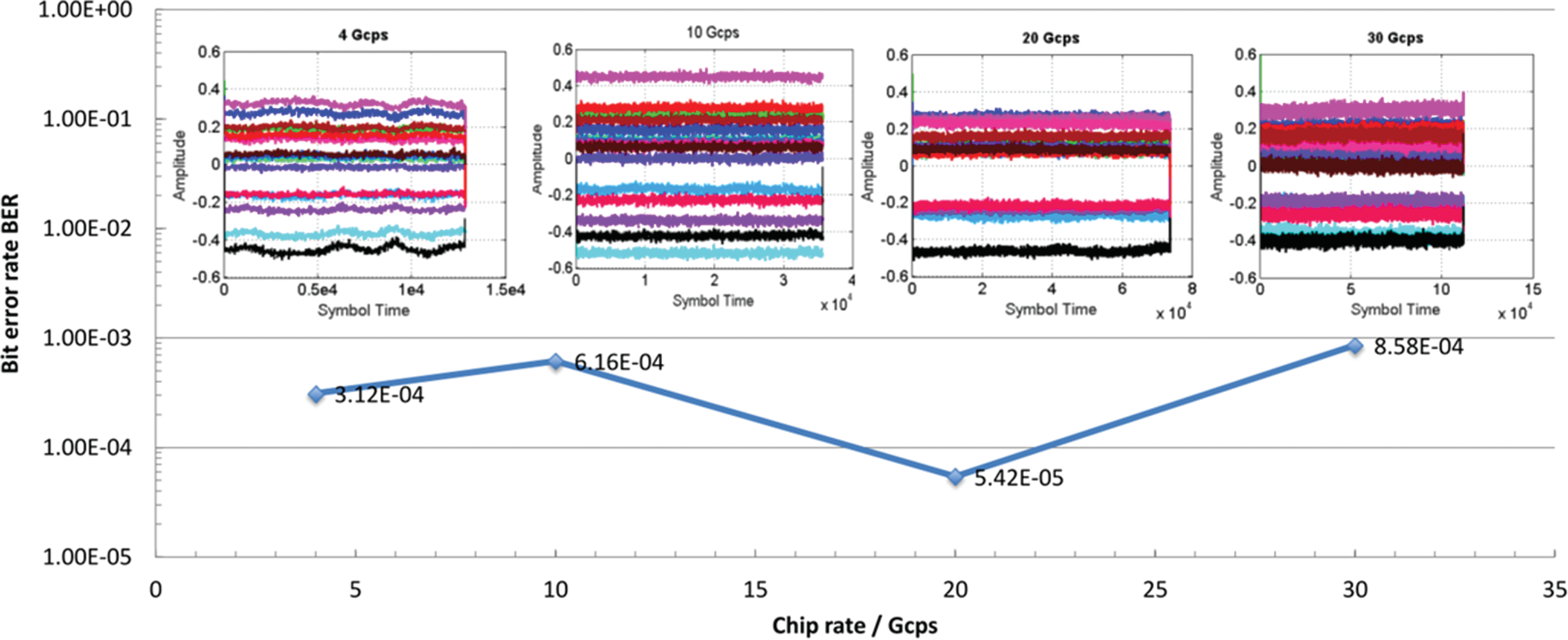

在图15中,针对不同的码片速率展示了眼图及其相应的误码率。对于编码数据速率为20 Gbps的情况,测得垂直眼图张开度为40%,误码率为5.4 × 10⁻⁵,[14]而在30 Gcps时测得的误码率为8.58 × 10⁻⁴。通过使用更线性的射频前端,频谱效率可进一步提高到4 bits/s/Hz,从而利用PSSS调制[14]实现100 Gbps。

6 结论与展望

在高频毫米波下实现100 Gbps无线通信需要在发射机和接收机基带电路中进行超宽带信号处理,这对基带数据转换器和信号处理器提出了极为严苛的指标要求。本文介绍了基于PSSS的收发器架构以及基于科斯塔斯环的射频载波同步技术的研究,该技术能够高效地在模拟域中实现大部分基带信号处理。其中包括使用并行DAC和ADC,这些转换器工作在相对较低的PSSS流符号速率下,从而显著降低了对数据转换器的要求。我们展示了系统模型,并讨论了主要系统参数的设计,重点在于混合信号实现。用于接收机信号处理的关键电路,如宽带积分清零和宽带相关器,已在SiGe BiCMOS技术中实现,并展示了其测量结果。最后,讨论了通过硬件在环测量实现20 Gbps 240 GHz PSSS链路的演示。该实验设置包括240 GHz射频前端、高速任意波形发生器和数字存储示波器,以及在Matlab中实现的PSSS基带处理器模型。未来工作目标是实现具备射频同步功能的完整的PSSS发射机和接收机,以研究基于PSSS的收发器架构和混合信号处理在未来超宽带无线通信链路中的适用性。

8051

8051

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?