目录

1. 概述

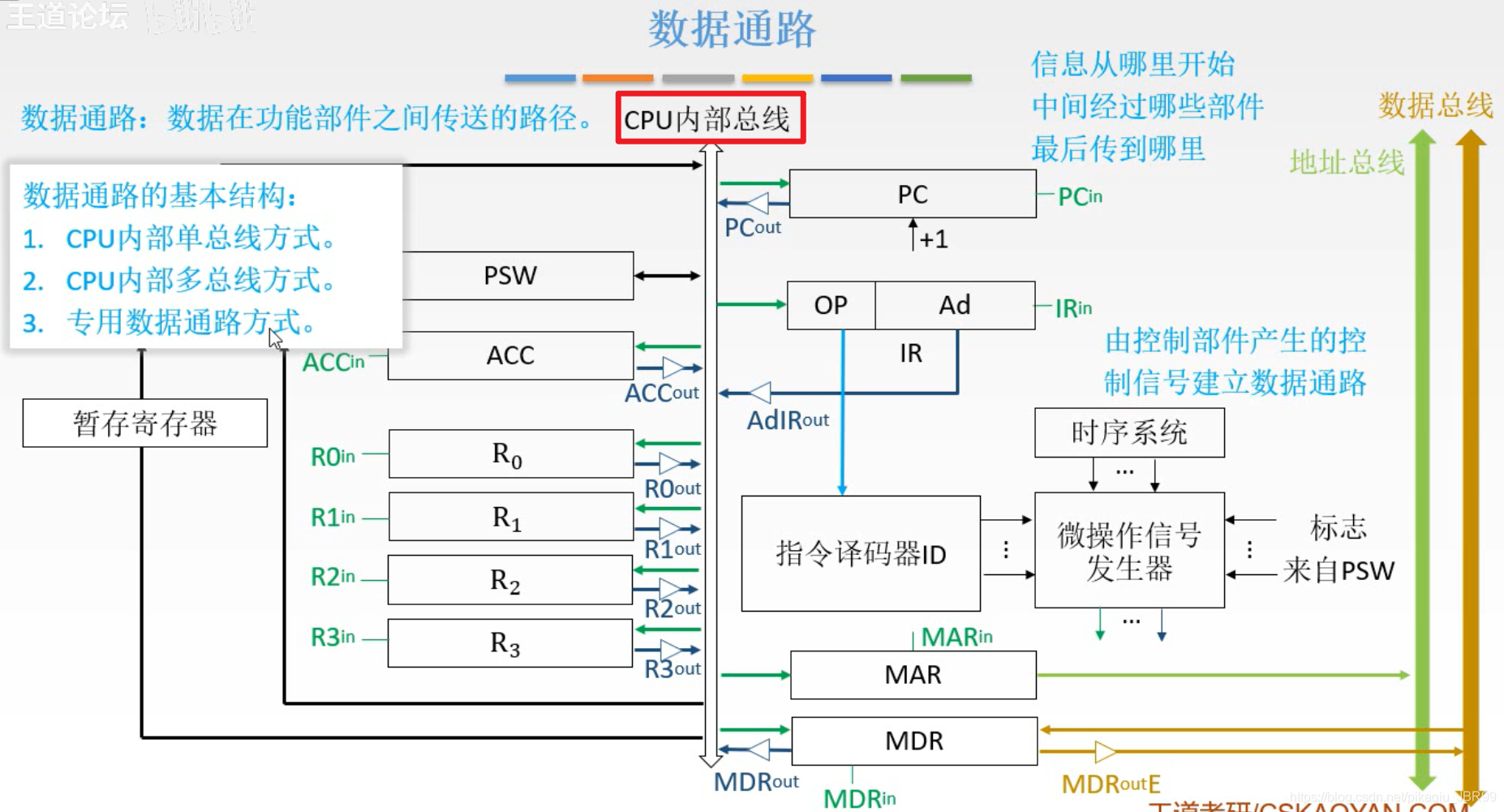

在研究数据通路的时候,要搞清楚的一个问题就是:信息从哪里流出来的,中间经过哪些部件,最后传到哪个部件;

以及这样的流动是怎么去控制的 = => 依靠的是控制单元所发出来的控制信号,这些控制信号可以建立数据通路。

而具体应该有哪些控制信号 ==> 基于 CPU 内部这些连线的方式的。

连线的方式有三种:CPU 内部单总线方式、CPU 内部多总线方式、专用数据通路方式。

前两种可以看成一种:即采用总线的方式。

2. 单总线方式下的分析

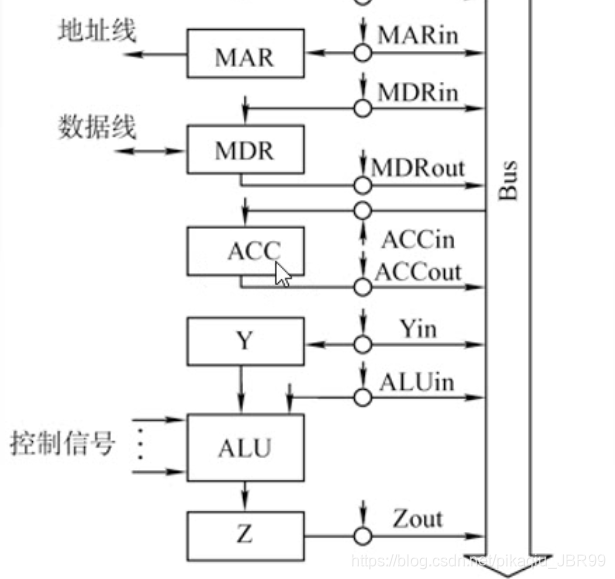

部件的连接逻辑:每个部件都直接和 CPU 总线相连,但是部件与部件之间没有直接的连线。

每个部件和总线连接的方式是一条可以控制通断的通路,通路的通断是由上面标志的控制信号来控制的,

out 结尾的控制信号决定这条通路能否向外传输信息, in 结尾的控制信号决定这条通路能否由外向内部传输信息。

(所以应该是单向指向内,图中画了双向,应该修改为单向。)

MAR MDR 是和主存进行交流的,所以向外连接到地址总线和数据总线。 图中的 Y 和 Z 是暂存寄存器。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2994

2994

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?