CPU组成:运算器,控制器,寄存器等部件组成。控制器包含指令寄存器,程序计数器,译码器,操作控制器组成。

指令执行过程:1.外存中的程序(指令)和数据载入到内存中。2.将内存中的指令和数据分别载入指令寄存器和数据寄存器中。3.译码器将指令寄存器中的指令翻译为机器可识别的唯一机器码。4.操作控制器控制运算器工作。5.运算器从寄存器中取出数据并进行计算(中间结果也保存在寄存器中)。6.将运算结果写回内存和外存中。

流水线技术的理解:指令执行过程分为6个子过程,一条指令经过以上所有过程算是执行完毕。考虑每个过程可以独立运行,译码器翻译指令的时候指令寄存器就可以去读取下一条指令,译码器将机器码交给操作控制器后就可以马上去翻译新的指令,以此类推一个模块只做一件事情。每个模块就像流水线的一个个车间一样,可以提高生产效率。

寄存器基础和伪指令基础概念可以参看一下两篇文章,对cpu的指令执行有个大概的了解:

CPU的内存管理和任务保护,对于多任务系统保持每个任务之间互相独立,一般采用将每个进程的内存地址设为相互独立且连续的4G大小(前2G为系统内存),我们称之为线性内存地址,而在进程内会检查当前用户状态是否具有访问系统内存的权限。线性地址是在逻辑上的一种抽象,其实并不需要将所有的内容载入到物理内存中,我们使用分页机制将需要的内容载入内存,并将逻辑地址与物理地址对应起来。

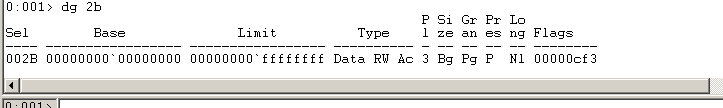

分段机制:源于8086只有16位寄存器,而有20位地址总线,寄存器无法表现所有的内存地址,故将内存分段,在每一段内使用偏移地址来映射所有内存,而分段的信息保存在段描述符表中,段寄存器保存段选择子,段选择子保存段在段描述符表中的索引,找到段描述符中的基地址后加上偏移量得到当前所指向的内存地址。现代CPU寄存器位数增加以后能够完全映射内存采用平坦模型,不再需要偏移了,在windebug中可以看到段描述信息,基地址为0,limit为4G

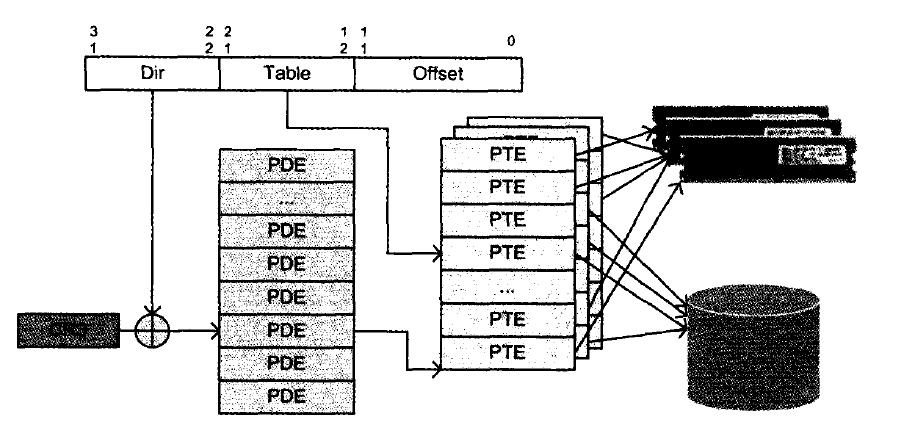

分页机制:只有在需要的时候将数据加载到内存中,并可以根据不同任务中的逻辑地址计算出唯一的物理地址。地址的翻译过程为CR寄存器指向的内存地址为页目录表地址,线性地址的高10位为页目录表的索引,页目录表的12~31位指向的内存地址为页表地址,线性地址的中间10位为页表的索引,页表的12~31位指向的内存地址内存页的地址,线性地址的低12位为内存叶中的便宜地址。从CR寄存器指向的内存开始寻找页的物理地址的过程如下:

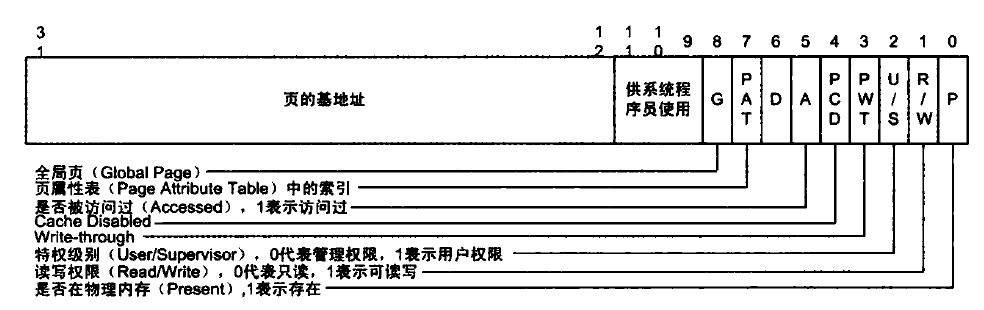

页目录表项和页表项的结果如下:

466

466

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?