UART IP

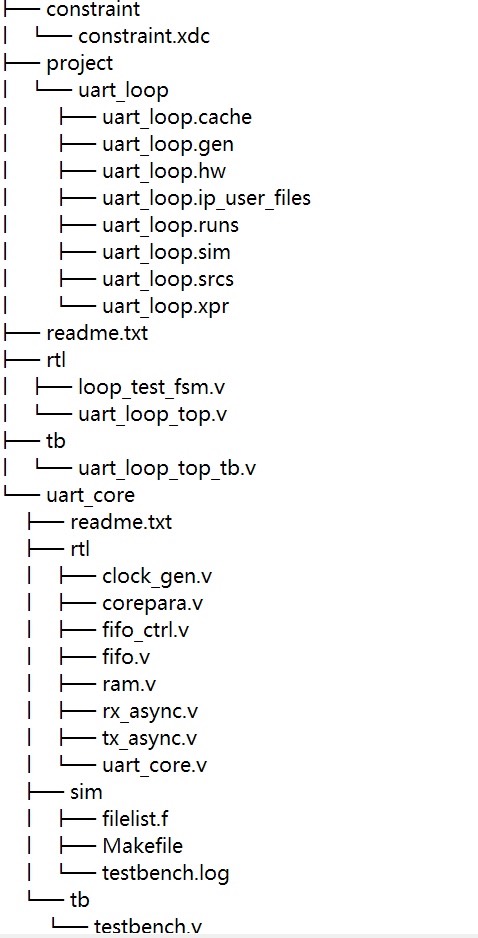

项目使用的代码;

使用verilog;

IP使用VCS进行仿真;

可移植到任何FPGA上使用;

上板测试工程为回环测试,接收上位机发送数据再发回给上位机,也包含仿真文件,使用vivado

ID:64699688090032369

咸鱼_RTL猿

UART IP是一种常见的串行通信接口,被广泛应用于各种嵌入式系统和数字电路设计中。本文将围绕UART IP展开讨论,重点关注项目使用的代码、使用Verilog进行开发、IP的仿真以及可移植性和上板测试工程。

在项目开发过程中,选择合适的代码实现方式对于UART IP的正确功能和高性能至关重要。代码的可读性、可维护性和可扩展性是评估代码质量的重要标准。项目使用的代码采用了Verilog语言,Verilog是一种硬件描述语言,适用于数字电路设计。它通过模块化的方式描述电路结构和行为,能够方便地实现各种逻辑功能。通过合理的模块划分和代码结构设计,可以提高代码的可读性和可维护性,减少调试和维护的难度。

在开发过程中,使用VCS进行仿真是一种常用的方法来验证设计的正确性和性能。VCS是一种功能强大的仿真工具,可用于验证硬件设计的功能和时序。通过构建仿真环境和测试向量,可以对UART IP进行全面的功能验证,确保其符合设计要求。在仿真过程中,可以检测到可能存在的时序问题、数据错误和其他异常情况,并及时进行修复和优化。

UART IP的可移植性是它的一个重要特点。由于不同的FPGA厂商采用了不同的架构和接口标准,为了能够在不同的FPGA上广泛使用,必须设计出具有良好可移植性的IP。可移植性的实现可以通过采用标准接口、遵循规范和良好的工程实践来完成。通过将IP模块进行参数化和配置,可以方便地适配不同的FPGA芯片,并提供更好的可扩展性和灵活性。

为了验证UART IP在实际硬件上的功能和性能,需要进行上板测试。上板测试工程通常包括回环测试,即接收上位机发送的数据后再将其发回给上位机。这种测试方式能够直接验证UART IP的收发功能,并且便于检测硬件设计中可能存在的问题。同时,回环测试还需要提供仿真文件,以便与实际硬件进行对比,确保仿真结果与实际情况一致。在上板测试工程中,可以使用vivado等工具进行开发和调试,进一步验证UART IP的正确性和性能。

综上所述,UART IP在项目中的应用非常广泛,可以通过合适的代码实现方式、使用Verilog进行开发、IP的仿真以及可移植性和上板测试工程来确保其正确功能和高性能。通过合理的设计和验证流程,开发人员可以为不同的嵌入式系统和数字电路设计提供稳定和可靠的UART通信功能。

【相关代码 程序地址】: http://nodep.cn/688090032369.html

本文详细介绍了UARTIP项目中使用Verilog编程、VCS仿真、FPGA移植及上板回环测试的过程,强调了代码质量、可移植性和验证的重要性。

本文详细介绍了UARTIP项目中使用Verilog编程、VCS仿真、FPGA移植及上板回环测试的过程,强调了代码质量、可移植性和验证的重要性。

3822

3822

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?