前言

在写TB代码时,如果循环退出条件没注意,可能使循环一直不能退出,而且该循环又是没有延时的,因此就出现了zero-delay(零延时)的无限循环。

编写RTL,如果不注意,可能会写出zero-delay(零延时)的组合逻辑,也就是组合逻辑的输出,直接反馈到组合逻辑的输入上,导致零延时的组合逻辑。

一、irun工具

方法一:

irun提供了 +linedebug 编译选项,可以实现代码的调试。

irun -64 –sv +access+wrc +linedebug testbench.v

方法二:

使用simvision工具,进行调试,命令如下:

irun -64 –sv +access+wrc -gateloopwarn zero_dut.v testbench.v -gui

在console界面中,输入run,开始仿真。

输入 driver -active,会打印出,工具认为的零延时组合逻辑的RTL代码位置。

三、vcs工具

方法一:

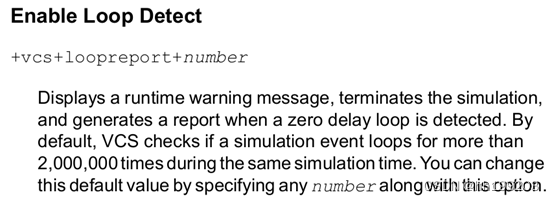

Compile/simv中加上这个option: +vcs+loopreport+number

方法二:

在compile用-debug_all,然后手动找。

方法如下:

Run the simulation using the following command:

./simv -ucli

## create the following procedure to run the simulation for "nsteps"

ucli%proc mstep {nsteps} {

global now

for {set a1 0} {$a1 < $nsteps} {incr a1} {

echo [step]

echo $now

echo [senv activeScope]

}

}

Ucli% run

##Once you think that the simulation is already in infinite loop,

##you can hit "CTRL C"

Ucli% mstep 1000

## The above step will generate simulation step log for next 1000 steps.

## You can then analyze the log file to see if there is any repetition of

## the logic. If you do not see the repetition then run for another 1000

## steps and so on.

总结

本文主要介绍irun和vcs如何利用工具去检测TB环境零延时无限循环以及zero-delay组合逻辑。

249

249

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?