这里主要是以电脑显示器为实验平台。

标准VGA接口一共有15个接口,真正用到的信号接口不多,就五个,HSYNC 是行同步信号,VSYNC是场同步信号, 同步信号就是为了让 VGA 显示器接收部分知道送来的数据是对应哪一行哪一列的哪一个像素点的。VGA_R、VGA_G、VGA_B 是三原色信号,这三个信号接口的输入都是模拟信号(标准为 0-0.7V),所以它们都有相应的地线需要连接。我们使用的这块学习板的接口做得比较简单,直接用 I/O 口去连接 VGA的五个信号接口,并且三原色信号接口输入的只可能是数字信号(0 或 1) ,因此驱动液晶屏上显示的颜色最多也就 8 种。一般来说,可以在 FPGA/CPLD 和 VGA接口间加一个 DAC 芯片,这样就可能实现 65536 种或者更多色彩的显示。

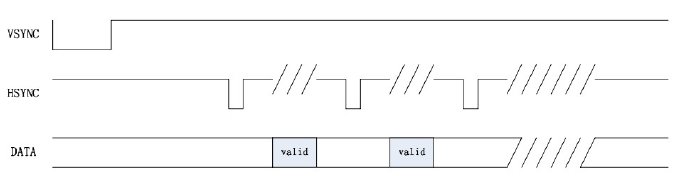

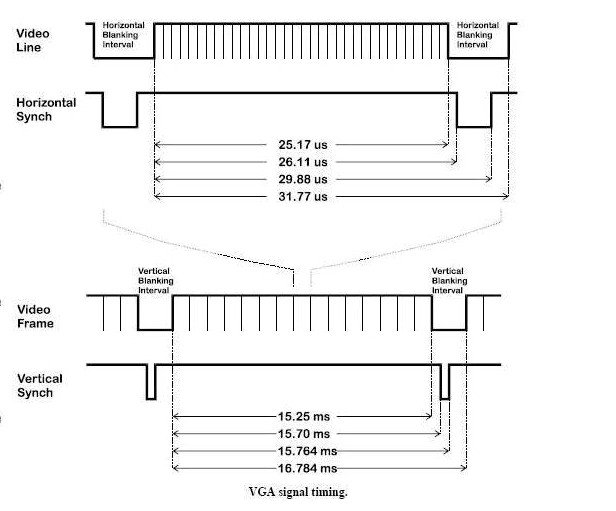

其主要是由两个同步信号所控制,即场同步信号VSYNC和行同步信号HSYNC。, 场同步信号 VSYNC 在每帧开始的时候产生一个固定宽度的低脉冲, 行同步信号 HSYNC 在每行开始的时候产生一个固定宽度的低脉冲,数据在某些固定的行和列交汇处有效。其时序图如下:

具体程序如下:

//==============================VGA-256===================================

module vga_256(clk,rst,hsync,vsync,vga_r,vga_g,vga_b );

input clk;

input rst;

output hsync;

output vsync;

output [2:0] vga_r;

output [2:0] vga_g;

output [1:0] vga_b;

reg clk2;

reg [9:0] x_cnt;//行坐标

reg [9:0] y_cnt;//列坐标

initial begin

clk2 = 0;

end

always @(posedge clk)

clk2 <= ~clk2; //2分频,输入时钟25M

always @(posedge clk2 or negedge rst) //列扫描

if(!rst)

x_cnt <= 10'd0;

else if(x_cnt == 10'd799)

x_cnt <= 10'd0;

else

x_cnt <= x_cnt+1'b1;

always @(posedge clk2 or negedge rst) //行扫描

if(!rst)

y_cnt <= 10'd0;

else if(y_cnt == 10'd524) //扫描到524行

y_cnt <= 10'd0;

else if(x_cnt == 10'd799)

y_cnt <= y_cnt+1'b1;

reg hsync_r,vsync_r;//行,场同步信号

always @(posedge clk2 or negedge rst)

if(!rst)

hsync_r <= 1'b1;

else if(x_cnt == 10'd0)

hsync_r <= 1'b0;

else if(x_cnt == 10'd96)

hsync_r <= 1'b1;

always @(posedge clk2 or negedge rst)

if(!rst)

vsync_r <= 1'b1;

else if(y_cnt == 10'd0)

vsync_r <= 1'b0;

else if(y_cnt == 10'd2)

vsync_r <= 1'b1;

assign hsync = hsync_r;

assign vsync = vsync_r;

reg valid_yr;//有效标志位

always @(posedge clk2 or negedge rst)

if(!rst)

valid_yr <=1'b0;

else if(y_cnt == 10'd32)

valid_yr <= 1'b1; //32-512之间显示

else if(y_cnt == 10'd512)

valid_yr <= 1'b0;

wire valid_y = valid_yr;

reg valid_r;//有效显示标志区

always @(posedge clk2 or negedge rst)

if(!rst)

valid_r <= 1'b0;

else if((x_cnt == 10'd141) && valid_y)

valid_r <= 1'b1;

else if((x_cnt == 10'd781) && valid_y)

valid_r <= 1'b0;

wire valid = valid_r;

wire [9:0] x_dis;//横坐标显示有效区域相对坐标0-639

wire [9:0] y_dis;//纵坐标显示有效区域相对坐标0-479

assign x_dis = x_cnt - 10'd142;

assign y_dis = y_cnt - 10'd33;

//VGA色彩信号

//

reg [7:0] vga_rgb;

always @(posedge clk2)

if(!valid) vga_rgb<=8'd0;

else begin

case(x_dis)

10'd0:begin

if(y_dis >= 10'd0 && y_dis < 10'd30) vga_rgb <=8'd0;

else if(y_dis >= 10'd30 && y_dis < 10'd60) vga_rgb <=8'd16;

else if(y_dis >= 10'd60 && y_dis < 10'd90) vga_rgb <=8'd32;

else if(y_dis >= 10'd90 && y_dis < 10'd120) vga_rgb <=8'd48;

else if(y_dis >= 10'd120 && y_dis < 10'd150) vga_rgb <=8'd64;

else if(y_dis >= 10'd150 && y_dis < 10'd180) vga_rgb <=8'd80;

else if(y_dis >= 10'd180 && y_dis < 10'd210) vga_rgb <=8'd96;

else if(y_dis >= 10'd210 && y_dis < 10'd240) vga_rgb <=8'd112;

else if(y_dis >= 10'd240 && y_dis < 10'd270) vga_rgb <=8'd128;

else if(y_dis >= 10'd270 && y_dis < 10'd300) vga_rgb <=8'd144;

else if(y_dis >= 10'd300 && y_dis < 10'd330) vga_rgb <=8'd160;

else if(y_dis >= 10'd330 && y_dis < 10'd360) vga_rgb <=8'd176;

else if(y_dis >= 10'd360 && y_dis < 10'd390) vga_rgb <=8'd192;

else if(y_dis >= 10'd390 && y_dis < 10'd420) vga_rgb <=8'd208;

else if(y_dis >= 10'd420 && y_dis < 10'd450) vga_rgb <=8'd224;

else vga_rgb <= 8'd240;

end

10'd40,10'd80,10'd120,10'd160,10'd200,10'd240,10'd280,10'd320,10'd360,

10'd400,10'd440,10'd480,10'd520,10'd560,10'd600:vga_rgb <= vga_rgb+1'b1;

default: ;

endcase

end

assign vga_r = vga_rgb[7:5];

assign vga_g = vga_rgb[4:2];

assign vga_b = vga_rgb[1:0];

endmodule

---------------------------------------转载请注明出处-------------------------------------------

619

619

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?