最近调试一个项目,时序没有报错,仿真没有问题,但是上板始终差一个bit,因为更换过器件,所以怀疑IP,各种怀疑,最后没办法,只能在signaltap上一个模块一个模块抓,然后跟仿真结果对比,最终定位到一个计数器。计数器的代码如下

always @(posedge clk or posedge reset) begin // 模块3

if (reset)

dinCnter <= 0;

else if (din_en == 1'b1 && dinCnter != 11)

dinCnter <= dinCnter + 1'b1;

end

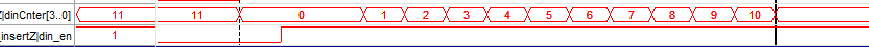

这里reset是一个本地的复位信号,在din_en的前一拍是拉高的,signaltap抓出来的结果如下,可以看到dinCnter并没有在din_en拉高后马上开始+1。

reset和din_en信号是上一个模块给过来的,大概的逻辑如下

assign x = (a & b) | (c & d); // 模块1输出

assign din_in = (g & h) | (l & o); // 模块1输出

assign reset = x | p; // 模块2中的赋值语句

// 上面的计数器为模块2的子模块中的逻辑

对x和din_en打一拍输出结果就对了。

代码虽然不是我写的,但是我也觉得这样写没什么问题,这里没有几级组合逻辑,感觉可以接受(虽然已经是跨模块了),因为a、b、c、d、g、h、l、o都是寄存器输出的。

问题是为什么时序报告里没有这条关键路径?从结果来看很明显是din_en没有满足建立时间的要求。

总结这次经验,模块的输出一定要寄存器输出,输入最好也是。.

.

.

.

.

.

.

.

.

.

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?