前言

本文暂时先附上CRC算法的基本原理,方便自己后期的学习查看。

本文参考《基于FPGA的嵌入式开发与应用》徐光辉,此书中含有较多的印刷错误。

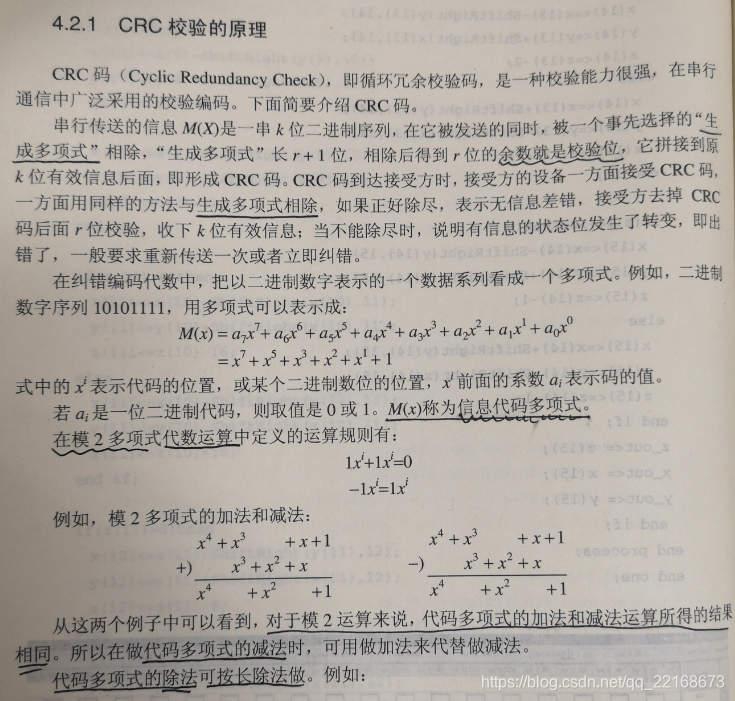

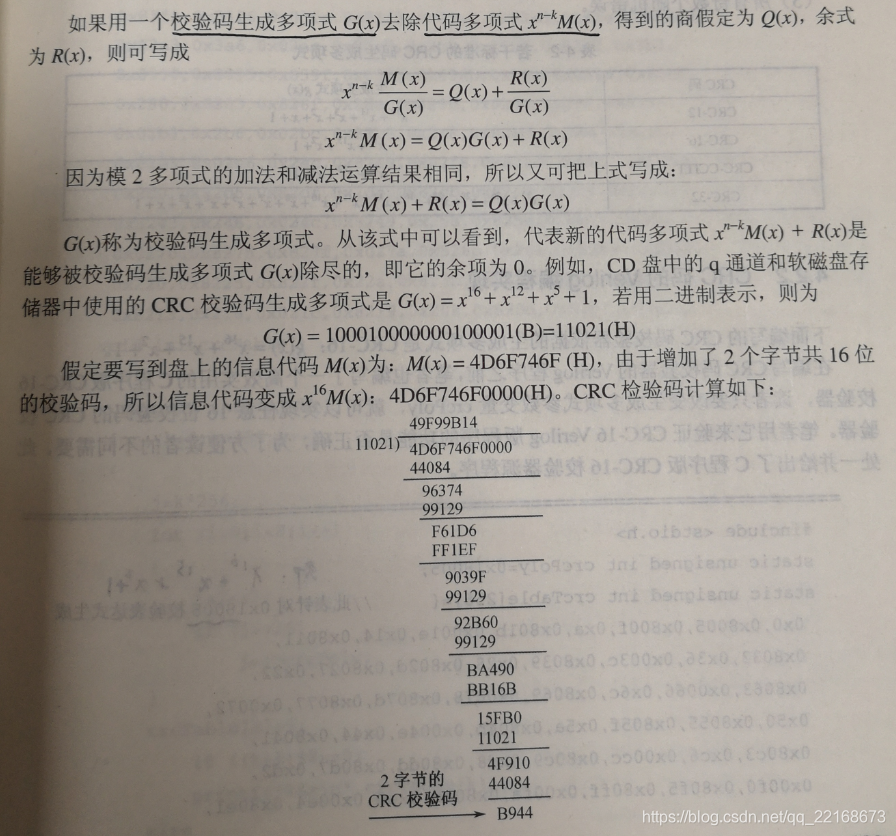

CRC

下图4-7存在印刷错误。

在下图中,G(x)的二进制bit串中多了一个0(印刷错误),十六进制表示是正确的。

正确表示为:G(x)=1_0001_0000_0010_0001(B)=11021(H).

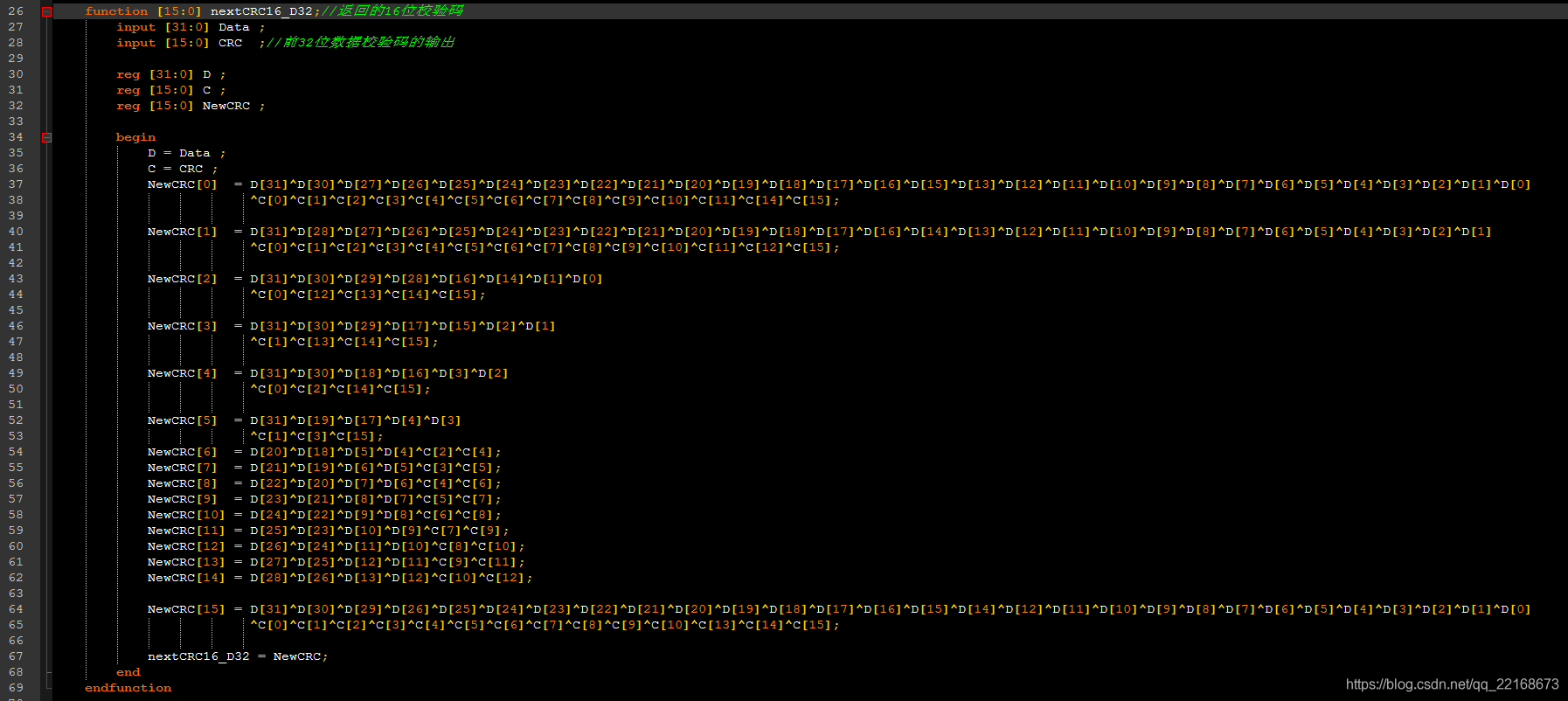

CRC16的FPGA实现

1、Verilog代码

下面Verilog中采用的生成多项式是,上表4-2中标准的CRC码生成多项式CRC-16

2、modelsim仿真

参考文献

| 1、Pushment | CRC校验算法的Verilog实现 |

| 2、徐光辉 | 《基于FPGA的嵌入式开发与应用》 |

| 3、Payshent | CRC校验算法 |

| 4、persistence_s | CRC校验 |

| 5、ssl2009 | 闲话CRC32校验 |

| 6、xiaogugood | 我学习CRC32、CRC16、CRC原理和算法的总结(与WINRAR结果一致) |

| 7、请叫我小怪物 | CRC _Generator _32_8 |

3766

3766

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?