1.ARMv7-M memory mapped architecture

ARMv7-M是采用Memory-mapped架构,这一位置该架构采用了物理地址作为:

- 事件入口,比如vectors向量表。

- 系统控制和配置,比如System Control Registers。

ARMv7-M实现了使用一个地址列表来存放异常处理入口,即发生异常时,从Vector Table中获取异常处理函数入口。

该架构保留了地址空间0xE000000-0xFFFFFFFF给System Level使用。arm使用了该空间的低1MB空间作为PPB使用(Private Peripheral Bus)。剩余的空间可以基于系统设计自行使用,但是存在内存属性的限制,如Execute Never等。

2.Overview of system level terminology and operation

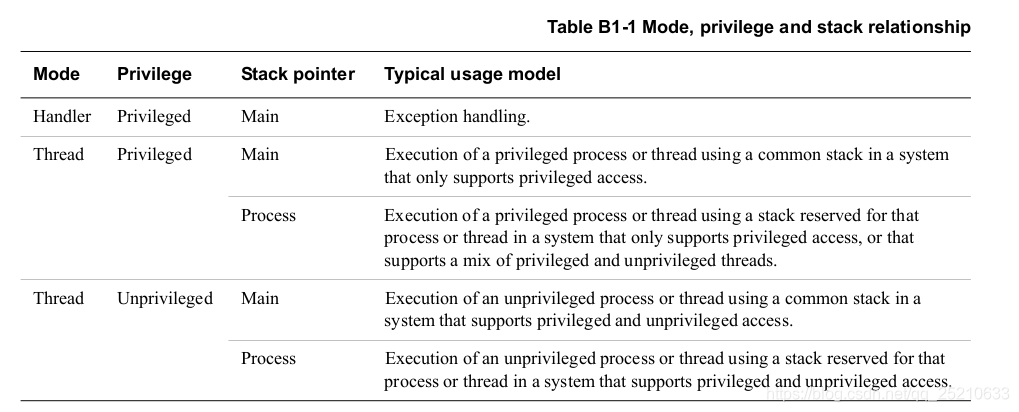

Modes, privilege and stacks

模式:

M架构的处理器支持两种操作模式:

Thread mode 在Reset时进入的模式,也作为Execption返回时的模式。

Handler mode 出现异常时进入的模式,处理器要进行异常返回时,当前模式一定是Handler mode。

特权级:

代码能够运行在特权(Privileged)或者非特权(Unprivileged),非特权下的代码在访问某些资源时会被限制,特权下的代码能够访问所有资源(Stm32 f103系列所采用的Cortex-M3内核处理器,代码全部运行在Privileged下)。

运行在Handler mode下的代码全部为特权的,比如Execution Handler函数。

运行在Thread mode下的代码可以是特权的或者非特权的。

栈指针:

处理器实现了一对栈寄存器,Main Stack pointer和Process Stack pointer,在Handler mode下使用Main Stack pointer,在Thread mode下两者都可以使用(Stm32 f103系列所采用的Cortex-M3内核处理器,使用Main Stack pointer)。

Exceptions

异常的产生:

有相应的异常事件发生并呈递给处理器时,会产生一个异常。

异常的处理:

处理器按照异常入口去执行异常处理代码。

异常种类:

- Reset:特殊的异常,当被产生时,会以不可恢复的方式终止当前的程序运行。

- Supervisor Call (SVCall):有SVC指令产生。应用程序可以通过此方式通知下层操作系统,可以为应用程序更改特权级访问或者切换特权级等操作。ARM-v7 M也支持

- PendSV机制。

- Fault:当指令运行出错时,会产生Fault异常。可以分为synchronously(同步)和asynchronously(异步)异常。大部分情况下的Fault异常都是同步异常,但BusFault是种异步异常。同步异常会和导致异常的指令一起被报告出来,但是不保证能报告出异步异常的原因。

- Interrupt:中断区别于以上三种异常,所有中断都与指令流异步。典型的,中断被用来外设和处理器的交互。

每种指令都有一个异常号,优先级,Vector中的Entry Pointer。

除Reset外,其他异常还有以下状态:

异常状态:

Inactive:异常既不是Pending也不是Active状态。

Pending:相应的异常事件发生了,但是处理器还没有处理。

Active:处理器正在处理当前异常,但是还未退出Exception Handler,也可能在handler中被更高优先级的异常打断。

Active and Pending:当一个异常时Active状态时,又产生了相同的异常。只有异步异常才能够同时有Acitve 和 pending状态。

- 每种异常都有优先级,其中三种异常的优先级是固定的,其他的异常优先级都可以配置。

- 指令的执行也有相应的优先级,成为运行优先级。

- Reset后的执行优先级是执行优先级的基本级别。只有Thread模式下的指令的执行才能处于此基本执行优先级。

- 异常优先级足够高于当前执行优先级的异常将变为活动状态。足够高优先级概念与优先级分组有关。

软件能够通过寄存器修改运行优先级。

异常返回:

- 如果异常状态时Active且Pending。

(1).如果异常有足够的优先级,它将会变成active并且重新进入异常处理函数。

(2).其他情况下将会进入pending状态。

- 如果异常状态时Active,它将会变为Inactive。

- 处理器将会恢复为进入异常时保存到栈中的信息。

- 如果之前的代码运行在Thread模式,那么处理器将会改变为Thread模式。

- 处理器恢复被异常处理函数抢占之前的代码。

Execution state

ARMv7-M只能运行Thumb指令集。ESPR.T bit位代表了Thumb指令运行状态,为1表示正在运行Thumb指令。设置此bit为0会导致处理器在运行下条指令时产生Fault错误,因为在这个状态下所有的指令都是未定义指令。

本文介绍了ARMv7-M架构的基础特性,包括其Memory-mapped架构、系统级别的术语及操作模式等内容。文中详细阐述了Thread mode与Handler mode的区别,以及异常处理流程、优先级和返回机制。

本文介绍了ARMv7-M架构的基础特性,包括其Memory-mapped架构、系统级别的术语及操作模式等内容。文中详细阐述了Thread mode与Handler mode的区别,以及异常处理流程、优先级和返回机制。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?